# 科研費

# 科学研究費助成事業研究成果報告書

平成 30 年 6 月 13 日現在

機関番号: 16101

研究種目: 基盤研究(C)(一般)

研究期間: 2015~2017

課題番号: 15K00079

研究課題名(和文)3次元積層チップ間接続の異常遅延検出のための検査容易化回路設計手法の開発

研究課題名(英文)Design-for-testability circuit for detecting delay faults at interconnects in 3D stacked ICs

## 研究代表者

四柳 浩之 (Yotsuyanagi, Hiroyuki)

徳島大学・大学院社会産業理工学研究部(理工学域)・准教授

研究者番号:90304550

交付決定額(研究期間全体):(直接経費) 3,500,000円

研究成果の概要(和文):本研究では,3次元実装LSIにおける積層チップ間接続で発生する異常遅延の検査を行うための検査容易化設計手法を開発した。また,チップ積層間の接続に用いるシリコン貫通ビア(TSV)やマイクロバンプの欠陥による遅延について,電磁界シミュレーションおよび電子回路シミュレーションにより推定した。提案する検査容易化設計は,TSVに遅延付加セルを設け,異常遅延の検査を行うものである。遅延付加部の内部配線の影響を低減する配置方法についても検討した。試作ICの測定結果より付加遅延量のバラツキを抑える遅延付加ゲートの評価や複数TSVの同時検査可能な条件などを明らかにした。

研究成果の概要(英文): In this research, we propose design-for-testability circuits for testing delay fault occurred at interconnects in 3D stacked ICs. We also estimate the delay caused by defects in Through-Silicon-Via (TSV) or microbump used in interconnects using an electromagnetic simulator and a circuit simulator. The proposed design-for-testability circuit can detect delay faults by time-to-digital converter embedded in boundary scan design. The place and route method for reducing internal routing of TDC was also developed. We also fabricated some experimental ICs to evaluate delay gates which have small propagation delay variations and evaluate the feasibility of testing multiple TSVs simultaneously.

研究分野:計算機システム

キーワード: VLSIの検査技術 検査容易化設計 3次元積層チップ 遅延故障 LSIテスト ディペンダブル・コンピ

ューティング

## 1.研究開始当初の背景

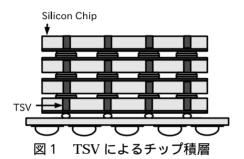

近年,集積回路の微細化の物理的限界が近づいており,従来とは異なる技術による高集積化として,複数の LSI チップを積層する 3次元実装 LSI の開発が進められている。 3次元実装 LSI では,図 1のようにチップ内に基板を貫くシリコン貫通ビア(TSV)を設け,TSV とマイクロバンプでチップ間を接続し,積層する。

3次元実装 LSI に固有のテストとして, チップ積層を行う前に TSV がチップ内に 正しく製造されたかを検査するプリボンド テストと,TSV を露出しマイクロバンプで チップ間を接続した後にそれらの接続が正 しく行われたかを検査するポストボンドテ ストの2種が存在する。チップ積層後のポ ストボンドテストに関しては,チップ間 続の静的な特性を検査する論理値テストが 主な対象となっており,信号遅延などの同 的な特性のテストが課題となっていた。

#### 2.研究の目的

本研究では,3次元実装LSIにおける積層チップでのチップ間接続で発生する異常遅延の検査を行うための検査容易化回路の設計手法を開発する。TSVおよびマイクロバンプの検査,特にそれらで発生する遅延故障の検査について,主に,(1)積層チップ間接続の遅延故障検査対象となる異常遅延量の推定,(2)積層チップ間接続の遅延故障検査容易化設計の開発および模擬IC試作による故障検出能力評価,(3)積層チップの接続配線に依存しない検査容易化設計の開発,の3つについて研究を行う。

## 3.研究の方法

提案する検査容易化設計手法は,チップ積層間の接続に用いるシリコン貫通ビア(TSV)やマイクロバンプに発生する欠陥を考慮し,TSVに遅延付加セルを設け,異常遅延の検査を行うものである。検査容易化設計に関する各課題についての研究方法を述べる。

## (1)積層チップ間接続の遅延故障検査対象と なる異常遅延量の推定

積層チップ間の TSV およびマイクロバンプで発生する欠陥に関して,電磁界シミュレーション・電子回路シミュレーションによる異常遅延量の検討と検査可能性の評価を行う。また,TSV と検査容易化回路間の配線,ゲー

トで起こる遅延量も含めた評価も行うため, レイアウト設計後の配置配線情報や,試作 IC の実測結果なども解析に用いる。

(2)積層チップ間接続の遅延故障検査容易化 設計の開発および模擬 IC 試作による故障検 出能力評価

遅延付加・検出回路をバウンダリスキャン 回路に埋め込む提案済みの検査容易化設計 手法を,積層チップ間の異常遅延検出に適用 するための条件を検討する。適用条件として は,遅延付加回路に使用する遅延付加ゲート の選択や,積層チップ間で制御信号を生成・ 伝達する手法の開発,複数 TSV の同時検査の ための検査容易化回路内の配線条件などの 検討が必要である。また,TSV を含むチップ 間接続を擬似抵抗などで模擬して IC 試作を 行い, 主に複数 TSV の検査条件とそれに伴う 検査時間などのコスト評価を行う。東京大学 大規模集積システム設計教育センター (VDEC) 提供の Synopsys 社, Cadence 社,MentorGraphics 社等の設計用 EDA ツール を設計に用い, Rohm 0.18um CMOS チップの 試作を行った。

(3)積層チップの接続配線に依存しない検査容易化設計の開発

TSV を通る遷移信号に遅延を付加する際に配線遅延の影響を考慮するとチップの入出力の順序が遅延付加に最適となるとは限らない。これらのことから,検査容易化回路内の遅延付加ゲートの接続順についての検討が必要である。本研究においては,チップの入出力配置と検査容易化回路内で使用する遅延付加・検出用のセルの配置・配線法の開発を行う。

#### 4.研究成果

各研究方法によって得られた成果は次のとおりである。各成果は研究期間中に3回設計した試作 IC の測定およびシミュレーションにより得られたものである。

(1)積層チップ間接続の遅延故障検査対象と なる異常遅延量の推定

電磁界シミュレーションによる解析から、マイクロバンプのみの断線については、その抵抗値が k オーダー以上とならなければ信号遅延への影響が軽微であること、また故障検出の際にはマイクロバンプ側からで接続であることで遅延検出がよりしやすいことで遅延検出がよりしやすいことが確認できた。 遅延付加セルの配置によら付加遅延量の増減を考慮するため、積層チルをがいる場所の入出力に付加順に接続、の2種の配線時の入出力ピン配置順に接続、の2種の配置配線を行い、シミュレーションにより伝搬遅延時間の差異を調査した。

(2)積層チップ間接続の遅延故障検査容易化 設計の開発および模擬 IC 試作による故障検 出能力評価

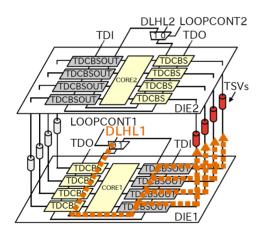

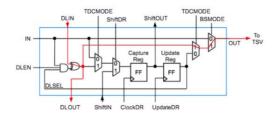

3次元実装 IC にも適用可能な検査容易化設計として,提案済の時間デジタル変換器(TDC)組込型バウンダリスキャン設計を図2の構成でチップ内に組み込んだ。チップ内のコア回路に依存せず遷移信号をTSVへ供給するために改良した図3の TDCBSOUT セルの設計を行った。 遅延観測を行う際の経路間やチップ間のばらつきの影響を低減する補正手法について検討した。補正により遅延付加用ゲート1段または2段の変化を異常と判定可能となり,高精度な検査が可能となった。

遅延付加用 XOR ゲートの設計改良により, 測定分解能が 15%程度向上し,面積削減も行 うことができた。 複数信号の同時検査に関 しては、IC内での遅延付加部の付加遅延量の ばらつきがゲート換算で約1/10程度存在し また観測する2経路と遅延付加部の接続箇 所が近い場合に,遷移信号が干渉して観測不 能となることを確認した。 複数経路の同時 検査時に観測する信号遷移の消滅を防ぐた め,0から1,1から0の遷移での付加遅延 量の差の少ないデュアルパストランジスタ 型の XOR ゲート遅延付加ゲートを設計し,試 作 IC に実装した。 遅延付加部制御回路を 組込んだ IC を設計,試作し,実測による動 作検証と遅延分解能の調査を行った。制御信 号を外部から与える以前の試作 IC と比較し,

図2 TDC 組込型バウンダリスキャン回路の 3次元実装 IC への適用

図3 TDCBSOUT セル

同等の分解能を持つことを確認した。 遅延付加回路を内蔵するバウンダリスキャン設計において,遷移信号印加専用のセルを不要とし,従来のバウンダリスキャン設計での標準モードのみで TSV を検査するための制御回路を設計した。

(3)積層チップの接続配線に依存しない検査容易化設計の開発

遅延付加部の検査容易化セルをスタンダードセル化し、配置配線を行い、試作 IC内に実装した。 提案する検査容易化設計を実装する際のチップレイアウトに関して、遅延付加部の内部ゲート間の配線長を削減する設計手法を提案した。遅延付加ゲート間の距離を抑える配置変更により以前の配置配線結果より遅延時間の平均値・標準偏差を抑えることができた。

## 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [学会発表](計22件)

平井 智士, 四柳 浩之, 橋爪 正樹: TDC 組込み型バウンダリスキャンにおける遅延付加部のリオーダによる配線長の低減,電子情報通信学会技術研究報告, Vol.117, No.444, 13-18, 2018年2月 Satoshi Hirai, Hiroyuki Yotsuyanagi and Masaki Hashizume: Reordering Delay Elements in Boundary Scan Circuit with Embedded TDC, the 18th IEEE Workshop on RTL and High Level Testing, Taipei, Dec. 2017.

谷口 公貴, 四柳 浩之, 橋爪 正樹: 試作した遅延故障検査容易化回路による2 経路同時検査について,第64回機能集 積情報システム研究会,2017年10月. 柴田 駿介, 四柳 浩之, 橋爪 正樹:3 次元実装 IC におけるマイクロバンプ欠 損時の遅延解析,第64回機能集積情報システム研究会,2017年10月.

新開 颯馬, 四柳 浩之, 橋爪 正樹: 遅延故障検査容易化設計のための遅延付加ゲートの設計, 第 64 回機能集積情報システム研究会, 2017 年 10 月.

河塚 信吾, <u>四柳 浩之</u>, 橋爪 正樹: TDC 組込み型スキャン FF の微小遅延故障 検出能力評価, DA シンポジウム 2017, 21-26, 2017 年 8 月.

河口 巧, 四柳 浩之, 橋爪 正樹: TSV 検査のための TDC 組込み型バウンダリス キャン制御回路の設計, DA シンポジウム 2017, 15-20, 2017 年 8 月.

Satoshi Hirai, <u>Hiroyuki Yotsuyanagi</u> and Masaki Hashizume: On design for reducing delay variation in design-for-testability circuit for delay fault, 2017 Taiwan and Japan

Conference on Circuits and Systems, Aug. 2017.

河塚 信吾, <u>四柳 浩之</u>, 橋爪 正樹: 微小遅延故障テストのための TDC 組込み型スキャン FF の設計について, 電子情報通信学会技術研究報告, Vol.116, No.331, 105-110, 2016 年 11 月.

Takumi Kawaguchi, <u>Hiroyuki</u> Yotsuyanagi and Masaki Hashizume: On Control Circuit and Observation Conditions for Testing Multiple TSVs Using Boundary Scan Circuit with Embedded TDC, Proc. of the 17th IEEE Workshop on RTL and High Level Testing, 1-3-1-1-3-6, Hiroshima, Nov. 2016. 森 亮介, 四柳 浩之, 橋爪 正樹: TDC 組込み型バウンダリスキャンを用いる遅延故障検査でのチップ間ばらつき補正,電気関係学会四国支部連合大会講演論文集,96,2016年9月.

森 亮介, 四柳 浩之, 橋爪 正樹: 遅延 故障検査容易化回路を用いる同時検査対 象経路選択条件の検討, 電子情報通信学 会技術研究報告, Vol.115, No.339, 25-30, 2015年12月.

濱田 圭吾, 四柳 浩之, 橋爪 正樹: 遅延故障用バウンダリスキャンによる TSV 検査法に関する研究,電気関係学会四国支部連合大会講演論文集,111,2015年9月.

宮本 陽平, 四柳 浩之, 橋爪 正樹: TSV 故障検出回路における VDL 回路部の遅延検出能力評価, 電気関係学会四国支部連合大会講演論文集, 112, 2015 年9月.

石場 隆之, 四柳 浩之, 橋爪 正樹:微小遅延故障検査用遅延測定回路内の遅延付加部の改良, 電気関係学会四国支部連合大会講演論文集, 117, 2015年9月. 森 亮介, 四柳 浩之, 橋爪 正樹: TDC 組込み型バウンダリスキャンを用いた 2 経路同時遅延測定の実測による評価, 電気関係学会四国支部連合大会講演論文集, 118, 2015年9月.

Hiroyuki Yotsuyanagi, Akihiro Fujiwara and Masaki Hashizume: On TSV Array Defect Detection Method Using Two Ring-oscillators Considering Signal Transitions at Adjacent TSVs, Proc. of IEEE 3D System Integration Conference 2015, TS8.24.1-TS8.24.4, Sep. 2015.

## 6.研究組織

## (1)研究代表者

四柳 浩之 (Yotsuyanagi Hiroyuki) 徳島大学・大学院社会産業理工学研究部理 工学域・准教授

研究者番号:90304550