# 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 9 日現在

機関番号: 32689

研究種目: 基盤研究(C)(一般)

研究期間: 2015~2017

課題番号: 15K06036

研究課題名(和文)ロバスト超低電圧回路設計技術に関する研究

研究課題名(英文) Robust ultra-low voltage LSI design technology

#### 研究代表者

柳澤 政生 (Yanagisawa, Masao)

早稲田大学・理工学術院・教授

研究者番号:30170781

交付決定額(研究期間全体):(直接経費) 3,800,000円

研究成果の概要(和文):本研究では「ムダを省き"頑張って"動く、"それなりに"動く」LSIを実現することを目的に、ロバストな超低電圧回路による超低エネルギーLSI、ならびに、ソフトエラー耐性をもったLSIを設計した。前者においては、インバータ回路を使用してリーク電力を低減するバルク型の回路ならびにFinFET型の回路を提案し、約15~30%のリーク電力を削減できることを示した。後者においては、低電力な耐ソフトエラーラッチであるNew-SEHラッチ、Fast-SEHラッチ、ならびに、SHC ラッチの提案を行い、電力削減、遅延削減を達成した。

研究成果の概要(英文): As semiconductor technology continues scaling down, the reliability issue has become much more critical than ever before. Robust ultra-low voltage LSIs are presented in this research. Bulk-type circuit and FinFET-type circuit are developed. Experimental results show they reduce leak power by 15-30%. Unlike traditional hard-errors caused by permanent physical damage which can't be recovered in field, soft errors are caused by radiation or voltage/current fluctuations that lead to transient changes on internal node states, thus they can be viewed as temporary errors. However, due to the unpredictable occurrence of soft errors, it is desirable to develop soft error tolerant designs. In this research, low-power soft error tolerant New-SHE latch, Fast-SEH latch, and SHC latch is proposed. In case of SHC latch, 80.52% power reduction at maximum is achieved compared with FERST latch.

研究分野: 工学

キーワード: ロバスト 低電圧回路 低消費電力回路 LSI設計 ソフトエラー耐性

#### 1. 研究開始当初の背景

近年、スマートフォンを始め、タブレットやセンサネット並びに健康等のアプリケーションの携帯性を必要とする情報機器の発展拡大に伴い、情報機器のエネルギー消費量の増加が懸念されている。そのため、情報通信の中心的役割を担うLSIにおいて消費エネルギーを劇的に削減することは喫緊の課題であり、地球規模的なグリーン・イノベーションの意味で情報通信産業の急務とも言える。

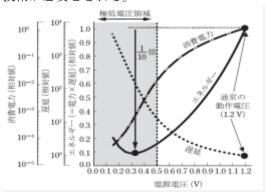

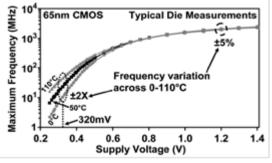

LSI 回路の低消費電力化には、電源電圧を 下げることが最も効果的である。CMOS回路 の動作電力は電圧の自乗に比例するので、例 えば電源電圧を 1.2V から 0.3V に下げると 消費電力が約3桁減少するが、遅延が約2桁 増加するので、消費電力と遅延をかけたエネ ルギーは約 1/10 になる(図1参照)[1]。し かし、半導体プロセスの微細化に伴って電源 電圧の低電圧化を進めると遅延・リーク電力 の増大や PVT (Process / Voltage / Temperature) ばらつきなど様々な問題に直 面する。特に、I)電源電圧の低下に伴い、回 路の動作周波数は指数関数的に減少する(図 1参照)。この結果、漏れエネルギーが低電 圧領域(特にサブスレッショルド領域:電源電 圧はトランジスタの閾値電圧以下の領域)で は劇的に増加する。結果として見込み通りの 低電圧によるエネルギー削減の効果が得ら れるとは限らない; II)低電圧の条件下では、 CMOS 回路の動作が不安定となり、LSI の PVT ばらつきに影響され(図 2 参照) [2]、誤 動作が極めて増大する。どうにかこれを克服 するような新たなロバストな低電圧LSI設計 技術が必要とされる。

図 1: エネルギーの電源電圧依存性の一例 [1].

図 2: 電源電圧による周波数ばらつき [2].

これらの背景から、10年後のスマート社会 に向け超低エネルギー情報通信機器構築の ための本質は、以下の技術開発が生命線を握 る:(A)低電圧動作による LSI の消費電力量 を更に1 桁削減する。(B) 低電圧回路におい て、製造・電圧・温度ばらつき(PVT ばらつ き)等に変動があっても、正しく動作する。 サブスレッショルド回路の高速化設計技 術の一つとして、スーパーパイプライン手法 [3] が知られている。スーパーパイプライン では、パイプラインレジスタを積極的に増や すことで、低電圧動作における性能と、エネ ルギー効率をともに向上させた。この手法で は、最適パイプライン化により毎クロックの ステージ遅延が短縮されるため、リークエネ ルギー消費を抑え、全体の消費エネルギーを 削減することが可能である。しかし、スーパ ーパイプラインは、温度の変動によるばらつ きに対応しておらず、結果として PVT ばら つきがあっても確実に正常に動作するよう な "always correct" 動作を保証するために、 設計時には大きなマージンを要し、見込み通 りの低エネルギー化の効果が得られるとは 限らない。もう一方、PVTばらつき耐性に関 して、これまで Intel [4]、Michigan 大学 [5]、 または大阪大学 [6] の研究グループなどが 「動的タイミングエラー検出・回復手法」の 研究を行われている。「動的タイミングエラ 一検出・回復手法」は、ばらつきに対し、常 に回路が正しく動作しているかをチェック する回路を設計し、その個体/そのときの動作 における、実際の遅延に基づき、動的にタイ ミングエラー検出・回復動作を行う。しかし、 既存研究はいずれも、タイミングエラーを事 後、すなわちタイミングエラーが起きた後に 検出しており、発生したエラーを回復するた めに極めて大きなオーバヘッドを要する。

LSI(大規模集積回路)の信頼性における 重要な問題の1つとして、放射線起因のソフ トエラーが挙げられる。高エネルギー粒子が 回路に衝突すると、エネルギーを失い、電子 正孔対が生成する。過剰キャリアである電子 は N 拡散領域、正孔は P 拡散領域へと収集 される。収集された電荷がノードの臨界電荷 量を上回った場合、状態が反転し、ソフトエ ラーが発生する。つまり、PMOS と NMOS において、データは一方向にしか反転しない。 ソフトエラーは一時的な故障のため、回路構 造の工夫等で回復することができるが、間違 った値をラッチした場合、回路に重大な障害 が生じる。従来の耐ソフトエラー技術よりも 高い耐性をもち、低消費電力・小面積・高速 な LSI 設計技術の開発が求められている。

#### 2. 研究の目的

本研究では、LSI の設計技術、即ち「LSI の作り方」に焦点を当て、「ムダを省き"頑張って"動く、"それなりに"動く」を実現することを目的に、ロバストな超低電圧回路による超低エネルギーLSI、ならびに、ソフ

トエラー耐性をもったにLSIを中心とした研究開発を遂行する。既存LSI設計技術の問題点を解決する革新的技術として「I: MOSトランジスタの調整による超低電圧回路高速化設計技術」と「II: ソフトエラー耐性をもつ低消費電力・小面積・高速回路設計技術」を提案する。そしてI)の結果として、CMOS回路中の電圧低減に影響しやすい NMOSトランジスタの Size を調整による回路全体の高速化が可能となる。さらに、II)の結果として、従来の耐ソフトエラー技術よりも高い耐性をもち、低消費電力・小面積・高速な回路設計基盤技術を開発する。

本研究提案を用いれば、1) 低電圧回路動 作速度低下問題を緩和することができ、更に 漏れエネルギーを削減することが可能とな る。結果として、将来的に低電圧による最大 1 桁以上電力削減を可能とした超々低エネル ギー化システムLSI設計が期待できるものと 考える。2) 既存のソフトエラー検出・回復 手法のように回路の最終的な処理結果を事 後解析することと異なり、回路自身が自分で ソフトエラーに対して耐性を持ち、エラーが 生じても自身で訂正することが可能となる。 提案技術は、低電圧回路のばらつき問題を緩 和する技術を提供するもので、今後、電機メ ーカ・半導体メーカがこの技術を用いること でワーストケース設計をとることをせず、テ ィピカルケース設計に移行できることを示 唆する。さらに、ソフトエラー耐性も持ち合 わせるので、相当にロバストな回路を実現さ せることが可能となり、今後の LSI 設計技術 に大きな変革点をもたらすと考える。

#### 3. 研究の方法

まず、研究計画全体の基礎となる研究項目 (I) 超低電圧回路設計技術の研究開発を実 施する。本研究の予備研究として、通常定格 電圧(1.2V) で伝搬遅延が同一になるように 設計されている CMOS 素子のトランジスタレ ベルシミュレーションを行った。通常定格電 圧で動作させるために設計しているインバ ータを低電圧領域(特にサブスレッショルド 領域)で動作させると NMOS の方が PMOS より 遅延が増加する (Vdd = 0.2V の時、NMOS は PMOS より 4 倍もの遅延時間が発生する結果 となる)。この結果による、CMOS 回路中の電 圧低減に影響しやすい NMOS トランジスタの Size を調整すれば、サブスレッショルド領域 で動作する CMOS 回路全体の高速化が可能と なると考える。

本研究ではまずサブスレッショルド電圧で動作する回路の概要と課題、課題の対処例について考察する。そして、対処例の1つである DTMOS のレイアウト設計を行い、DTMOSの課題であるウェルを追加した際の面積や寄生成分について影響を評価し指摘する。さらに DTMOS を FinFET へ適用してサブスレッショルド領域における動作についてインバータ回路を用いて評価する。そしてサブスレ

ッショルド電圧を用いたリーク電力を削減 するインバータ回路について、提案、実装し、 既存手法と比較・考察を行う。

つぎに、研究項目(II)ソフトエラー耐性をもの低消費電力・小面積・高速回路設計技術の研究開発を実施する。従来の耐ソフトエラー技術の1つとして、小松らによって提案された SHE(Soft Error Hardened)ラッチ補をして、小松らによって提挙が挙げられる。SEH ラッチは2つのデータ補エノードで構成される。1つのノードでエラーが起きた場合は他の2つのノードのデータをられぞれ参照することによって、エラーからしれぞれ参照することによって、エラーからしない性質を利用し、データ補正ノードをそれぞれ PMOS と NMOS ではソフトエラーはフトエラー耐性を実現している。

本研究では、まず、SEH ラッチを改良する ことにより、低消費電力で、小面積な、かつ、 高速な(遅延時間の短い)ソフトエラー耐性 を持ち合わせたラッチを開発することを考 える。ソフトエラーの発生原因を利用したも のや多重化を行うものなど、様々な耐性手法 が提案されてきた。C-element を使用した耐 性技術としては、TFH ラッチや FERST ラッチ、 HiPeR ラッチ等が挙げられる。しかし、従来 の技術は回復できるノードに制限があるこ とや、多重化による電力オーバーヘッドが大 きいこと等の問題が挙げられる。以上より、 低電力かつどのノードでエラーが発生して も回復できるラッチの設計技術の開発が急 務であるといえる。本研究では、つぎに、 C-element を使用し、低電力化を目指した耐 ソフトエラーラッチである SHC ラッチを開 発することを考える。

## 4. 研究成果

(I) 超低電圧回路設計技術の研究に関して 記述する。これまでのサブスレッショルド電 圧で動作する回路の問題はサブスレッショ ルドリークが課題となっていた。待機時の長 い機器にとっては深く関わる問題であり、改 善することが求められている。そこでインバ ータ回路を使用してリーク電力を低減する バルク型の回路ならびに FinFET 型の回路を 提案した。VDD、VSSの間に新たにNMOSとPMOS を追加することで OFF 状態であるインバータ の NMOS と PMOS に流れるリークを遮断して回 路全体のリーク電力を抑制する手法である。 バルク型の回路では各ボディ端子を NMOS (MO) は VDD に、PMOS (M1) は MO のソース端 子に、NMOS (M2)、PMOS (M3)はVSSに接続す る。FinFET 型の回路では全てのボディ端子を ゲート端子と短絡する。使用したライブラリ は、バルク型はローム社の 180nm、FinFET 型 はPTM-MGの15nmのライブラリである。バル ク型はチャネル幅の比は外側(MO, M3)と内側 (M1, M2)で2:1, FinFET型は3:1程度、加え て tfin (Fin の厚み)の値を通常の 2.9 倍の

大きさにした。提案回路の遅延時間及びリーク電力を HSPICE シミュレーションを使用して測定した。 バルク型のリーク電力は Vdd=0.3 [V] 付近がリーク電力の極小点になった。それ以下の電源電圧においては MO とM3 のトランジスタにおけるサブスレッショルドリーク電流が増加した事が要因と考にいてく傾向だが、それ以降はほぼ一定の値であった。2つの MOS でできた従来のインバータと比較すると、バルク型、FinFET 型は約15~30%のリーク電力を削減できることが分かった。また、バルク型は3~4桁、FinFET型は20~35%の遅延時間のオーバーヘッドが発生することも分かった。

(II) ソフトエラー耐性をもつ低消費電力・ 小面積・高速回路設計技術の研究に関して記 述する。ソフトエラーによる信頼性の低下を 防ぐ LSI 設計に焦点を当てて研究を行った。 従来、DICE やフリップフロップの多様化とい った耐ソフトエラー技術が提案されてきた が、消費電力が増加する、回路面積が増える 等の問題点が生じており、低電力で高耐性を もつLSI設計技術の開発が急務となっている。 本研究では、SEH ラッチを改良することによ り、低電力な耐ソフトエラーラッチである New-SEH ラッチを提案し、NCSU15nm の PDK (Process Design Ki) を用い、実装・評価を 行った。従来の SEH ラッチと比較し、消費電 力を 46%削減、トランジスタを 25%削減可 能なことをシミュレーション実験によって 示した。ただ、このラッチは遅延オーバーへ ッドが大きいものであった。そこで、さらに 優れた耐ソフトエラーラッチを検討した。そ の結果、New-SEH ラッチをさらに改良するこ とにより高速化を目指した Fast-SEH ラッチ を提案した。シミュレーション実験によって、 Fast-SEH ラッチは SEH ラッチと比較して、最 大で 10.91%の電力削減、55.17%の遅延削減 することを示した。また、C-element を使用 し、低電力化を目指した耐ソフトエラーラッ チである SHC ラッチの提案を行った。SHC ラ ッチと既存の耐ソフトエラーラッチを実装 し、spice シミュレーション・評価を行った 結果、SHC ラッチ は HiPeR ラッチと比較し、 最大で80.52%の電力削減を達成した。また、 改良 SHC ラッチは FERST ラッチと比較し、 最大で66.04%の遅延削減を達成した。

### <引用文献>

[1] 高宮真, 篠原尋史, 桜井貴康, "低電圧動作限界に挑戦する極低消費電力 LSI 回路技術の最新動向,"電子情報通信学会誌, vol. 95, no. 11, pp. 974-978, 2012.

[2] H. Kaul et.al, "A 320 mV 56  $\mu$  W411 GOPS/Watt Ultra-Low Voltage Motion Estimation Accelerator in 65 nm CMOS," IEEE Journal of Solid-State Circuits, vol. 44, no. 1, pp. 107-114, 2009.

[3] M. Seok et.al, "A 0.27V 30MHz

17.7nJ/transform 1024-pt complex FFT core with super-pipelining," IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 342-344, 2011.

[4] S. Das et.al, "A self-tuning DVS processor using delay-error detection and correction," IEEE Journal of Solid-State Circuits, vol.41, no.4, pp. 792 - 804, 2004.

[5] K. Bowman et.al, "Energy-efficient and metastability-immune resilient circuits for dynamic variation tolerance," IEEE Journal of Solid-State Circuits, vol. 44, no.1, pp. 49-63, 2009. [6] H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye, "Adaptive performance compensation with in-situ timing error predictive sensors for subthreshold circuits," IEEE Transactions on VLSI Systems, vol. 20, no. 2, pp. 333-343, 2012.

## 5. 主な発表論文等

〔学会発表〕(計 5件)

- ① Saki Tajima, Nozomu Togawa, <u>Masao</u>

<u>Yanagisawa</u>, and Youhua Shi, "Soft

error tolerant latch designs with low

power consumption (invited paper),"

IEEE 12th International Conference on

ASIC (ASICON 2017), October 25-28,

2017, Guiyang, China

- ② 田島咲季,戸川望,柳澤政生,史又華, "C-element を用いたソフトエラー耐性 をもつ SHC ラッチの設計," 電子情報通 信学会 回路とシステムワークショップ 論文誌,2017年5月11~12日,福岡県 北九州市.

- ③ 田島咲季, 史又華, 戸川望, <u>柳澤政生</u>, "高速かつ低電力なソフトエラー耐性を もつ Fast-SEH ラッチの設計," 電子情 報通信学会 回路とシステムワークショ ップ論文誌, 2016 年 5 月 13 日, 福岡県 北九州市.

- ④ 田島咲季, 史又華, 戸川望, <u>柳澤政生</u>, "15nmプロセスにおける低電力な耐ソフトエラーラッチの設計," 電子情報通信 学会 VLSI 設計技術研究会(デザインガイヤ), 2015年12月2日, 長崎県長崎市.

- (5) Saki Tajima, Youhua Shi, Nozomu Togawa, and <u>Masao Yanagisawa</u>, "A low-power soft error tolerant latch scheme," the 11th International Conference on ASIC (ASICON 2015), November 4, 2015, Chengdu, China.

### 6. 研究組織

(1)研究代表者

柳澤 政生(YANAGISAWA, Masao) 早稲田大学・理工学術院・教授 研究者番号:30170781