# 科学研究費助成事業 研究成果報告書

令和 元年 5月30日現在

機関番号: 13901

研究種目: 基盤研究(B)(一般)

研究期間: 2016~2018

課題番号: 16H02800

研究課題名(和文)マルチ・メニーコア向け高並列組み込み制御システム設計・実装手法の研究

研究課題名(英文)Design and Implementation for Parallelization of Embedded Control Systems on Multi- and Many-Core Processors

研究代表者

枝廣 正人 (Edahiro, Masato)

名古屋大学・情報学研究科・教授

研究者番号:50578854

交付決定額(研究期間全体):(直接経費) 13,200,000円

研究成果の概要(和文):一つの半導体チップに複数のプロセッサを搭載するマルチ・メニーコアプロセッサ (以下,マルチコア)向け高並列組込み制御システム設計・実装手法の確立を目的とし,以下の4項目を実現した.(ア)高並列化を実現する制御アルゴリズムを確立,(イ)マルチコア活用を目指す制御設計とソフトウェア実装を統合するクロスレイヤ設計手法を確立し,車載制御を意識した実際の環境において実証,(ウ)モデルベース並列化における最大実行時間最小化手法を提案,(エ)PCを用いた組込み制御高速シミュレーション手法を提案.

研究成果の学術的意義や社会的意義

研究成果の子術的意義や社会的意義 IoT社会においては高性能制御を機器に組み込むニーズが増大するが,機器内では電力制約によりプロセッサ動作周波数を上げることができず,マルチコアプロセッサによる高性能化に期待が高まっている.この実現には制御ソフトウェアの並列化が必須であるが,従来の制御アルゴリズムは並列化が困難であり,マルチコアを有効に利用することができなかった.本研究において実現した,制御アルゴリズム,制御-実装協調設計手法および設計自動化技術は,マルチコア向け組込み制御ソフトウェアの設計生産性向上を可能にする.

研究成果の概要(英文): In this research, in order to establish a highly parallel embedded control system design and implementation method for the multi-many-core processor that mounts multiple processors on one semiconductor chip, we made four achievement: (a) established a control algorithm to realize high parallelism, (b) established a cross-layer design method, which is a co-design method between control and parallel software design, aiming at higher multi-core utilization, and demonstrated it in an actual environment with awareness of vehicle control, (c) proposed a method for minimizing the maximum execution time in parallelization for model-based development, and (d) proposed a method for high-speed embedded control simulation using PCs.

研究分野: 組込みシステム向け並列化設計技術および組合せ最適化

キーワード: 組込みシステム 制御システム マルチコア 並列化 シミュレーション

## 様 式 C-19、F-19-1、Z-19、CK-19(共通)

## 1.研究開始当初の背景

今後ますます複雑で高精度な制御が要求され計算性能向上が必須である.一方半導体の微細化限界により今後の計算性能向上は並列化に依るところが大きい.この問題に対しては国内外で多くの研究が進められており,例えば制御設計の結果である逐次プログラムを自動並列化コンパイラにより並列化する手法が知られている[A]が,1)もとの制御アルゴリズムに抽出可能な並列性が少ない,2)制御設計段階において並列実行について考慮されない,3)実装における並列実行状況が制御設計にフィードバックされない,といった理由により計算性能向上が難しいのが現状である.

[A] 梅田他, モデルベース設計により自動生成されたエンジン制御 C コードのマルチコア用自動並列化, 情報処理学会組込みシステムシンポジウム(20), 2013.

#### 2.研究の目的

上記のような背景をふまえ,マルチコア向け高並列組込み制御システム設計・実装手法の確立を目的とした.具体的には,高精度制御をマルチコア上に効率よく実装するため,従来扱われてこなかった,並列に向いた制御アルゴリズム設計,制御設計とソフトウェア実装の統合,制御アルゴリズムの並列実装自動化を目的とした.

#### 3.研究の方法

本研究においては上記目的の下,(ア)高並列化を実現する制御アルゴリズム,(イ)マルチコア活用を目指す制御設計とソフトウェア実装を統合するクロスレイヤ設計手法,(ウ)モデルベース並列化における最大実行時間最小化手法,(エ)PCを用いた組込み制御高速シミュレーション手法について研究した.

なお,当初は(ウ)(工)の研究に関して実施する予定はなく,並列化モデルからソフトウェアコンポーネントを抽出し,並列実装する研究を実施予定であったが,その後の調査において[B]のような研究が進んでいることがわかり,予定を変更した.

[B] Maximilian Hempe, A Model-based Approach for Conditioning Software to Multi-Core using AUTOSAR. 9th AUTOSAR Open Conference in Gothenburg, 2016.

#### 4. 研究成果

(ア)高並列化を実現する制御アルゴリズム

本研究テーマは,研究開始当初の背景における課題「1)もとの制御アルゴリズムに抽出可能な並列性が少ない」に対応するものである.

制御工学分野では、対象を数理モデル化し、それに依存して制御を実現する.しかしハイエンド制御、例えば高出力・トルク密度を目指す自動車向けモータのような制御対象では、複雑な非線形性を持ち 動的に変動するため 高精度の数理モデル化は極めて困難になりつつある.今後の性能向上のためには、数理モデルへの依存性が高く、逐次性の強い現在の制御アルゴリズムから、計算機資源を積極的に活用する、すなわち並列化に向いた制御アルゴリズムに転換する必要がある.非線形性を持ち、動的変動するような制御対象にも適用可能で、並列化可能な制御アルゴリズムとしてモデル予測制御が知られているが、計算量が膨大で、単純な並列化では組込み機器への適用が難しいという課題があった.

これに対し本研究では,永久磁石同期モータ向けベクトル制御を題材とし,並列化および AI 手法(ニューラルネットワーク)の適用を進めた.結果として,もとのモデル予測制御アルゴリズムの並列化により,パソコン等に用いられる汎用プロセッサ 12 台で約 10 倍の性能向上を実現,逐次 AI 手法の適用により約 3700 倍の並列化を実現した.しかしながら,実際の自動車に適用するためには,さらに 100 倍~1000 倍の性能向上が必要であり,グラフィックスプロセッサ(GPU)等を用いた AI 手法の並列化が今後の課題である.

(イ)マルチコア活用を目指す制御設計とソフトウェア実装を統合するクロスレイヤ設計手法本研究テーマは,研究開始当初の背景における課題「2)制御設計段階において並列実行について考慮されない,3)実装における並列実行状況が制御設計にフィードバックされない」に対応するものである.

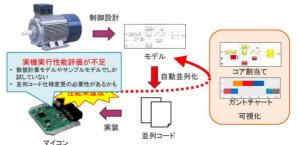

現在,車載制御を始めとしてモデルベース開発(MBD)が主流となりつつある.MBD におい

ては , 制御設計では Mathworks 社の MATLAB/Simulink 等のツールを用いて モデル (右図中央上方のブロック線図)を記述し , 実装設計ではモデルから自動生成 された逐次コードを利用してマルチコア 向けに並列化実装する . その際 , 制御設計と実装設計が分離しているため , 現状で上述の 2) , 3)の問題が起こっている . この問題を解決するため , 我々はモデル設計と並列化を協調させるクロスレイヤ設計の概念を提案し , 本研究で実証した .

モデル設計と並列化を協調させる

具体的には、ソフトウェアのためのハードウェア抽象化記述 SHIM [C]を用いてマイコンのアーキテクチャ・性能情報をモデルレベルで利用可能とした.そして、SHIM の情報を用いてモデルのレベルで並列化を行い、性能見積を行った(上図の右端のコア割当および可視化).このことにより、制御設計段階において並列実行について考慮することができ、かつ、実装における並列実行状況を制御設計にフィードバックすることが可能となった.

実証のため,a) 車載向けマルチコアマイコンであるルネサス エレクトロニクス社 RH850/F1H(2コア)に AUTOSAR 仕様 OS TOPPERS ATK2 を搭載し,車載を意識した実証環境を構築し,b) プラシレスモータを制御対象とし,モデルベース開発用に車載モータ向けセンサレス制御アルゴリズムをモデル設計し,提案するクロスレイヤ設計により実証環境上で並列動作させた.その結果,図の右端のコア割当および可視化情報を用い,制御設計者と実装設計者が性能向上について協調設計開発可能となることがわかり,最終的に2コアで約1.7倍の高速化を実現した.実証環境については下記「その他」成果の動画 として公開している.

現状では,モデル設計が完了し,制御設計者の手を離れた後,実装設計者が逐次コードをマルチコアマイコン上に並列実装して性能状況を解析している.また,実装段階のコードレベルではモデル上のボトルネック箇所がわかりにくい状況である.そのため,並列化実装は数か月を要している作業である.本研究で提案するクロスレイヤ設計により,モデルレベルでモデルの並列化状況および並列実行状況を可視化でき,制御設計者と実装設計者が同時に確認して協調設計できるようになった.さらに,与えられたモデルから並列化コードを自動生成できるようになったため,大幅に生産性を向上させることが可能となり,並列化設計期間を 10 分の 1以下にできる可能性があることを示した.

また,これらの成果ソフトウェアについては一部オープンソース化した(下記[その他]成果のオープンソースソフトウェア , ).

[C] Multicore Association, Software-Hardware Interface for Multi-many-core (SHIM), https://www.multicore-association.org/workgroup/shim.php

#### (ウ) モデルベース並列化における最大実行時間最小化手法

本研究テーマは,研究の方法で述べたように当初は実施予定ではなかったが,並列化性能を向上させるため,研究項目として追加した.

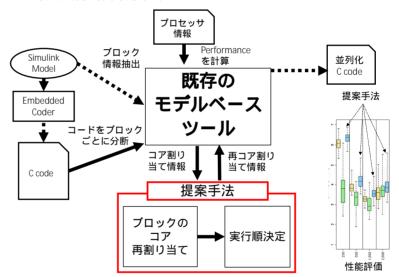

右図に示すとおり、本研究項目では、既存ツールの割当結果を利用して再配置を実現する・モデーを実現する・モデーをでいるが、既存ツール(Embedded Coder)を利して逐次のコードを生成している。既存モデルとしているが、モデルとで、アコード及び、各プロセ

ッサの情報を利用することで、並列化コードを生成している.既存手法では、コア配置のアルゴリズムにヒューリスティック手法を用いているため、一部最適なコア配置でない結果になっているところがある.本研究項目では、この問題を解決するために、ボトルネックになっている箇所のモデルの再配置及び、実行順序を変更することで、最大実行時間の最小化を実現する.提案手法では、クリティカルパス(最も処理に時間がかかるパス)を分析し、クリティカルパスと同じコアで処理しているモデルを、処理量の少ないコアに再配置を行う.この際、通信遅延も考慮し、なるべく再配置によって通信遅延が増えないように再配置を行う.図右側のグラフに示すとおり、提案手法が既存研究より性能が向上(グラフが高い方が性能が良い)していることが分かる.

#### (エ)PC を用いた組込み制御高速シミュレーション手法

本研究テーマも、研究の方法で述べたように当初は実施予定ではなかったが、性能見積の高速化および精度向上を目的として、研究項目として追加した。

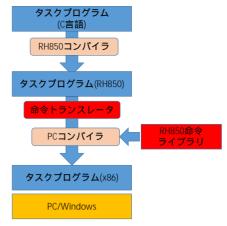

このシミュレーション環境を実現するために,a)ターゲットプログラムの命令をアセンブラレベルでホストマシン上のシミュレーション実行する関数に変換する機能,b)ターゲット CPU 命令をシミュレーション実行する機能,c)ターゲットシステムでの実行時間を経過させる機能を実現した.本 CPU シミュレータを使って,(イ)で開発したブラシレスモータ制御モデルを実行させた.a)とb)の命令変換機能のターゲットマシンにはルネサス エレクトロニクス社製プロセッサ RH850 を用い,特権命令を除く命令を実現した.従来 CPU シミュレータで実行されてい

ュレーショ ソ機能ること 現すが考えられる.

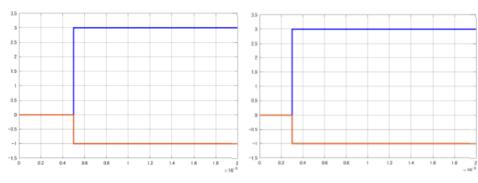

## 単一コアでの実行

2コアでの実行

## 5. 主な発表論文等

〔雑誌論文〕(計2件)

Zhaoqian Zhong and <u>Masato Edahiro</u>, "Model-Based Parallelizer for Embedded Control Systems on Single-ISA Heterogeneous Multicore," INTERNATIONAL JOURNAL OF COMPUTERS & TECHNOLOGY, 查読有, Vol. 19, 2019, 7470-7484.

DOI: https://doi.org/10.24297/ijct.v19i0.8123

鍾兆前, <u>枝廣正人</u>, "組込み制御システムに対するマルチコア向けモデルレベル自動並列化手法,"情報処理学会論文誌,査読有,59巻,2018,735-747.

https://ipsj.ixsq.nii.ac.jp/ej/?action=repository\_uri&item\_id=185884

## [学会発表](計18件)

Zhaoqian Zhong and <u>Masato Edahiro</u>, "Model-Based Parallelizer for Embedded Control Systems on Single-ISA Heterogeneous Multicore Processors," 2018 International SoC Design Conference (ISOCC), Nov. 2018.

<u>Yukikazu Nakamoto</u>, Daichi Minami, Shota Shiba, Yoshitaka Koga, and Koji Fukuoka, "A Simulation Environment of Embedded Control Systems for Multi-core Processors," 2018 IEEE Conferences on Internet of Things, Green Computing and Communications, Cyber, Physical and Social Computing, Smart Data, Blockchain, Computer and Information Technology, Congress on Cybermatics, Aug. 2018.

Sasuga Kojima, <u>Masato Edahiro</u>, and <u>Takuya Azumi</u>, "Remapping Method to Minimize Makespan of Simulink Model for Embedded Multi-core Systems," International Conference on Computers and Their Applications (CATA), March 2018.

<u>枝廣正人</u>, "MBP(モデルベース並列化)を用いたクロスレイヤ設計",組込みマルチコアサミット 2017,招待,2017 年 11 月.

Sasuga Kojima, <u>Masato Edahiro</u>, and <u>Takuya Azumi</u>, "Improving Core Allocation of Simulink Model for Embedded Multi-core Systems," IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), Aug. 2017. 竹松慎弥, 鍾兆前, 井上雅理, 横山静香, 小島流石, 近藤真己, 中本幸一, 安積卓也, 道木慎二, 本田晋也, 枝廣正人, "モデルベース開発におけるクロスレイヤ設計手法のマルチコア上モータ制御実装への適用," 情報処理学会組込みシステムシンポジウム 2017, 2017 年 8 月. Shunsuke Hori and <u>Takuya Azumi</u>, "Extended Mapping Algorithm Based on Modularity from Synchronous Block Diagrams to AUTOSAR Runnables," 2016 IEEE 21st International Conference on Emerging Technologies and Factory Automation (ETFA), Sept. 2016.

[図書](0件)

[ 産業財産権](0件)

[その他]

## 公開動画

「モデルベース開発から TOPPERS 搭載システムへのクロスレイヤ自動設計を利用したマルチコアモータ制御実装」https://youtu.be/eszVE9wc\_\_c

オープンソースソフトウェア

モデルベース開発から TOPPERS 搭載システムへのクロスレイヤ自動設計を利用したマルチコアモータ制御実装, https://github.com/ts1413/CrossLayerDesign

TOPPERS ATK2 (AUTOSAR 仕様) ルネサス エレクトロニクス社マルチコアマイコン RH850/F1H向け CCRH コンパイラ利用,https://www.toppers.jp/atk2.html

### 受賞

情報処理学会東海支部学生論文奨励賞,雑誌論文

ISE President Best Paper Award, 学会発表

優秀ポスター賞、学会発表

TOPPERS プロジェクト 第 7 回 TOPPERS 活用アイデア・アプリケーション開発コンテストアプリケーション開発部門 銅賞,「竹松慎弥,鍾兆前,井上雅理,横山静香,小島流石,近藤真己,<u>中本幸一</u>,安積卓也,道木慎二,本田晋也,枝廣正人,"モデルベース開発から TOPPERS 搭載システムへのクロスレイヤ自動設計を利用したマルチコアモータ制御実装"」,2017年11月.

### 6. 研究組織

(1)研究分担者

研究分担者氏名:道木 慎二

ローマ字氏名: (DOKI, Shinji)

所属研究機関名:名古屋大学

部局名:大学院工学研究科

職名:教授

研究者番号(8桁): 10273260

研究分担者氏名:安積 卓也

ローマ字氏名: (AZUMI, Takuya)

所属研究機関名:埼玉大学 部局名:大学院理工学研究科

職名:准教授

研究者番号(8桁): 40582036

研究分担者氏名:中本 幸一

ローマ字氏名: (NAKAMOTO, Yukikazu)

所属研究機関名:兵庫県立大学

部局名:大学院応用情報科学研究科

職名:教授

研究者番号(8桁): 70382273

(2)研究協力者

研究分担者氏名:本田 晋也

ローマ字氏名: (HONDA, Shinya)

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。