## 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 1 日現在

機関番号: 12612

研究種目: 研究活動スタート支援

研究期間: 2016~2017

課題番号: 16H06798

研究課題名(和文)ルータにおけるテーブル検索処理の省電力化および高速化に関する研究

研究課題名(英文)Low-Power High-Speed Table Lookup Processing in Routers

#### 研究代表者

八巻 隼人 (Yamaki, Hayato)

電気通信大学・大学院情報理工学研究科・助教

研究者番号:20782197

交付決定額(研究期間全体):(直接経費) 1,800,000円

研究成果の概要(和文):本研究では,ルータの省電力化およびパケット処理の高速化を実現するパケット処理キャッシュにおける,最適なキャッシュ制御手法およびハードウェアについて検討を行った.まず,パケット処理結果を事前にキャッシュに保存しておく,パケットの投機的処理技術により,これまで70%程度であったキャッシュヒット率を80%程度まで向上可能とした.更に,提案するパケット処理キャッシュをハードウェアレベルで詳細にシミュレーションおよび評価し,提案機構が実装可能なハードウェアコストであることを示した.

研究成果の概要(英文): This study proposed more efficient cache control mechanism for Packet Processing Cache (PPC), which enabled to process packets at high speed with significant low energy, and evaluated the hardware costs. First, we enabled to improve the cache hit rate of PPC from 70% to 80% to adopt a speculative packet processing method which stored processing results of packets into the cache in advance. In addition, we simulated and evaluated the hardware implementation of our approach and showed that our approach can be implemented with implementable hardware costs.

研究分野:計算機アーキテクチャ

キーワード: ルータ パケット処理 高スループット 省電力化 キャッシュ

#### 1.研究開始当初の背景

近年の通信データ総量の増加は著しく,通信データの転送処理を担うルータに要求される処理速度と,その処理にかかる消費電力の増大が深刻な問題となっている。全ネットワーク機器が消費する電力は世界総発電量の数%に達することが懸念されており,ルータには,処理速度を向上させながらも,省電力化を達成することが求められている.

ルータにおいて、処理速度上のボトルネックとなり、なおかつ高い電力を消費する処理に Ternary Content Addressable Memory (TCAM)と呼ばれる特殊なメモリの検索がある.TCAM は格納されたデータ 1bit 毎に比較器を有し、全データを同時に比較することで、高速なデータ検索を可能とするが、続々な電力を消費することが知られている.様々な報告によると、現在のコアルータ消費電力の30%以上が TCAM により消費されている.更には、TCAM により達成可能な処理速度がある.は現状の最高速度である 100Gbps 程度が限界であり、今後も加速するインターネット回線速度(例えば 400Gbps)に対応できない可能性がある.

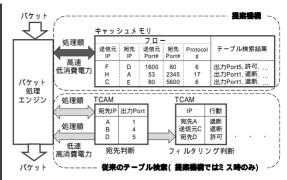

これに対し、頻繁に検索される TCAM 検 索結果を.より小規模だが高速かつ低消費電 力なキャッシュメモリに保存し,再利用する パケット処理キャッシュ(以下,PPCと呼ぶ) が提案されている .PPC の概要を図1に示す. PPC で用いられるキャッシュメモリは TCAM と比べ ,容量は 1/100 程度だが ,1/500 以下の消費電力で 10 倍以上高速にアクセス ができるため,パケットをキャッシュにより 処理できる場合には,従来よりも大幅に高速 かつ低電力な処理を実現できる、そのため、 PPC では、キャッシュにより処理できたパケ ットの割合(これをキャッシュヒット率と呼 ぶ)にその性能が大きく左右されることから, キャッシュヒット率の向上が重要な課題で ある.

#### 2.研究の目的

本研究では,以下の3項目を目的とする. (1) PPC におけるキャッシュミスの原因分析を詳細に行い,PPC におけるキャッシュの 学動を明らかとする.

- (2) (1)で得られた分析結果から, PPC に最適なキャッシュ制御手法(小規模なキャッシュに, いかに再利用性の高い TCAM 検索結果を蓄えるか)を提案する.

- (3) これまでの研究では行われてこなかった PPC 全体のハードウェアコストを詳細に見積り,その実用性,実現性について評価する.

#### 3.研究の方法

(1) 報告者は、様々な実ネットワークで得られた通信トラフィックのトレースを持っ

図1 PPC の概要

ている、そこで、これらのトレースからパケットの統計情報を分析することや、自作のPPC シミュレータを用いたキャッシュミス率の測定などにより、実ネットワーク環境における PPC のふるまいを明らかにする.

(2) これまで,研究目的(2)を達成するために様々なキャッシュ制御手法が提案されてきたが,PPCにおいて最大のキャッシュミス要因である初期参照ミスを削減する手法は未だ提案されていない.初期参照ミスとは、キャッシュの初参照時にまだキャッシュ内に再参照データが保存されていないために生じるキャッシュミスであり,PPCでは通信ストリームの1パケット目において必ず生じる.そこで,本研究ではこの初期参照ミスに焦点を当て,その削減手法を検討する.

多くのインターネットアプリケーションは要求・応答モデルに従って通信しており、クライアントからの要求にサーバが応答する形でサービスが提供される.ここで,応答通信は要求通信からある程度の予測が可能である.この事実を基に,本研究では要求パケット到着時に応答パケットを予測し,事前に処理を行いキャッシュしておく投機的なパケット処理手法を提案する.

(3) PPC の実運用に際して,キャッシュヒット率を向上させる様々なキャッシュ制御手法の適用は重要だが,何よりこれらの手法が実装可能な回路規模であり,またこれらのハードウェアにより消費電力が増大しないことが重要である.そこで,本研究ではハードウェア記述言語を用いて,実際にルータで用いられる ASIC を対象としたハードウェアシミュレーションにより,提案機構の回路規模や必要メモリ量,また消費電力について概算を行う.

## 4. 研究成果

(1) 本研究において様々な実ネットワークトラフィックを分析したところ,ネットワーク内では1パケットから10パケット程度で構成されるマイスフローと呼ばれる通信がフローの大多数を占めていることが明らかとなった.一方で,パケット数の観点から見ると,数万単位のパケットで構成されるエレ

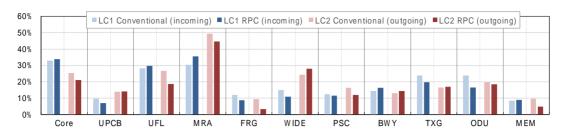

図2 従来手法と提案手法のキャッシュミス率比較

ファントフローと呼ばれる通信が大部分を占めていることが明らかとなった.これらの分析結果から,PPC においては,キャッシュ不要なマイスフローの TCAM 検索結果を適切にキャッシュ内から排除し,再参照度合の高いエレファントフローの TCAM 検索結果を優先的にキャッシュに確保することが重要であることが示された.

"研究の方法"で述べた,応答パケッ トの投機的パケット処理手法に関して,実際 のネットワークトラフィックを用いて,その 実用性を評価した.図2に従来手法と提案手 法によるキャッシュミス率の比較結果を示 した.シミュレーションでは,提案手法によ リ平均で 10.7%, 最大で 50.6%のキャッシュ ミスが削減可能であることを示した.また, シミュレーション結果から,提案手法はトラ フィックの方向(アップストリームかダウン ストリームか), すなわち要求通信と応答通 信の割合の違いにより、性能に差が生じるこ とがわかった.これは,提案手法が応答通信 によるキャッシュミスの削減に焦点を当て ていることから,アップストリームに対して は効果が得られないどころか, キャッシュに 不要な TCAM 検索結果を保存してしまうこと で,キャッシュミスが増加してしまうことを 意味している.そこで,本研究では,提案手 法を改善し,ルータの初期設定時に提案手法 が有効かどうかを数秒の試行で判断し,以降 その判断結果に基づいて提案手法の ON/OFF を決定する手法を提案した. 本手法の評価に おいては,たった1,000パケット程度を用い た試行により、十分な精度で提案手法の ON/OFF を判断できることを示した.

(3) 本研究では、TCAMとキャッシュメモリ、提案するキャッシュ制御手法の3つに分け、それぞれの回路規模や消費電力について見積を行った.まず、回路規模については近年のルータで用いられる TCAM が 729mm² 程度であるのに対し、キャッシュメモリは0.372mm²程度,またキャッシュ制御モジュールは0.00178mm²程度であることから、TCAMと比べて PPC の機構は十分に回路規模が小さいことが示された.更に、本研究で提案したキャッシュ制御モジュールはキャッシュメモリの0.5%程度の回路規模であり、実装において問

題となるほどのコストではない.また,消費電力に関しても,TCAMの動的消費電力が30nJ程であるのに対し,キャッシュメモリは0.054nJ程であり,TCAMの0.18%程の消費電力でアクセス可能であることが示された.以上の結果より,提案するPPC機構は十分に実装可能であり,また消費電量上のオーバーへッドも小さいことが示された.

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

[雑誌論文](計0件)

## [学会発表](計22件)

H. Yamaki, Flow Characteristics-Aware Cache Replacement Policy for Packet Processing Cache, 2018 SAI Future of Information and Communications Conference (FICC 2018), 2018.

H. Yamaki and H. Nishi, Line Replacement Algorithm for L1-scale Packet Processing Cache, In Adjunct Proceedings of 13<sup>th</sup> Annual International Conference on Mobile and Ubiquitous Systems: Computing, Networking and Services (MOBIQUITOUS '16), 2016.

愛甲達也,八巻隼人,三輪忍,本多弘樹, ゲートウェイにおける攻撃パケットに 着目したテーブル検索負荷削減手法の 提案,情報処理学会システム・アーキテ クチャ研究会,2018

八巻隼人 ,愛甲達也 ,三輪忍 ,本多弘樹 , パケット処理キャッシュにおける送信 元 IP アドレスに着目したミス削減手法 に関する初期検討 ,情報処理学会システム・アーキテクチャ研究会 , 2017 八巻隼人 ,西宏章 ,L1 規模のパケット処理キャッシュにおけるライン置き換え 方式の検討 ,情報処理学会システム・アーキテクチャ研究会 , 2016

[図書](計0件)

〔その他〕 ホームページ等 http://www.hpc.is.uec.ac.jp/yamaki\_lab/

index-jp.html

# 6 . 研究組織

## (1)研究代表者

八巻 隼人 (YAMAKI, Hayato)

電気通信大学・大学院情報理工学研究科・

助教

研究者番号:20782197