#### 研究成果報告書 科学研究費助成事業

今和 元 年 6 月 1 1 日現在

機関番号: 13903

研究種目: 基盤研究(C)(一般)

研究期間: 2016~2018 課題番号: 16K06350

研究課題名(和文)低コスト 変調器評価手法を用いる1ビット信号処理システム開発

研究課題名(英文)Development of 1-bit signal processing system using low cost evaluation method of Delta Sigma modulator

#### 研究代表者

平野 智(HIRANO, Satoshi)

名古屋工業大学・工学(系)研究科(研究院)・准教授

研究者番号:90238379

交付決定額(研究期間全体):(直接経費) 3,800,000円

研究成果の概要(和文):1ビット信号処理回路については、基本的な最小構成単位の回路の組み合わせによる 実現方法は回路規模や精度の点について有効ではないが、実現したい機能全体の一括構成手法については実用の 可能性があることを示した。 変調器の最適設計については、GA法を用いることで3次 変調器に対して設 計手法の有効性を示すことができた。実装における問題点については、FPGAとPCを用いてアナログ発振器を用い ない低コストである1ビット信号を用いた 号処理回路の評価に利用できることを示した。 変調器の評価システムを実現することができ、開発した1ビット信

研究成果の学術的意義や社会的意義 変調器の最適設計については、3次 変調器において従来よく用いられているアルゴリズムと比較してよ り高いSNRを実現する変調器、あるいはより最大入力信号振幅の大きい変調器の設計が可能であることから、変調器の設計が必要な分野にとって有益な結果である。

FPGAとPCを用いてアナログ発振器を用いない低コストである1ビット信号を用いた 変調器の評価システムを実現することができたことは、変調器単体の性能を低コストで評価することができることから、オーディオのみならず、計測制御システム、ウェアラブルデバイスなど 変調器をシステムに組み込む分野にとって有益な結 大がず、 ならず、 果である。

研究成果の概要(英文):For 1-bit signal processing circuits, it was confirm that the method of realization by combination of the circuits of the basic minimum configuration unit was not effective in terms of circuit scale and accuracy, but the method of realization by the circuits of collective configuration of all functions will be a possibility of practical use. For the optimum design of the Delta-Sigma modulator, it was confirm that the proposed design of the third-order Delta-Sigma modulator by using the GA algorithm was effective. For the problems of the implementation, it was confirm that the low cost evaluation system of the Delta-Sigma modulator using 1-bit signal was realized with FPGA and PC without using an extremely high cost analog oscillator, and the proposed evaluation system will be useful for the developed 1-bit signal processing circuit.

研究分野: 工学

キーワード: 変調器 FPGA 1ビット信号処理

# 様 式 C-19、F-19-1、Z-19、CK-19(共通)

#### 1.研究開始当初の背景

オーディオの分野ではハイレゾオーディオまたはハイレゾ音源が注目を浴びている。この理由として、人間はより高分解能あるいはより広い信号周波数帯域の情報を欲していると考えられる。しかしながら従来手法のAD変換器でアナログ信号をディジタル信号に変換した場合には、分解能も信号周波数帯域も限定されてしまい、周波数帯域を広くするためには推定するしか手段がない。

AD 変換器により高い分解能、より広い信号周波数帯域を望むことは、高いダイナミックレンジやより多くの情報が求められるロボットや自動車をはじめとして計測制御システムにとっても同様である。さらには急速に発展してきたウェアラブルデバイスのように、小型、低消費電力化に答えられることも必須の要素である。

これらの要求にこたえるひとつの手法として、オーバサンプリング方式による 変調器がある。 変調器を用いる従来の手法として、 変調器の出力 1 ビット信号に対してディジタルデシメーションを行う構成が用いられてきたが、この手法ではディジタルデシメーションにて信号周波数帯域を限定していることになる。しかし 変調器の出力 1 ビット信号はオーバサンプリングされているので信号周波数帯域は限定されていない。そこで信号周波数帯域を限定することなくディジタル信号処理する方法、つまり 変調器出力の 1 ビット信号に対して直接ディジタル処理を行う、1 ビット信号処理回路が有効であると考えられる。しかしながらこの手法では 変調器も合わせた一体のシステムとして検討する必要がある。さらに 1 ビット信号に対して直接性能評価を行う必要が出てくる。

#### 2 . 研究の目的

本研究では、 変調器を用いた1ビット信号処理システムの開発を研究目的とする。従来のオーバサンプリング 変調器の1ビット信号からデシメーションを行うディジタル信号システムは、デシメーションによるポスト処理の処理時間による信号遅延などの点において、逐次比較などの従来方式のAD変換器を用いた場合と同程度である。本研究では 変調器の出力1ビット信号を直接ディジタル信号処理することにより 変調器の利点を最大限に利用し信号遅延も含め従来方法では実現しえないディジタル信号システムの開発を検討するものである。変調器の評価方法として従来のアナログ処理を含まない完全ディジタル方式の確立も含まれる。

#### 3.研究の方法

本研究においては以下の3点について実施する。

- (1) 1 ビット信号処理回路: 変調器の出力である 1 ビット信号を入力とする信号処理システムについて、基本的な最小構成単位(単位遅延や加算器など)を組み合せる構成、実現したい機能全体の一括構成などの手法について検討を行う。また従来手法では実現できないため、それら 1 ビット信号処理回路の評価方法についても検討を行う。

- (2) 変調器の最適設計:これまでの研究成果である電力関係式を用いた量子化器の線形モデル化による最適設計について、最急降下法、SA(Simulated Annealing)法、GA(Genetic Algorithm)法などのアルゴリズムを用いて、実装時の素子値等の誤差による影響に対してよりロバストな設計手法および計算時間の短縮方法の開発を行う。

- (3) 実装における問題点:ディジタル回路部分を FPGA 上に実装しネットワークを経由して接続された PC 上で解析を行う手法を発展させ、完全ディジタル方式の評価システムとして FPGA 上に実装した理想信号源およびディジタル 変調器を用いた、1 ビット信号を入力信号とした変調器の評価手法を確立する。また周辺回路のアナログプレフィルタ部分を実装して低ノイズ電源や耐ノイズ配線、耐ノイズ基板実装技術の確立を求めて市販品の 変調器 IC の測定手法の確立を目指す。

### 4.研究成果

上記研究の方法(1)~(3)についてそれぞれの研究成果を以下のとおり示す。

(1) 1 ビット信号処理回路: FPGA 上に実装して評価することを中心とした手法として、基本的な最小構成単位の回路単体についての評価およびこれらの組み合わせによる構成の一つである周波数サンプリング法によって構成したディジタルフィルタ回路について検討を行った。得られた結果としては、最小構成単位の回路単体の性能向上が難しく、また周波数サンプリング法によって構成したディジタルフィルタでは想定していたよりも感度が高く十分な係数精度を取る必要があり全体としてみると回路規模が想定以上に大きくなることがわかった。したがって本手法はあまり有効ではないと結論付けた。そこで実現したい機能全体の一括構成手法として超音波を用いた距離推定手法を題材として方針転換をして検討を行った。計測信号を別途作成し1ビット信号処理回路を FPGA 上に実装した評価実験においては、回路規模や精度および推定時間について十分な実用性を持つことが判明したが、周辺部の回路を含めた全体を完全実装したシステムについての評価は研究期間内に実施することができず、今後の課題として持ち越すこととした。

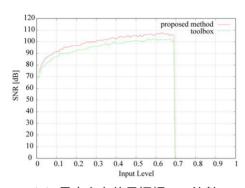

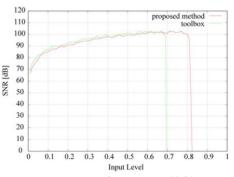

変調器の最適設計:SA法およびGA法を中心に検討を行ったが、GA法を用いる最適設 計法について交差法に工夫をすることで成果が得られた。実装時の素子値等の誤差による影響 に対してよりロバストな設計法となるように制約条件を加えた上でも、3 次の れば実現可能なパラメータの全探索によって得られた最適解をほぼ探索できる最適設計アルゴ リズムを構築することができた。設計結果の有効性を確認するために、 変調器の設計でよ く用いられる MATLAB 上で動作する ツールボックスを用いて設計した結果と比較を行った。 結果を図1に示す。図1(a)は ツールボックスで設計された結果と最大入力信号振幅が同程 度になるよう設計した結果であり、提案法では最大 SNR が約 5dB 向上することがわかる。図 1 (b)では最大 SNR が同程度になるよう設計した結果であり、提案法では最大入力信号振幅が約 変調器においても優秀と考えられ 1.5dB 向上することがわかる。しかしながらより高次の る最適設計アルゴリズムであるがパラメータの全探索が不可能なため最適解であることの検証 手法に課題を残した。

(a) 最大入力信号振幅での比較

(b) 最大 SNR での比較

図1:設計結果の比較

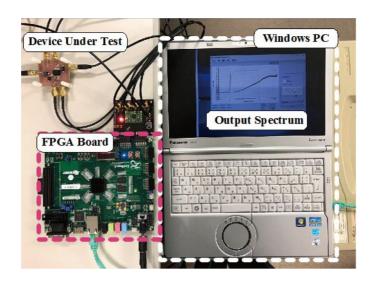

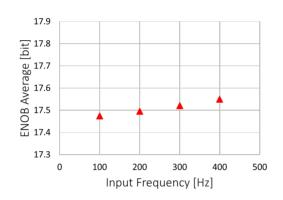

変調器(DUT)の出力1ビット信号をFPGAに取 (3) 実装における問題点:性能評価を行う り込みデータ蓄積および転送用ディジタル回路部分を FPGA 上に実装しネットワークを経由し て接続した PC 上で解析を行う手法での問題点は、DUT に入力するアナログ正弦波としてどれだ け高精度、低雑音の発振器を準備できるかが鍵であった。発振器から発生する雑音や電源電圧 の高調波などは性能評価を行う 変調器からもそのまま出力されてしまい、DUTで発生する 雑音や高調波と区別がつかないためである。また市販の発振器ではどのような高価な機器を用 いても精度として 16 ビット程度が限界であり、さらなる精度向上のために別途アナログ回路を 追加すれば、追加した回路から発生する雑音や信号を伝播するケーブルに混入する雑音などの 問題を抱えることになり、また測定信号の可変化などへの柔軟な対応が困難になる。そこで FPGA 上にディジタル回路により構成された DDS による理想発振器を実現し、このディジタル正 弦波信号から完全ディジタル 変調器を用いて1ビット信号を生成し、さらに1ビット信号 の振幅可変装置等を備えることにより、DUT への入力信号に 1 ビット信号を用いた の評価システムの実装を行った。FPGA 上に実装した DDS から生成される正弦波の周波数や振幅 可変装置の制御は FPGA を通してすべてソフトウェア上で実現することで、測定信号の可変化に 柔軟に対応することができる。 また PC 上のソフトウェアにより、 記録、1 ビット信号の測定( 時 間軸上での計測 ) FFT を用いた周波数スペクトルの測定 (周波数軸上での計測 ) およびこれ らの結果からの DUT の性能評価を SNR やダイナミックレンジなどで数値化する仕組みを実装し た。さらに FPGA 上の完全ディジタル 変調器についても性能評価を行い、従来手法の高価な アナログ正弦波発振器を用いた評価方法と同等の安定性を持ったシステムであることを示すこ とができた。システムの概観を図2に示す。性能評価を行うDUTを実装した基板およびDUTを 動作させる電源以外には、FPGA が実装された評価ボードおよび自作ディジタル回路ボードと PC のみを用いており、高価な高精度アナログ発振器等のアナログ回路を一切用いない、低コスト である1ビット信号を用いた 変調器の評価システムが実現できていることがわかる。この システムを応用することによって開発した 1 ビット信号処理回路の評価が可能になる。今回実 験した DUT を実装した基板においては実装上の工夫により 変調器 IC の性能が 17 ビット以 上あることが図3のグラフからも確認できる。ただし 変調器 IC の種類ごとに低雑音化す るための実装上の工夫が必要であるため、この検討については引き続き実施する必要がある。

図2:1ビット信号を用いた 変調器評価システムの概観

図3:実験した 変調器の性能評価結果

# 5. 主な発表論文等

### [雑誌論文](計 3 件)

Yoshiaki Otsu、Junya Hattori、<u>Satoshi Hirano</u>、Tomio Goto、High-Precision Evaluation System Using High-Order Digital Modulator for Digital Audio System、Consumer Electronics (GCCE), 2018 IEEE 7th Global Conference on、查読有、2018、pp.499-500 DOI: 10.1109/GCCE.2018.8574658

Kenta Tsuge、Yoshiaki Otsu、<u>Satoshi Hirano</u>、Tomio Goto、Evaluation system for digital audio system under variable conditions、Consumer Electronics (GCCE), 2017 IEEE 6th Global Conference on、查読有、2017、pp. 1-2

DOI: 10.1109/GCCE.2017.8229310

Kenta Tsuge, Kazuya Okuma, <u>Satoshi Hirano</u>, Tomio Goto、Evaluation Method by High-Speed 1-Bit Stream for Digital Audio System、Consumer Electronics, 2016 IEEE 5th Global Conference on、查読有、2016、pp.1-2

DOI: 10.1109/GCCE.2016.7800457

# [学会発表](計 9 件)

Yoshiaki Otsu, Junya Hattori, <u>Satoshi Hirano</u>, Tomio Goto, High-Precision Evaluation System Using High-Order Digital Modulator for Digital Audio System, IEEE 7th Global Conference on Consumer Electronics (GCCE2018), 2018

服部 純也, <u>平野 智</u>, 後藤 富朗、1bit 信号処理によるリソース効率化を目的とした周波数サンプリングフィルタの設計手法、電気・電子・情報関係学会東海支部連合大会、2018 浜口 祐弥, , 吉野 友弥, <u>平野 智</u>, 後藤 富朗、1 ビット信号処理を用いた超音波距離推定の高速化、電気・電子・情報関係学会東海支部連合大会、2018

Kenta Tsuge、Yoshiaki Otsu、<u>Satoshi Hirano</u>、Tomio Goto、Evaluation system for digital audio system under variable conditions、IEEE 6th Global Conference on Consumer

Electronics, 2017

世古 潤平, 平野 智, 後藤 富朗、遺伝的アルゴリズムによる 変調器の最適設計手法 実装を考慮した有効性の検討 、電子情報通信学会ソサイエティ大会、2017

大津 慶明, 柘植 健太, 平野 智, 後藤 富朗、FPGA を用いた 変調器のリアルタイム評価システムの GUI の改善、電子情報通信学会ソサイエティ大会、2017

柘植 健太,大津 慶明,<u>平野智</u>,後藤 富朗、任意周波数条件を設定可能な 変調器の1 ビット評価手法、電気・電子・情報関係学会東海支部連合大会、2017

Kenta Tsuge, Kazuya Okuma, <u>Satoshi Hirano</u>, Tomio Goto, Evaluation Method by High-Speed 1-Bit Stream for Digital Audio System, IEEE 5th Global Conference on Consumer Electronics, 2016

世古 潤平, 平野 智, 後藤 富朗、有効な探索を優先した遺伝的アルゴリズムによる 変調器の最適設計手法、電子情報通信学会ソサイエティ大会、2016

[図書](計 0 件)

# 〔産業財産権〕

出願状況(計 0 件)

名称: 発明者: 権利者: 種類: 種号: 出原外の別:

取得状況(計 0 件)

名称: 発明者: 権類: 種類: 番号: 取得外の別:

〔その他〕 ホームページ等

6.研究組織

(1)研究分担者

研究分担者氏名:

ローマ字氏名:

所属研究機関名:

部局名:

職名:

研究者番号(8桁):

(2)研究協力者

研究協力者氏名:

ローマ字氏名:

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。