#### 研究成果報告書 科学研究費助成事業

今和 元 年 6 月 2 1 日現在

機関番号: 15401

研究種目: 基盤研究(C)(一般)

研究期間: 2016~2018 課題番号: 16K06356

研究課題名(和文)ネットワーク化制御に適した量子化器の実現

研究課題名(英文) Realization of quantizers for networked control systems

#### 研究代表者

大野 修一(Ohno, Shuichi)

広島大学・工学研究科・准教授

研究者番号:70273919

交付決定額(研究期間全体):(直接経費) 3,700,000円

研究成果の概要(和文):ディジタル機器で利用するとき、信号はサンプリングされ量子化される。量子化とはもともと連続値である信号の値をある有限個の離散値で表現することである。量子化においては、量子化誤差と呼ばれる誤差が発生する。 本研究は、実現が容易な構造を持つデルタシグマ変調器による量子化器の設計と解析を行っている。量子

化誤差の影響を解析的に評価することで、量子化誤差の影響を最小にするデルタシグマ変調器の設計法を導出し

研究成果の学術的意義や社会的意義 構造が簡易で実現が容易なデルタシグマ変調器による量子化は電子機器に広く利用されている。従来のデルタシ グマ変調器は変調器の出力の周波数領域での情報に基づき設計されてきた。実際のシステムでは、多くの場合、 量子化された信号はあるシステムに入力され出力される。本研究は、システムの出力における量子化誤差の影響 を最小にするデルタシグマ変調器を設計しており、従来法より量子化誤差の影響を低減化している。

研究成果の概要(英文):To enter signals into digital devices, signals are sampled and quantized. Quantization is to convert continuous-valued signals into discrete-valued signals that can take only a finite number of discrete values.

In quantization, so-called quantization errors are generated. We analyze and synthesize the quantization by easily realizable Delta-Sigma modulators having a relatively simple structure. We analytically evaluate the effect of quantization errors on the system and develop designs of Delta-Sigma modulators to minimize the effect.

研究分野: 信号処理

キーワード: デルタシグマ変調器 量子化 ネットワーク化制御 システム実現

様 式 C-19、F-19-1、Z-19、CK-19(共通)

## 1.研究開始当初の背景

アナログ信号をディジタル機器で扱うためには、信号をサンプリングし量子化しなければならない。このアナログディジタル(A/D) 変換は、現代のさまざまなシステムにおいて必要不可欠である。

信号を A/D 変換すると誤差が生じる。ディジタル機器が利用できるようになった当初は、機器の性能の制約やコストの問題のため、十分なサンプリング周波数を達成できず、ディジタル値を表現するためのビット数が限られていた。特にビット数の制約による誤差(量子化誤差)の影響は大きく、量子化誤差を低減化するため多くの研究がなされてきた。

デルタシグマ変調器は、簡易な構成ながら高速サンプリングにより量子化できることから、広く 利用されている。

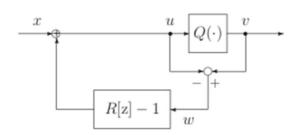

図1 デルタシグマ変調器

図1にデルタシグマ変調器の概略図を示している。 $Q(\cdot)$ は一様量子化器、R[z]-1 はフィードバックフィルタである。デルタシグマ変調器では一様量子化器の出力 v をフィードバックしフィルタンリグした信号が入力信号 x と加算され一様量子化器に入力される。このとき、デルタシグマ変調器の出力は v=x+R[z]w となる。ここで、w は一様量子化器の量子化誤差であり、フィードバック構造により一様量子化器の量子化誤差はノイズ整形フィルタで処理されることになる。ノイズ整形フィルタを適切に設計することで、望ましいデルタシグマ変調器が得られる。一方、近年、機器間の信号を無線通信により伝達し制御を行うネットワーク化制御の必要性が高まっている。複数の小型センサからの情報を無線通信により収集し、多数の機器を無線で接続する場合、帯域が制限される。また、装置を簡易化するとともにバッテリー寿命を延すためには、できるだけ少ないビット数で情報を伝達しなければならない。そのため、単純な構成で効果的に量子化誤差の影響が低減化できる量子化器が必要となっていた。

#### 2.研究の目的

本研究の目的は、ビットレート制約のあるネットワーク化制御に適した量子化器を設計することである。比較的単純な構成を持ち容易に実現できるデルタシグマ変調器を量子化器として採用し、通信品質であるビットレート制約のもとで制御品質である誤差量を最小にするデルタシグマ変調器を設計し、ネットワーク化制御システムにおいて量子化誤差の影響を効果的に低減化できる技術を実現する。

#### 3.研究の方法

図 1 のデルタシグマ変調器において、フィードバックフィルタと一様量子化のパラメーラを設計する。ビットレート制約により、一様量子化器のレヴェル数が決定される。

デルタシグマ変調器の出力がある線形システム H[z]に入力されたとすると、その出力は y=H[z]x+H[z]R[z]w となり、量子化誤差のない場合の出力 H[z]x に、誤差 H[z]R[z]w が加算されていることがわかる。

一方、デルタシグマ変調器内においてフィードバックを大きくすると、一様量子化の入力 u の 振幅が大きくなり、オーバーフローが発生する可能性がある。オーバーフローが発生すると量子 化誤差が非常に大きくなる可能性があるため、オーバーフローが発生しないようフィードバックにオーバーフロー制約を課す。

フィードバック信号と誤差信号の大きさはノルムにより評価する。まず、一様量子化器の誤差を 白色ノイズとモデル化したときの信号の分散と信号の絶対値の最大値である I1 ノルムを採用 する。前者は、システムの 2 ノルムで評価できる。後者、既存の理論を用いて線形行列不等式 により数値的に評価する。オーバーフローに関する制約は I1 ノルムで表現できる。

これらの表現により設計問題は、制約のある最適化問題として定式化する。つぎに、最適化問題を数値的に解くことで、デルタシグマ変調器を設計する。さらに、設計したデルタシグマ変調器の特性を数値シミュレーションで評価する。

## 4. 研究成果

デルタシグマ変調器のフィードバック信号に対するノルム制約のもとで量子化誤差の影響を最小にするデルタシグマ変調器の設計法を、数値最適化問題として定式化した。従来法と異なり、デルタシグマ変調器に接続されるシステムの出力における量子化誤差の影響を最小化しているため、最適化問題は接続システムに依存している。また、デルタシグマ変調器の最適設計問題は双線形行列不等式で記述できることを示し、最適設計問題が NP 困難であることを明らかにしている。最適設計問題に緩和を適用したのち双線形行列不等式を行列不等式に変換することで、量子化誤差の影響の最小化問題を凸最適化問題の帰着し、拡張線形行列不等式を数値的に解くことで、デルタシグマ変調器を設計する手法を提案している。このデルタシグマ変調器は接続システムと同次数の無限インパルス応答型のノイズ整形フィルタを持ち、低計算量のフィルタで実装可能である。また、デルタシグマ変調器のフィードバック信号に対するノルム制約により、デルタシグマ変調器の安定性が保障されている。提案法で設計したデルタシグマ変調器を用いた数値シミュレーションによりその性能を評価し、提案法の有効性を確かめている。

デルタシグマ変調器はオーバーサンプリングにより量子化誤差を小さくすることができる。一方、オーバーサンプリングは単位時間あたりの情報量を増やす。つまり、誤差の低減化と情報量の増大はトレードオフの関係にある。そこで、このトレードオフの理論的な解析を行った。量子化誤差の平均自乗誤差を最小にするデルタシグマ変調器が、あるひとつのパラメータを用いて数値的に求められることを証明し、数値例によりその妥当性を示している。この最適デルタシグマ変調器を用いることで、オーバーサンプリングと量子化誤差の平均自乗誤差の関係を明らかにしている。また、線形行列不等式を用いた最適化によるデルタシグマ変調器の設計法を提案している。さらに、オーバーフローが発生しないようフィードバック信号に制約を課し最大誤差を最小とすることで、オーバーフローのない最大誤差を最小にするデルタシグマ変調器を設計し、数値例によりその性能を評価している。

理想モデルに追従するよう制御するモデル追従制御においてディジタル制御器を用いる場合、量子化された信号がコントローラへ入力される。このとき、開発したデルタシグマ変調器による量子化を適用することで、従来法より量子化誤差の影響が低減できることを示している。制御入力に制限があるシステムではワインドアップ現象により性能劣化する場合がある。量子化では、ある範囲の数値以外の数値に対してはオーバーフローが発生する。オーバーフローが発生すると制御入力が制限されることになり、ワインドアップ現象が発生する可能性がある。そこで、適切に設計した複数のデルタシグマ変調器を用いることで、量子化誤差の影響を低減化しつつ、ワインドアップ現象に対応する方法を提案している。

DC/AC インバータは 2 値パルス信号を回路に入力することで、直流電流を交流電流に変換する。 2 値パルス信号の発生のため、パルス幅変調器が利用されている。望ましい 2 値パルス信号をデルタシグマ変調器で発生する方法を提案し、パルス幅変調器を用いた場合より高品質な交流電流の発生を可能にしている。

離散時間フィルタをディジタルデバイスに実装するとき、量子化によるオーバーフローが問題となる。そこで、同じビット数を用いたときに、オーバーフローに頑健な実装方法を提案しその有効性を示している。

#### 5 . 主な発表論文等

〔雑誌論文〕(計5件)

- 1. <u>Shuichi Ohno</u> and Yuichi Yoshimura, State space realizations robust to overloading for discrete-time LTI systems, Signal Processing, 查読有, vol. 156, 2019, pp. 12-20.

- 2. <u>Shuichi Ohno</u>, Yuma Ishihara, and Masaaki Nagahara, Min-Max design of feedback quantizers without overloading, IEEE Transactions on Circuits and Systems I: Regular Papers, 查読有, vol. 65, no. 4, 2018, pp.1395-1405.

- 3. M. Rizwan Tariq and <u>Shuichi Ohno</u>, An iterative LMI algorithm for quantization noise reduction in Delta-Sigma modulators, Signal Processing, 査読有, no. 144, pp.163-168, March 2018.

- 4. <u>Shuichi Ohno</u>, Teruyuki Shiraki, M. Rizwan Tariq, and Massaaki Nagahara, Mean squared error analysis of quantizers with error feedback IEEE Transactions on Signal Processing, 査読有, vol. 65, no.22, 2017, pp. 5970-5981.

- 5. <u>Shuichi Ohno</u> and M. Rizwan Tariq, Optimization of noise shaping filter for quantizer with error feedback, IEEE Transactions on Circuits and Systems I: Regular Papers, 查読有, vol.64, no. 4, 2017, pp. 918-930.

# [学会発表](計3件)

- 1. <u>Shuichi Ohno</u>, Delta-Sigma modulators for constant envelop transmissions with guaranteed stability, Proc. of IEEE International Conference on Acoustics, Speech and Signal Processing, pp. 3724-3728, Calgary, Canada, April 2018.

- 2. M. Rizwan Tariq and <u>Shuichi Ohno</u>, Min-max IIR filter design for feedback quantizers, Proc. of APSIPA ASC 2017, Kuala Lampur, Indonesia, December 2017.

- 3. M. Rizwan Tariq and <u>Shuichi Ohno</u>, Design of a continuous-time loop filter for Delta-Sigma modulators with excess loop delay, Proc. of the 49th ISCIE International Symposium on Stochastic Systems Theory and Its Applications, Hiroshima. November. 2017.

[図書](計0件)

〔産業財産権〕 出願状況(計0件)

名称: 発明者: 権利者: 種号: 番号: 出内外の別:

取得状況(計0件)

名称: 発明者: 権利者: 種類: 番号: 取内外の別:

〔その他〕 ホームページ等

6.研究組織

(1)研究分担者 研究分担者氏名:

ローマ字氏名: 所属研究機関名:

部局名:

職名:

研究者番号(8桁):

(2)研究協力者

研究協力者氏名:永原 正章 ローマ字氏名:Nagahara Masaaki

研究協力者氏名:Tariq, M. Rizwan ローマ字氏名:Tariq, M. Rizwan