# 科研費

## 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 4 日現在

機関番号: 1 2 6 0 1 研究種目: 挑戦的萌芽研究

研究期間: 2016~2017

課題番号: 16K14227

研究課題名(和文)光照射キャパシタンス測定による熱酸化処理後のSiC基板中欠陥の半定量的評価

研究課題名(英文) Quasi-quantitative characterization of defect density in SiC substrate after

thermal oxidation by photo-assited capacitance measurement

#### 研究代表者

喜多 浩之(Kita, Koji)

東京大学・大学院工学系研究科(工学部)・准教授

研究者番号:00343145

交付決定額(研究期間全体):(直接経費) 2,800,000円

研究成果の概要(和文): MOSデバイスでは,半導体のバンドギャップに対応するエネルギー範囲での欠陥準位の低減が不可欠である。SiCを含むワイドギャップ半導体では,界面近傍の酸化膜中に存在する準位やパンドギャップ中央付近の深い準位に捕獲された電荷の放出の時定数が極めて長く,従来のMOSキャパシタを用いた評価手法では見過ごされている。本研究では,単色化された紫外光や可視光の照射によって一旦電荷を放出させた欠陥準位に,印加電圧の掃引と共に捕獲されていく過程を解析してMOS界面に形成される応答の遅い欠陥準位の分布を推定する手法を提案する。また,同分布についてSiC界面を形成する酸化プロセスによって生じる違いを明確化した。

研究成果の概要(英文): Reduction of defect state density in the energy range corresponding to semiconductor's bandgap is inevitable for the operation of MOS devices, however, for the wide-bandgap semiconductors including SiC, the defect states locating in near-interface oxide, and those with the energy level near the middle of the bandgap often overlooked in conventional characterization techniques using MOS capacitors, due to a significantly long time constant of the electron emission from those states. We proposed an alternative method to estimate the profiles of such defect states at SiC MOS interfaces, based on the analysis of the carrier capturing process by voltage bias sweep just after the removal of the trapped carriers by irradiation of monochromatic ultraviolet or visible light. Using this method, we also clarified the difference of deep defect level profiles at SiC MOS interface formed by different oxidation processes of SiC.

研究分野:電子デバイス材料工学

キーワード: 電子・電気材料 表面・界面物性 半導体物性 電子デバイス・機器 光照射 炭化ケイ素 界面準位

影点

#### 1.研究開始当初の背景

4H-SiC を始めとするワイドギャップ半導体デバイスは、電力制御用パワーデバイスの高効率化のための切り札として期待が集まっている。ところが、SiC のパワーMOSFETは、MOS 界面形成技術が未成熟であるために反転層チャネルの抵抗が大きい、或いは動作信頼性が不足する等の課題がある。本伝の熱時点で研究代表者らは既に、4H-SiC の熱的に及の無力学的・速度論的に CO の生成と説離に有利となる条件を選択的に利用した認識に有利となる条件を選択的に利用した認識に有利となる条件を選択的に利用した認識に有利となる条件を選択的に利用した認識に有利となる条件を選択的に利用した説があり、対応によって MOS 界面品質の目安 が応いてある。 "界面欠陥準位密度(Dit)"が広いエネルギー範囲で< 10<sup>11</sup>cm<sup>-2</sup>eV-1 を実現できることを実証していた。

しかしながら、Ditをここまで減らしたプロセスを用いてもチャネル移動度の改善は限定的であった。SiC の物性を考慮すると、まだ数倍~10 倍の向上の余地が残っているため、MOS 界面にはもっとほかにキャリア移動度を大きく制約する重要な因子が残されたままであると考えるのが自然である。

#### 2.研究の目的

上記の背景を踏まえると,SiC を始めとするワイドギャップ半導体デバイスでは,従来の Si デバイスで用いられてきた界面品質評価手法をそのまま当てはめただけでは見落とされてしまうような界面欠陥の影響を選択的に抽出するための新しい評価手法が必要である。

本研究では特に,ワイドギャップ半導体デバイスの界面欠陥の2つの特徴に着目した。第一に,理想的な界面ではなくゲート酸化時内部に欠陥構造を内包するために,SiC界面から僅かに離れた位置の欠陥への電荷捕獲を考慮する必要がある。このような欠陥への手ャネル電荷の捕獲・放出は,酸化膜内のトンネル過程を経るために距離に応じて急激に時定数が大きくなる。従って同じエネルであっても,空間的な位置に応じてルベルであっても,空間的な位置に応じて様々な時定数の電荷捕獲が生じるということである。

第二に、空間的には界面に位置していたとしても、バンドギャップの中央に近いエネルギー帯に形成された欠陥準位は、キャリア捕獲と放出の時定数が非常に長くなることである。一度捕獲されると、通常の電気特性のバイアス印加時間内に放出される確率が低い点が特徴であり、MOS キャパシタ動作など表面ポテンシャルの掃引範囲が限定においては放出されず、しかし実際のMOSFET の反転バイアス下でのみ放出されるといった応答が想像される。これらの特徴を踏まえ、それを検出できる測定手法を案・実証することを本研究の目的とした。

# 3.研究の方法

ワイドギャップ半導体の MOS キャパシタを

用いて界面(近傍)準位への電荷捕獲量を評価するために,光照射を利用することとした。光照射を行うことで,通常のゲートバイアスの印加だけでは応答しない捕獲電荷を強制的に放出させることができる。MOS キャパシタでは捕獲電荷量に敏感に応答する電気特性としてキャパシタンス - 電圧測定(C-V 測定)を利用でき,光照射による電荷放出の影響,及び光遮断後の再捕獲の影響を C-V 特性の変化として高感度に検出することとした。

本研究は,ワイドギャップ半導体として 4H-SiC を評価対象とした。エピタキシャル層 ~5 µ m を有する 4H-SiC(0001)ウェハ (n型, p 型)を基板として用いた。エピ層のドープ 濃度は n 型 , p 型とも~1×10<sup>16</sup>cm<sup>-3</sup>とした。 これらの表面を 1300 , 1atm-0<sub>2</sub> 雰囲気中で 熱酸化(ドライ酸化)を行った後,一部のサ ンプルにはH<sub>2</sub>0:0<sub>2</sub>=9:1の水蒸気 - 酸素混合雰 囲気中,800 での酸化(ウェット酸化)を 30min または8hr 追加して行った。このウェ ット酸化条件では酸化レートが~0.1nm/hr と遅いため,8hr の長時間の処理を行っても 追加酸化量は<1 nm と小さく抑えられること に注意されたい。酸化後に,ゲート電極とし て Au, また基板側電極として AI を蒸着して MOS キャパシタとした。尚, Au 電極は照射光 に対して不透明であるが,200 µm の電極の 周囲の基板は露出しており,電極周囲から侵 入する光や,それの内部反射光があり,光照 射効果は容易に得ることができる。

n 型基板,p 型基板それぞれを用いて各条件で作製した MOS キャパシタに対し,まず最初に光照射をしながら強反転バイアスを印加した。光を遮断した後,蓄積側へ向けて C-V 特性(dark)を取得,蓄積側まで掃引後にすぐに掃引方向を変えて反転側へと掃引しながら C-V 特性を取得して,ヒステリシスを抽出した。このヒステリシスは,一旦光照射で放出された捕獲電荷が,その後のバイアス掃引によって埋め戻された効果を表わす。照射光は分光器で単色化しており,紫外光の照射(3.4eV)または可視光の照射(1.2~1.7eV)を使い分けて評価を行った。

#### 4.研究成果

#### (1) 遅い酸化膜中トラップの半定量的評価

3.4eV の紫外光はバンドギャップを超えるエネルギーとなるために少数キャリアがられる。この少数キャリアとの再結合が生じれる。この少数キャリアとの再結合が生じれる。この少数キャリアとの再結合域において速やかに界面捕獲電荷が減少する。光遮断後のバイアス掃引時には徐々に再捕獲がで戻す時点で戻すら出しが開始するのでは、この後引き続いてもまだ再捕獲していない。この後引き続いて蓄積側へと掃引を続けるとようやく再捕獲が完了するので、フラットバンド電圧近傍での

ヒステリシス幅は,時定数の遅い準位の効果 のみを選択的に反映している。この性質を利 用して,遅い時定数の準位に起因する電荷捕 獲量を選択的に評価することとした。

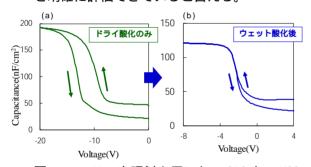

n 型基板上の MOS キャパシタでは,ドライ酸化後の C-V 特性には,dark の測定においても小さなヒステリシスがもともとみられているが,3.4eV の光照射後の特性には巨大なヒステリシスが現われ,隠れていた応答のとに捕獲電荷が大量にあることが分かる。ところが,ウェット酸化を行った試料ではこれが徐々に減少し,8hr では光照射後もヒステリシス幅が小さく抑えられ,捕獲電荷量が半分以下へ低下すると推定された。

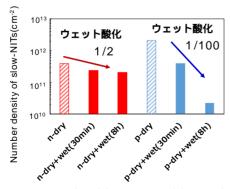

また p 型基板を用いた測定では,この効果 がさらに顕在化しており,ウェット酸化によ って2桁以上の低下が生じる。図1は,p型 基板におけるヒステリシス幅の変化を表わ している。これらのことから SiC のウェット 酸化には,遅い応答を示す欠陥準位を減少さ せる効果が強く,特に価電子帯端側にある遅 い時定数の準位がより効果的に除去される ことが分かる。このことを図2にまとめる。 以上のように, 本手法であれば, 応答の遅い (時定数の長い)捕獲電荷の総量を相対的に 評価することができる。このような遅い応答 は, 主として酸化膜中に分布の広がった欠陥 構造に帰着するのが妥当であり, MOS 界面形 成手法の違いによる界面近傍の酸化膜品質 を明確に評価できていると言える。

図1 3.4eV の光照射を用いた p-SiC 上の MOS キャパシタの C-V 特性。(a)ドライ酸化 (b) ドライ酸化後にウェット酸化の場合の結果。

図23.4eVの光照射を用いた測定から半定量的に推定される遅い時定数の電荷捕獲量の試料間の比較。p基板で酸化プロセス間の差が顕著であることは,価電子帯近傍のエネルギー領域の欠陥準位に差があることを示唆。

# (2) エネルギーの深い準位へのトラップ量の半定量的評価

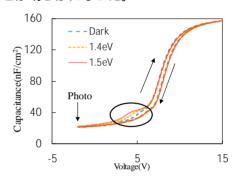

次に照射光を可視光に変えて測定を行った。この波長では少数キャリアの注入は生じないが,捕獲電荷に対する励起効果がある。この励起によって空となった準位は,光遮断後のバイアス掃引と共に埋まる過程にとは、光に出まる過程になければフラットバンド電圧に至る前に埋めないが、ヒステリシスは空乏領域ののキャパシタでの測定例である。このように生いまける捕獲電荷量を概算し,その微分値から欠陥準位密度を推定できる。

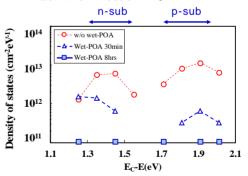

実際の試料に適用した結果を図 4 に示す。ドライ酸化の場合に比べ、ウェット酸化によってほとんど検出できないほどに低下することが明確に表れており、SiC の深いエネルギーレベルでの界面準位密度もまた、酸化プロセスによって大きく変化し得るということが明らかになった。

図 3 1.4eV~1.5eV の可視光の照射を用いた n-SiC のドライ酸化のみで作製した MOS キャパシタの C-V 特性。空乏領域に現れるヒステリシス幅の変化に着目する。

図 4 可視光の照射を用いた測定から半定量 的に推定されるエネルギー的に深い準位の 密度。ウェット酸化後は検出限界以下になる。

#### 5 . 主な発表論文等

#### 〔雑誌論文〕(計6件)

<u>Koji Kita</u> and Hironobu Kamata, "Demonstration of Large Flatband Voltage Shift by Designing Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Laminated Structures with Multiple Interface Dipole Layers", ECS

Transactions, 80 (1) 379-385 (2017), DOI: 10.1149/08001.0379ecst Jiayang Fei and Koji Kita. dipole "Opportunity of layer formation at non-SiO<sub>2</sub> dielectric interfaces in two cases: Multi-cation systems and multi-anion systems", Microelectronic Engineering, 178, 225-229 (2017).DOI: 10.1016/j.mee.2017.05.035 Koji Kita, Hirohisa Hirai, Hiroyuki Kajifusa, Kohei Kuroyama, Ishinoda, "Investigation of origins of the critically different MOS interface characteristics between dry-oxidized and wet-oxidized silicon carbide", Microelectronic Engineering, 178, 186-189 (2017), DOI: 10.1016/j.mee.2017.05.042 Jiayang Fei, Ryota Kunugi, Takanobu Watanabe and Koji Kita, "Anomalous flatband voltage shift of AIF<sub>x</sub>O<sub>y</sub>/AI<sub>2</sub>O<sub>3</sub> MOS capacitors: A consideration on dipole layer formation at dielectric interfaces with different anions", Appl. Phys. Lett. 110, 162907 (2017), DOI: /10.1063/1.4980059. Hironobu Kamata and Koji Kita, "Design of  $Al_2O_3/SiO_2$ laminated stacks with multiple interface dipole layers to achieve large flatband voltage shifts of MOS capacitors", Appl. Phys. Lett. 110, 102106 (2017), DOI: 10.1063/1.4978223. Yuki Fuiino and Koji Kita. "Estimation of Near-Interface Oxide Density SiO<sub>2</sub>/SiC Trap at Metal-Oxide-Semiconductor Interfaces by Transient Capacitance Measurements at Various Temperatures", J. Appl. Phys. 120, 085710 (2016),DOI:

#### [学会発表](計25件)

10.1063/1.4961871.

西田水輝,作田良太,平井悠久,<u>喜多浩</u>之「Photo-assisted CV 測定で評価する NIT にみる NO-POA と wet-POA 界面特性の違い」第 65 回応用物理学会春季学術講演会,3/20/2018,早稲田大学 西早稲田キャンパス(東京都・新宿区). 濱口高志 ,<u>喜多浩之</u> 「AI<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>,MgO/SiO<sub>2</sub>,MgO/AI<sub>2</sub>O<sub>3</sub> 各界面におけるダイポール起因の V<sub>FB</sub>シフトの温度依存性の違い」第 65 回応用物理学会春季学術講演会,3/18/2018,早稲田大学 西早稲田キャンパス(東京都・新宿区). Hironobu Kamata and Koji Kita,"Demonstration of a large Vfb shift induced by selectively formed multiple dipole layers in  $AI_2O_3/SiO_2$  laminated dielectric stacks," 48th IEEE Semiconductor Interface Specialists Conference (SISC2017), 12/09/2017, San Diego (USA).

Mizuki Nishida, Hirohisa Hirai and Koji Kita, "Evaluation of Deep Trap and Near-interface Oxide Trap Density at  $SiO_2/SiC$  Interface by Photo-assisted CV Measurement", 2017 International Workshop on Dielectric Thin Films for Future Electron Devices (2017 IWDTF), 11/22/2017, 東大寺カルチャーセンター (奈良県・奈良市).

Siri Nittayakasetwat and Koji Kita, "Temperatures Induced Anomalous Change in Effective Charges of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Interface Dipole Layer", 2017 International Workshop on Dielectric Thin Films for Future Electron Devices (2017 IWDTF), 11/22/2017, 東大寺カルチャーセンター (奈良県・奈良市).

平井悠久,<u>喜多浩之</u>「4H-SiC 熱酸化に伴う基板表面領域における酸素原子侵入とそれに対する酸化条件の影響」,応用物理学会先進パワー半導体分科会第4回講演会,11/02/2017,名古屋国際会議場(愛知県・名古屋市).

Koji Kita and Hironobu Kamata, "Demonstration of Large Flatband Voltage Shift by Designing Al203/Si02 Laminated Structures with Multiple Interface Dipole Layers", 232nd The Electrochemical Society (ECS) Meeting. 10/06/2017, National Harbor (USA). Hirohisa Hirai, Kei Ishinoda and Koji "Interface-Selective Low-Temperature Wet-O<sub>2</sub> Annealing to Enhance 4H-SiC (0001) MOSFET Mobility by Improving Near Interface SiO<sub>2</sub> Quality", International Conference on Silicon Carbide and Related Materials (ICSCRM 2017), 09/22/2017, Washington DC(USA).

Koji Kita, Hironobu Kamata, and Jiayang Fei, "Interface Dipole Layers between Two Dielectrics: Considerations on Physical Origins and Opportunities to Control Their 2017 Formation", International Conference on Solid State Devices and Materials (SSDM 2017), 09/20/2017. 仙 台国際センター (宮城県・仙台市). Fei Jiayang and Koji Kita, "Consideration on the interfacial dipole layer formation at non-SiO<sub>2</sub> oxide interfaces in the examples of  $HfO_2/AI_2O_3$ ",  $MgO/AI_2O_3$ and International Conference on Solid State Devices and Materials (SSDM 2017), 09/20/2017, 仙台国際センター(宮城県・仙台市).

西田水輝,<u>喜多浩之</u>「4H-SiC MOS キャパシタにおける遅い欠陥準位の光照射により観測される C-V 特性ヒステリシス解析による評価 」第78回応用物理学会秋季学術講演会,09/05/2017,福岡国際会議場(福岡県・福岡市).

Siri Nittavakasetwa. Hironobu Kamata

and Koji Kita, "Anomalous temperature dependence of dipole layer strength at the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface", 第 78 回応用物理学会秋季学術講演会, 09/05/2017,福岡国際会議場(福岡県・福岡市). 鎌田啓伸,<u>喜多浩之</u>「Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> 界面のダイポール層の生成・抑制の制御-界面の組成急峻性の与える効果-」第 78 回応 用物理学会秋季学術講演会,09/05/2017,福岡国際会議場(福岡県・福岡市).

Jiayang Fei and Koji Kita, "Opportunity of dipole layer formationat non-SiO<sub>2</sub> dielectric interfaces in two cases: multi-cation systems and multi-anion systems", 20th Conference on Insulating Films on Semiconductors (INFOS2017). 06/29/2017, Potsdom (Germany).

Koji Kita, Hirohisa Hirai, Hiroyuki Kajifusa, Kohei Kuroyama and Kei Ishinoda, "Investigation of Origins of the Critically Different MOS Interface Characteristics between Dry-oxidized and Wet-Oxidized Silicon Carbide", 20th Conference on Insulating Films on Semiconductors (INFOS2017), 06/28/2017, Potsdom (Germany).

鎌田啓伸,<u>喜多浩之</u>「AI<sub>2</sub>0<sub>3</sub>/Si0<sub>2</sub>界面のダイポール層の発現と抑制を決定づける因子の実験的検討」第64回応用物理学会春季学術講演会,03/16/2017,パシフィコ横浜(神奈川県・横浜市).

Jiayang Fei and <u>Koji Kita</u>, "Opportunity for dipole layer formation at an non-SiO<sub>2</sub> dielectric interface -  $MgO/AI_2O_3$ "第 64 回応用物理学会春季学術講演会,03/16/2017,パシフィコ横浜(神奈川県・横浜市).

<u>喜多浩之</u> 「4H-SiC MOS 界面特性の制御のための熱酸化プロセスの設計」 第 64回応用物理学会春季学術講演会 ,03/16/2017 ,パシフィコ横浜(神奈川県・横浜市).

鎌田啓伸,<u>喜多浩之</u>, "ダイポール層の 選択的発現を利用した Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> の繰り 返し構造における大きなフラットバンド 電圧シフト",応用物理学会 特別研究会 「電子デバイス界面テクノロジー研究会 材料・プロセス・デバイス特性の物理

- 」第 22 回研究会,01/20/2017,東レ総合研修センター(静岡県・三島市). 黒山 滉平,平井 悠久,山本 建策,林 真理子,<u>喜多 浩之</u>, "4H-SiCm 面ウェット酸化によるMOS 界面の電気特性と界面近傍SiO2 微視的構造の特徴の相関",応用物理学会先進パワー半導体分科会第3回講演会,11/08/2016(つくば国際会議場,つくば市).

- ② Hironobu Kamata and Koji Kita, "Design of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Laminated Stacks with Mutiple Interface Dipole Layers to Induce Large Flatband Voltage Shifts of MOS Capacitors," 2016 Int. Conf. on Solid State Devices and Materials (SSDM)), 09/27/2016, つくば国際会議場(茨城県・つくば市).

- ② Jiayang Fei, Ryota Kunugi, Takanobu Watanabe and <u>Koji Kita</u>, "Study on Dipole Layer Formation and its Origin at Al<sub>2</sub>O<sub>3</sub>/AlFxOy and Al<sub>2</sub>O<sub>3</sub>/AlNxOy Multi-anion Dielectric Interfaces by considering Anion Areal Density and Valence Differences, "2016 Int. Conf. on Solid State Devices and Materials (SSDM), 09/27/2016, つくば国際会議場 (茨城県・つくば市).

- 図 Koji Kita, "Opportunities to Design Thermal Oxidation and Post-Oxidation Processes to Control 4H-SiC MOS Interface Characteristics", 2016 Int. Conf. on Solid State Devices and Materials (SSDM), 09/28/2016, つくば国際会議場(茨城県・つくば市).

- 黒山 滉平,平井 悠久,山本 建策,林 真理子,<u>喜多 浩之</u>, "界面近傍の SiO₂ 微視的構造とMOS 界面の電気特性から見た 4H-SiC m 面のウェット酸化により形成された MOS 界面の特徴",第77回応用物理学会秋季学術講演会,09/15/2016,朱鷺メッセ(新潟県・新潟市).

- Jiayang Fei, Ryota Kunugi, Takanobu Watanabe, and <u>Koji Kita</u>, "Consideration on the Origin of Dipole Layer Formation at Dielectric Interfaces with Different Anions (Fluorine, Oxygen and Nitrogen)," 09/15/2016,第77回応用物理学会秋季学術講演会,朱鷺メッセ(新潟県・新潟市).

[その他]

研究室ウェブページ

http://www.scio.t.u-tokyo.ac.jp/index.html

### 6.研究組織

(1)研究代表者

喜多 浩之(KITA, Koji)

東京大学・大学院工学系研究科・准教授

研究者番号: 00343145

- (2)研究分担者 なし

- (3)連携研究者 なし