# 科学研究費助成事業研究成果報告書

令和 元年 6月21日現在

機関番号: 1 4 4 0 1 研究種目: 若手研究(B) 研究期間: 2016~2018

課題番号: 16K16085

研究課題名(和文)ハードウェア指向物体認識アルゴリズムとその実装方式の研究

研究課題名(英文)Hardware-oriented Algorithms and Implementation Methodology for Object Recognition

### 研究代表者

劉 載勲 (Yu, Jaehoon)

大阪大学・情報科学研究科・助教

研究者番号:70726976

交付決定額(研究期間全体):(直接経費) 2,200,000円

研究成果の概要(和文):物体認識は,計算量,ハードウェア資源,処理速度の問題から組込みシステムでの実現が困難であり,本研究ではこれらの克服に取り組んできた.その成果としてFPGA評価ボードを用いた汎用物体認識システムでは,同一認識アルゴリズムに基づく最新ハードウェアに比べて50倍以上の性能向上を実現し,歩行者検出で1080P60の動画入力に対して350 fpsの処理性能を達成した.各要素技術は5件の国際会議で発表され,そのうち国際会議A-SSCCでは交通物体認識システムを実演した.また新たなハードウェア指向特徴記述子は特許出願を行い,特徴記述子と認識処理の並列化処理機構はIEICE 学術論文誌で2件の発表を行なった.

研究成果の学術的意義や社会的意義 本研究の学術的意義としては,既存の物体認識システムの研究がアルゴリズムを中心として行われていたのとは 対照的に,システム全体のバランスを考慮したアルゴリズム,アーキテクチャ,ハードウェアの研究を行うこと によって既存研究の限界を超えた電力効率と処理性能を達成している点が挙げられる.また社会的意義として, 機械学習は今後運転補助システムや自動運転,ロボットなど幅広い組込み分野における利用が期待されており, 本研究成果はシステムアウェアな機械学習システムの設計方法などAI化社会を支えるための要素技術を提供して いる点が挙げられる.

研究成果の概要(英文): This research tackled the problems in implementing object recognition on embedded systems, which are intensive computational cost, limited hardware resources, and low processing performance. As a result, the proposed general object recognition system realized x50 faster processing performance compared with recent hardware based on the same object detection algorithm and achieved 350 fps processing performance for pedestrian detection with 1080P60 input video streams. Each core component techniques are publicized in five international conferences, and a traffic object detection system was demonstrated in A-SSCC. Also, a novel hardware-oriented feature descriptor is applied for a patent, and two papers, which are about the feature descriptor and parallel processing architecture for recognition processes, are published in IEICE Transactions.

研究分野: 機械学習、パターン認識、システムアーキテクチャ設計

キーワード: 物体認識 組込みシステム 機械学習 ハードウェア

### 様 式 C-19、F-19-1、Z-19、CK-19 (共通)

### 1. 研究開始当初の背景

画像処理に基づく物体認識は現在最も活発な研究分野の一つであり、物体認識のアルゴリズム研究は、洗練された特徴記述子と機械学習手法の登場によってここ 10 年間で目覚ましい進歩を遂げている。しかし一方で物体認識のハードウェア研究では、HOG (histograms of oriented gradients)や CoHOG (co-occurrence HOG)などの特徴記述子と SVM (support vector machine)による機械学習を用いた初期の物体認識手法の利用に留まっており、歩行者などの識別が困難な非剛体の検出においては ACF、LDCF、Spatial Pooling などの最新アルゴリズムに比べて約 30% 悪い検出ミス率を示している。物体認識のハードウェア研究とアルゴリズム研究の格差は特徴記述子の膨大な計算量と識別器の処理における複雑なメモリアクセスパターンに原因があり、その改良がハードウェア化では必須であるとの着想を得た。そこで本研究では、最新アルゴリズムの研究成果をハードウェア上で実現するために、ハードウェア指向の物体認識アルゴリズムとその実装方式について研究を行い、その有効性を示す。

### 2. 研究の目的

本研究では、最新の物体認識アルゴリズムの研究成果をハードウェアに適用し、高精度かつ高速な物体認識システムを実現することを目的とする。既存の物体認識ハードウェアの研究では、高い処理能力を達成するために効率的な数値演算の近似方法に注目していた。それに対して本研究では最先端の物体認識アルゴリズムで用いられる情報の本質を理解し、それと等価な情報を獲得でき、かつ、ハードウェアに適した物体認識アルゴリズムを新たに提案する。ここではこれをハードウェア指向の物体認識アルゴリズムと呼ぶ。さらに提案アルゴリズムに基づくハードウェア実装を行い、既存のハードウェア研究では達成できなかった高い認識精度と効率的な実装方式の両立を目指す。

### 3. 研究の方法

本研究では、最先端の物体認識アルゴリズムの一つである ACF 特徴記述子に基づく物体認識手法を解析し、その結果に基づいてハードウェア指向の物体認識アルゴリズムとその実装方式について研究を行う。まず平成 28 年度の研究では、ハードウェア指向の特徴記述子と特徴空間の正規化方法について研究し、その実装方式を検討する。次に平成 29 年度の研究では、複雑なメモリアクセスパターンを必要とする最新の識別処理とその実装方式について研究を行う。最終年度の平成 30 年度の研究では、これまでの提案手法を FPGA 上に一つのシステムとして統合し、室内及び室外環境におけるフィールドテストを実施し、システム全体の性能評価と改良を行う。

#### 4. 研究成果

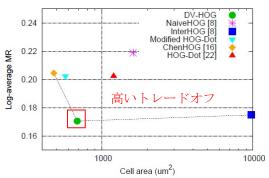

## ① 新たな特徴記述子 DV-HOG(decomposed vector histograms of oriented gradients)の考案

HOG は物体検出における形状情報の抽出に おいて多く用いられている重要な特徴記述 子である。HOG の計算には三角関数や二乗根 の計算などハードウェア実装において大量 の計算資源を必要とする演算が含まれてお り、既存ハードウェア実装において大きな足 かせとなっていた。そこで本研究では、HOG の形状情報を損なうことなく低ハードウェ ア資源で実装可能な DV-HOG を考案した。 DV-HOG は線形代数に基づく特徴記述子であ り、ACF を用いた歩行者研究室において他の HOG を上回る低いミスレート(MR)を達成して いる(右表)。さらにハードウェア実装におけ る回路面積とミスレートのトレードオフの 評価においても他の HOG 実装を凌駕している (右図)。これにより物体検出精度の劣化な くハードウェア実装における回路面積を 14 分の1に減らすことに成功している。本成果

| Method                                | Log-avg. | Diff. from |  |

|---------------------------------------|----------|------------|--|

|                                       | MR       | Table 4    |  |

| ACF-Exact [5] + DV-HOG (INT)          | 17.06%   | +0.82%     |  |

| ACF-Exact [5] + InterHOG [8] (INT)    | 17.49%   | -0.41%     |  |

| ACF-Exact [5] + $HOG$ -Dot [22] (INT) | 20.24%   | +2.67%     |  |

| ACF-Exact [5] + ChenHOG [16] (INT)    | 20.45%   | -0.97%     |  |

| ACF-Exact [5] + NaiveHOG [8] (INT)    | 21.88%   | +1.28%     |  |

は IEICE の学術論文誌で発表しており、1件の特許出願を行っている。

### ② ブースティング決定木の並列処理アーキテクチャと回路設計

ブースティング決定木は低計算量で高い推論性能を発揮できることから組込みシステムにおける利用が期待されている。しかしハードウェア実装においては各決定木が入力データによって異なったメモリアクセスを必要とするため、その並列実装が困難であった。そこで本研究では、ブースティング決定木の処理におけるメモリ競合を解消し、高い並列処理を実現するためのアルゴリズムとアーキテクチャを考案し、そのハードウェア設計を行った。提案手法はタスクスケジューリングと予測投機に基づき、並列処理を行う決定木の動作を同期させることによ

って高い並列度を実現した。その結果、提案ハードウェア実装は他の最新ハードウェア実装に 比べて 50 倍から 100 倍以上の処理性能を達成している。本成果は IEICE の学術論文誌で発表さ れている。

| Method Platform | Platform | Image size                       | Window size                      | Scale step         | Pixel step         | fps          | #window/sec. |           |

|-----------------|----------|----------------------------------|----------------------------------|--------------------|--------------------|--------------|--------------|-----------|

| Method          | Tuttorin | $W_{\rm img} \times H_{\rm img}$ | $W_{\rm win} \times H_{\rm win}$ | $S_{\text{scale}}$ | $S_{\text{pixel}}$ | $N_{ m fps}$ | $N_{ m wps}$ |           |

| ACF [10]        | CPU      | 640×480                          | $48 \times 96$                   | 21/8               | 4                  | 31.9         | 2,181k       | (1/105.0) |

| ACF [11]        | FPGA     | 640×480                          | $32 \times 64$                   | 21/6               | 4                  | 30           | 1,972k       | (1/116.1) |

| DPM [8]         | ASIC     | $1,920 \times 1,080$             | $64 \times 128$                  | $2^{1/3}$          | 8                  | 60           | 3,975k       | (1/57.6)  |

| Ours            | FPGA     | $1,920 \times 1,080$             | $48 \times 96$                   | $2^{1/8}$          | 4                  | 350          | 229,079k     | (1.0)     |

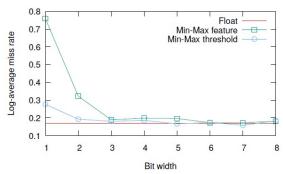

### ③ ブースティング決定木における量子化手法の考案

ブースティング決定木をハードウェア 実装において処理に必要な計算精度はハ ードウェア規模に直接影響する重要なフ ァクターである。そこで本研究では、決定 木の処理が大小比較のみに依存すること に着目し、精度劣化を抑えた量子化手法を 提案した。その結果、2 ビットの固定小数 点を用いたブースティング決定木でもそ の精度劣化を 2%未満に抑えることのでき る量子化手法を実現している(右図)。提 案手法を用いることでハードウェア実装 におけるメモリ容量の要求を 16 分の 1 に 減らすことが可能となり、組込みシステム における実装効率を大幅に改善すること ができた。本成果は国際ワークショップ SISAで発表されている。

| Method   | Representation | Bit width | Memory usage |

|----------|----------------|-----------|--------------|

| ACF [12] | Floating point | 32        | 39.6 Mbit    |

| Proposed | Fixed point    |           | 2.47 Mbit    |

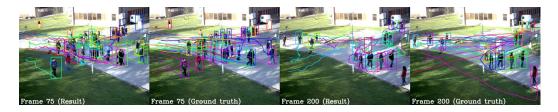

### ④ ハードウェア向け物体追跡手法の考案

物体追跡は物体検出と共に認識処理におけるコア技術であり、物体追跡と検出の効率的な融合は組込みシステムにおける実装効率に大きな影響を及ぼす。その効率的な融合のために本研究では、ブースティング決定木を用いた検出処理から得られる情報を再利用して物体の追跡を行う手法を考案した。提案手法は追跡のための処理を別途実装する必要がなく、高い追跡精度を達成した(下図)。本研究成果は、国際会議 ITC-CSCC で発表を行っている。

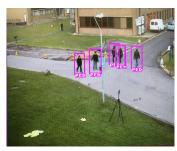

### ⑤ FPGA 実装による交通物体認識システムの構築

本研究では、上記の研究成果を用いて汎用的な物体認識システムを構築し、FPGA 評価ボードを用いて処理性能と回路規模の検証を行った。FPGA 実装では歩行者検出に対して 1080P60 の Full HD 動画入力に対して 170 fps の処理性能を、車、歩行者、信号機など 6 種類の交通物体を対象とした多クラス検出では 78 fps の処理性能を達成し、既存のハードウェア実装を大きく凌駕する結果となった(下図)。本研究成果は、国際会議 A-SSCC で発表されている。

### 5. 主な発表論文等

### 〔雑誌論文〕(計2件)

- 1. Koichi Mitsunari, Yoshinori Takeuchi, Masaharu Imai, and <u>Jaehoon Yu</u>, "Decomposed Vector Histograms of Oriented Gradients for Efficient Hardware Implementation," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 查読有, E101. A, 2018, pp. 1766-1775

- DOI: 10.1587/transfun. E101. A.1766

- 2. Koichi Mitsunari, <u>Jaehoon Yu</u>, Takao Onoye, and Masanori Hashimoto, "Hardware Architecture for High-Speed Object Detection Using Decision Tree Ensemble," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 查読有, E101. A, 2018, pp. 1298-1307

### DOI: 10.1587/transfun. E101. A.1298

### 〔学会発表〕(計5件)

- 1. Koichi Mitsunari, <u>Jaehoon Yu</u>, and Masanori Hashimoto, "Hardware Architecture for Fast General Object Detection Using Aggregated Channel Features," IEEE Asian Solid-State Circuits Conference, 2018

- Eric Aliwarga, Koichi Mitsunari, <u>Jaehoon Yu</u>, Takao Onoye, Toshitaka Azuma, and Mitsuhiko Koga, "System Design of Vision-based Framework for Senior Driver Assistance," Workshop on Synthesis And System Integration of Mixed Information technologies, 2016

- 3. Koichi Mitsunari, and <u>Jaehoon Yu</u>, "Influence of Numerical Precision on Machine Learning and Embedded Systems," International Workshop on Smart Info-Media Systems in Asia, 2016

- 4. Koichi Mitsunari, <u>Jaehoon Yu</u>, Yoshinori Takeuchi, and Masaharu Imai, "Object Tracking based on Path Similarity of Boosted Decision Trees Inproceedings," International Technical Conference on Circuits/Systems, Computers and Communications, 2016

- 5. Mitsuhiko Koga, Takao Onoye, <u>Jaehoon Yu</u>, Toshitaka Azuma, and Eric Aliwarga, "Vision-based Comprehensive Framework for Senior Driver Assistance," European Congress and Exhibition on Intelligent Transport Systems and Services, 2016

# 〔図書〕(計 件)

### 〔産業財産権〕

○出願状況(計1件)

名称: 勾配方向ヒストグラム生成装置及び勾配方向ヒストグラム生成方法

発明者:劉載勲,光成浩一,武内良典,今井正治

権利者:大阪大学 種類:特許

番号: 特願 2017-127405

出願年:2017 国内外の別:国内

### ○取得状況(計 件)

名称: 発明者: 権類: 種号: 番号に: 取内外の別:

〔その他〕

ホームページ等

- 6. 研究組織

- (1)研究分担者

研究分担者氏名:

ローマ字氏名:

所属研究機関名:

部局名:

職名:

研究者番号(8桁):

(2)研究協力者

研究協力者氏名:尾上 孝雄 ローマ字氏名: Takao Onoye

研究協力者氏名:武内 良典

ローマ字氏名: Yoshinori Takeuchi

※科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。