#### 研究成果報告書 科学研究費助成事業

今和 2 年 7 月 1 7 日現在

機関番号: 21602 研究種目: 若手研究(B) 研究期間: 2017~2019

課題番号: 17K12661

研究課題名(和文)遅延ばらつき・経年劣化に耐性を持つ集積回路設計技術の開発

研究課題名(英文) Development of Design Methodology for LSI Circuits with Tolerance for Delay Variation and Aging

#### 研究代表者

小平 行秀 (Kohira, Yukihide)

会津大学・コンピュータ理工学部・上級准教授

研究者番号:00549298

交付決定額(研究期間全体):(直接経費) 3.100.000円

研究成果の概要(和文):本研究では,製造後に遅延値を変更できる素子(PDE)をクロック回路に挿入することで,遅延ばらつきや経年劣化による誤動作から回路を回復させる機構を持つ,信頼性の高い集積回路の設計支援システムの開発を行った.従来のPDEを挿入した設計手法と比較して消費電力を削減するために,新たにPDEの構造を提案し,PDEを削減するためのクラスタリング手法を提案した.また,従来手法から設計手順を見直すことで,設計時間を100倍程度高速化した.計算機実験において,従来のクロック同期方式の回路と比較したところ,面積や消費電力の増加を抑えつつ,歩留まりが改善されることを確認した.

研究成果の学術的意義や社会的意義PDEにより各記憶素子に供給されるクロックタイミングを調整することで回路を誤動作から回復させることができるため,本研究によりLSIの設計技術の信頼性の向上に貢献した.また,設計に掛かる時間を既存研究より100倍程度高速化したことで,大規模な回路への適用の可能性が高まり,実用性を向上した.なお,開発した設計支援システムは,アプリケーションを限定していないため,どのようなアプリケーションに対しても高信頼な集積回路を実現できることが期待される.

研究成果の概要(英文): In this research, we developed a design automation system to realize LSI circuits with high reliability to which Programmable Delay Elements (PDEs) are inserted and in which malfunction due to delay variation and aging can be recovered. To reduce power consumption compared with existing design methods for PDE insertion, we proposed a new structure of PDEs and a clustering method which reduces the number of inserted PDEs. Moreover, the design time of the proposed method was about 100 times faster than that of an existing method by modifying the design processes. In computational experiments, the yield was improved and the overheads of the circuit area and the power consumption were restrained, compared with the existing method.

研究分野: 集積回路設計自動化

キーワード:集積回路設計自動化 遅延ばらつき 経年劣化 歩留まり改善 遅延調整可能素子

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。

## 1.研究開始当初の背景

LSI の微細加工技術の進歩により、回路の動作速度の向上、消費電力の削減などの集積回路の性能の向上が進んでいる一方、LSI の製造の困難さが増している。また、LSI の微細化に伴う物理現象が顕在化しており、製造される LSI の性能の不確実さが増加している。この不確実さの代表的なものとして、遅延ばらつきと経年劣化がある。近年、自動車など、長期間利用され、かつ人の生命に関わる幅広い分野で LSI の利用が進められており、遅延ばらつきと経年劣化に対して耐性を持つ、高信頼な集積回路の設計技術の開発が望まれている。

## 2.研究の目的

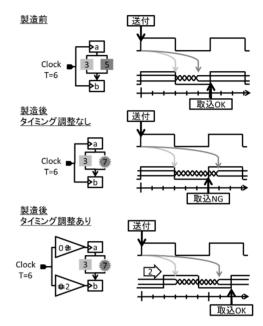

本研究では,製造後に遅延値を変更できる素子(Programmable Delay Element: PDE)をクロック木に挿入することで,誤動作から回路を回復させる機構を持つ集積回路の設計手法に焦点を当てた(図 1). PDE の消費電力を低減し, PDEをクロック木に挿入することで,遅延ばらつき・経年劣化に耐性を持つ集積回路の設計支援システムを開発することを目的として設定した.具体的には,PDE の構造,PDE の挿入箇所について検討し,挿入する PDE の消費電力を下げることで PDE を挿入するコストを下げることを目指した.

## 3.研究の方法

研究開始当初は,本研究の目的を達成するために,(1)PDE の構造を見直し,(2)複数の記憶素子に対して1 つの PDE を挿入するようにクラスタリングを行う,という2つの手法を適用することを計画した.さらに,当初の計画にはなかったが,(3)設計時間を短縮するための設計フローの見直しを行うことで,大規模な回路への適用が可能となり,実用性を向上させることを目指した.

図1: クロック同期方式のタイミング チャート・クロックタイミングを調整できる素子(PDE)を持つ場合,遅延ばらつきへの耐性が高い.

## 4. 研究成果

#### (1) PDE の構造

2017 年度の研究において, PDE の構造について検討を行った.既存の PDE では,選択される遅延値によらず, PDE の入力の信号がスイッチングすると PDE 内の全ての回路素子が必ずスイッチングするため,余分な動的電力が消費された.そこで本研究では,デマルチプレクサを利用した PDE の構造を提案した.この構造により,選択されない遅延値の回路素子はスイッチングしないので,従来の PDE よりも動的消費電力が減少する.計算機実験により,35 回路の平均で 55.7% の消費電力が削減されることを確認した.

## (2) クラスタリング手法

2017 年度の研究において,挿入する PDE の個数をクラスタリング手法により削減する手法について検討を行った.既存の研究では,全ての記憶素子に対して1つの PDE を挿入したため,面積と消費電力のオーバーヘッドが大きくなった.そこで本研究では,クロック木の最終段のクロックバッファからクロックが供給される複数の記憶素子を1つのクラスタにまとめ,1つのクラスタに対して1つの PDE を挿入することで挿入する PDE の個数を減少させるクラスタリング手法を提案した.提案手法は,与えられた目標の PDE 数を満たすクラスタリングを得る.計算機実験では,挿入する PDE の個数を25%に削減すると,多少歩留まりの改善率が低下するものの,35回路の平均で40%の回路面積と22.3%の消費電力が削減されることを確認した.

また 2019 年度には ,最終段以外のクロック木の構造も変更するクラスタリング手法を提案した .この提案手法では小規模な回路でも歩留まりを向上することができたが ,特に大規模な回路において ,既存のクラスタリング手法と比較し ,歩留まりの向上と消費電力の削減が実現された .

#### (3) 設計フローの見直し

2017 年度で検討したクラスタリング手法を用いるためには,計算時間が長いゲートレベルでのモンテカルロシミュレーションを実行し,PDE の遅延の調整量をあらかじめ予測する必要があ

るため、大規模な回路に対してこの手法を適用するのは現実的ではない.そこで2018年度と2019年度において、ゲートレベルでのモンテカルロシミュレーションを用いずに、市販のEDAツールによって統計的静的遅延解析を実行し、得られたばらつき予測を元に記憶素子間でのモンテカルロシミュレーションを実行することで、計算時間を削減する手法の検討を行った.既存のゲートレベルでのモンテカルロシミュレーションと比較し、100倍程度の高速が実現された.

## 5 . 主な発表論文等

「雑誌論文】 計1件(うち査読付論文 1件/うち国際共著 0件/うちオープンアクセス 0件)

| 「一根心神久」 「「「「」」」「「」」」「「」」」「「」」」「「」」「「」」「「」」「「」 |  |  |  |  |

|-----------------------------------------------|--|--|--|--|

| 4 . 巻                                         |  |  |  |  |

| E102.A                                        |  |  |  |  |

|                                               |  |  |  |  |

| 5 . 発行年                                       |  |  |  |  |

| 2019年                                         |  |  |  |  |

|                                               |  |  |  |  |

| 6.最初と最後の頁                                     |  |  |  |  |

| 894 ~ 903                                     |  |  |  |  |

|                                               |  |  |  |  |

|                                               |  |  |  |  |

| 査読の有無                                         |  |  |  |  |

| 有                                             |  |  |  |  |

|                                               |  |  |  |  |

| 国際共著                                          |  |  |  |  |

| -                                             |  |  |  |  |

|                                               |  |  |  |  |

## 〔学会発表〕 計5件(うち招待講演 0件/うち国際学会 2件)

## 1.発表者名

Kota MUROI, Yukihide KOHIRA

## 2 . 発表標題

Clustering for Reduction of Power Consumption and Area on Post-Silicon Delay Tuning

## 3 . 学会等名

The 7th IEEE International Symposium on Next-Generation Electronics (ISNE 2018) (国際学会)

4 . 発表年 2018年

#### 1.発表者名

青木誠孝 , 小平行秀

# 2 . 発表標題

一般同期方式における低電力化のための多電源回路の設計フロー

## 3 . 学会等名

電子情報通信学会VLD研究会

4.発表年

2019年

## 1.発表者名

室井孝太 , 小平行秀

## 2 . 発表標題

製造後遅延調整における面積削減のための遅延調整素子

## 3 . 学会等名

平成29年度 電気関係学会 東北支部連合大会

4 . 発表年

2017年

| 1 . 発表者名                          |

|-----------------------------------|

| 室井孝太,小平行秀                         |

|                                   |

|                                   |

|                                   |

| 2.発表標題                            |

| 製造後遅延調整における面積と消費電力の削減ためのクラスタリング手法 |

|                                   |

|                                   |

|                                   |

|                                   |

| 3.学会等名                            |

| 3.学会等名<br>電子情報通信学会VLD研究会          |

| 電子情報通信学会VLD研究会                    |

|                                   |

| 電子情報通信学会VLD研究会                    |

1.発表者名

Kora MUROI, Yukihide KOHIRA

2 . 発表標題 Clock Tree Modification for Circuits with Programmable Delay Elements

## 3 . 学会等名

The 22nd Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI 2019)(国際学会)

4 . 発表年 2019年

〔図書〕 計0件

〔産業財産権〕

〔その他〕

6 斑恋纲绘

| 6 . | . 研究組織                    |                       |    |

|-----|---------------------------|-----------------------|----|

|     | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |