# 科学研究費助成事業 研究成果報告書

令和 2 年 6 月 4 日現在

機関番号: 13901

研究種目: 挑戦的研究(萌芽)

研究期間: 2017~2019

課題番号: 17K19975

研究課題名(和文)フォトニクスとエレクトロニクスの融合による光コンピュータの構成法に関する研究

研究課題名(英文)A Study on Optical Computer Design through Photonics and Electronics Co-Optimization

#### 研究代表者

石原 亨(Ishihara, Tohru)

名古屋大学・情報学研究科・教授

研究者番号:30323471

交付決定額(研究期間全体):(直接経費) 4,900,000円

研究成果の概要(和文):本研究課題は、光を情報担体としてネットワーク内で高速計算を行う光コンピューティング技術の開発を目的とする。この目的のために、光並列加算器、光並列乗算器、光ニューラルネットワークなど、いくつかの光演算ユニットを開発した。単一の光デバイスの遅延は1ピコ秒未満であるため、光デバイスを回路構成要素として使用することにより、算術演算の計算速度をピコ秒のオーダーに抑えることができる。この超低遅延が、光デバイスを光回路合成に使用する根本的な動機である。光回路の消費電力を削減するいくつかの重要な技術の開発も行った。光電子回路シミュレーションにより、回路の光速動作を実証した。

研究成果の学術的意義や社会的意義 あらゆるものがインターネットに接続されるIoTの時代が到来し、第5世代通信(5G)技術が実用化されようと している。5G以降の6Gや7Gにおいては、あらゆるものが超低遅延で通信するための技術が必須となる。例 えば遠隔医療や自動運転車同士の通信には超低遅延演算が最重要技術となる。本研究課題は、光の速度で演算を

行う光コンピューティングの基礎設計技術を世界に先駆けて開発した。産業的にも学術的にもその意義は大きい。

研究成果の概要(英文): This project is focused on an in-network optical computing. We have developed several optical functional units such as parallel adders, parallel multipliers and optical neural networks. With the optical devices as circuit building blocks, the computational speed of the arithmetic functions is on the order of picosecond since the delay of the single optical device is less than one picosecond. This ultra-low-latency is the basic motivation of using the optical devices for the optical circuit synthesis. Several key techniques for reducing the power consumption of optical circuits have been also developed. With optoelectronic circuit simulation, we have demonstrated the light speed operation of the circuits.

研究分野: 情報工学

キーワード: 計算機システム 光コンピューティング 光集積回路

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。

# 様 式 C-19、F-19-1、Z-19(共通)

# 1.研究開始当初の背景

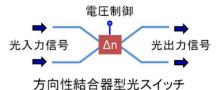

高性能かつ省エネルギーな集積回路(以下 LSI )は高度な情報社会を担うキーデバイスである。今日の LSI は、処理性能を向上させるためにチップサイズや素子サイズを極限まで小さくする 工夫がなされている。しかし ,回路プロックや論理素子をつなぐための金属配線が信号伝播遅延 のさらなる削減を制限する要因となり、今日の LSI の高速化に限界が見えつつある。一方 , LSI 技術とともに情報通信技術を支えている光技術は近年目覚ましい発展を遂げている。既に実現されているインターネット通信やデータセンタなどのノード間通信だけでなく、プロセッサチップ間や CPU 間の通信も光技術によって実現されようとしている。しかし、今日実用化されている光配線や光スイッチのサイズは LSI 中の論理ゲートと比べて 6 桁から 8 桁程度大きいため、光スイッチを LSI のように高集積化することは困難であった。超微小空間で光を制御する技術が存在しなかったためである。しかし、2000 年代に入りフォトニック結晶に代表されるナノフォトニクス技術が急速に発展し、光スイッチを数ミクロンまで小型化することが可能となった。これにより、光スイッチの素子遅延を CMOS 論理ゲートの 1/100~1/50 にできる目処がたちつつある。また、光スイッチの消費エネルギーは飛躍的に改善され、CMOS 論理ゲートと同程度になりつつある。以上の理由により、ナノフォトニクス技術は、未来の光集積回路の基盤技術として近年急速に注目されつつある。

# 2.研究の目的

本研究課題は、今日の高性能コンピュータを実現するエレクトロニクス技術と高速通信を担うフォトニクス技術を有機的に融合させることによって全く新しい光コンピュータの構成法を開拓するものである。光スイッチや光配線等のフォトニクス技術は今日の高速通信技術を支える必須技術であるが、これらの技術を"通信"ではなく"演算処理"に応用する研究はほとんど行われていないのが現状である。今日実用化されている光配線や光スイッチのサイズは集積回路(以下LSI)中の論理ゲートと比べて6桁から8桁程度大きいため、光スイッチの高集積化が

極めてある。2000年からし、2000年からは、されるでは、されるけんでは、されるけんでは、からないは、されるけんがある。

旧来の光スイッチ: サイズ・遅延とも大素子長=10mm、伝搬遅延時間=100ps

ナノフォトニクスに基づく光スイッチ: 素子長=100 µm、伝搬遅延時間=1ps

ォトニクス技術が急速に発展し、光スイッチを超小型化することが可能になりつつある。上図に示すとおり、従来は数 cm 程度の素子長が必要であった光スイッチは、フォトニック結晶を用いることにより光の波長の数倍程度(3~5μm)まで小型化できるため、光スイッチの信号伝搬時間を 100 fs 程度まで小さくできる目途が立ちつつある。これは、従来型 LSI による論理ゲートの伝播遅延時間の 1/100~1/50 の遅延時間である。本研究課題は、今日の高性能コンピュータを実現するデータ処理機能の中で光スイッチに適した処理機能を見極め、その機能を光スイッチに基づく論理回路で実現することにより、超高速データ処理技術を確立することが目的である。従って、LSI 中の全ての論理ゲートを光スイッチで置き換えることが目的ではない。

#### 3.研究の方法

ナノフォトニクス技術を単純に LSI に導入するだけでは LSI の高速化は望めない。光スイッチ素子の信号遅延は、状態を変化させるためのスイッチング遅延と信号を通過または遮断する

ためのパス遅延に分類できる。光スイッチ素子のパス遅延は LSI の構成要素である CMOS 論理ゲ

ートと比べ て 1/100~

シリアル接続が得意 (光の速度で伝搬可能) カスケード接続は不得意 (光電変換とスイッチング遅延)

1/50 倍程度 と非常に小 さいが、スイ

ッチング遅延は CMOS ゲートより 2 倍程度大きい。つまり、上図の左に示したように、光スイッチのシリアル接続で回路を構成すれば CMOS 論理回路よりも数十倍高速な回路が構成できるが、上図の右に示したようにカスケード接続により回路を構成すると CMOS 論理回路よりも低速となる。そこで本研究では、コンピュータアーキテクチャおよびその設計技術分野で培った知識を最大限活用し以下の計画で研究を実施した。

- 1. コンピュータの構成要素の中で光スイッチに適した要素と不適な要素を明らかにする。

- ◆ 一部の算術演算が光スイッチに適していることを確認しているが、より詳細に分類する。

- 2. 上記解析で明らかにする構成要素に対して光電融合回路に適した回路構造を明らかにする。

- ◆ 平成 26 年より NTT 物性科学基礎研究所と光スイッチに関する共同研究を開始している。当該研究所が開発中の光スイッチの特性モデルと既存の CMOS 論理ゲートの特性モデルに基づいて光電融合回路に適した回路構造を明らかにし、両モデルを用いた光電融合回路を設計する。

- 光電融合回路シミュレータによる評価を行ない光電融合回路の得失を明らかにする。

- ◆ カナダの Optiwave 社が開発した回路シミュレータによって光スイッチと CMOS 論理ゲート が混載する光電融合回路をシミュレーション可能である。このシミュレータを最大限活用 する。

上記の研究により、応募者の専門分野であるディジタル LSI 設計分野 (エレクトロニクス)とナノフォトニクス研究分野を有機的に融合させる新たな学術分野を開拓する。

### 4. 研究成果

平成 29 年度は二分決定グラフに基づく光論理回路の構成法を検討した。二分決定グラフに基づいて光論理回路を構成すると光スイッチの直列接続のみで回路を構成できる。つまり、二分決定グラフに基づく光論理回路は非常に高速に動作することが期待できる。しかし、二分決定グラフに基づく論理回路は実現する論理関数によっては必要とする素子数が入力の指数オーダーとなることが分かっている。つまり、実現する論理関数によっては二分決定グラフに基づく論理回路の面積が膨大になる可能性がある。この場合、光の信号を出力まで伝えるための電力も膨大となり現実的ではない。そこで、平成 29 年度は二分決定グラフに基づく光論理回路の素子数と光の減衰を低減するための方法を検討し、いくつかの興味深い設計最適化手法を発案した。並列カウンタや並列乗算器などの例を用いた実験により、発案した方法が素子数削減に有効であることを確認した。上記の結果は、集積回路設計技術に関する研究会にて発表した。

平成 30 年度は光論理回路の低消費電力化手法に関する検討を行った。二分決定グラフに基づく光論理回路における光信号の減衰率に関して詳細な解析を行った結果、光論理回路に入射される光信号の減衰は論理回路の入力変数の数の指数関数となることが明らかになった。光論理回路は、光スイッチを直列に接続することで高速に信号を伝搬させることができるが、光スイッチを伝搬する信号の減衰は、光スイッチの直列段数の指数に比例する。従って、直列に接続される光スイッチの数が多くなれば、光源に強い光信号を用いる必要があり、光集積回路全体の消費

電力が膨大となる。そこで、平成30年度は光集積回路の光の減衰を低減する回路設計手法を考案し、並列乗算器などを対象として手法の効果を検証した。また、二分決定グラフに基づく回路は、最悪の場合では素子数が入力数の指数に比例して大きくなる問題がある。そこで、本年度は光の波の性質を利用し、波長分割多重により一つの回路を複数の論理関数で共有する手法を考案した。さらに、並列乗算に適切な近似を導入することにより、光集積回路に適した回路アーキテクチャが構成できることを明らかにした。具体的には、2変数の積が、これらの変数の対数の和に置き換えられることに注目し、2変数の対数値を導出する際に適切な近似を導入することにより、回路の大部分を光スイッチの直列接続によって構成する並列乗算器のアーキテクチャを明らかにした。これらの研究成果は国内外の会議で発表した。

平成 31 年度は、平成 29 年度と 30 年度に行った研究の成果を発展させ、一般的な論理関数を 光デバイスによって実現する光論理回路の低消費電力化手法と光ニューラルネットワークのア ーキテクチャを考案した。平成30年度に行った研究で明らかにしたとおり、光論理回路は非常 に高速である反面、二分決定グラフを直接的に光デバイスで実現すると光源が消費する電力は 入力変数の数の指数オーダーとなる。そこで、光論理回路を適切に多段化することにより、光源 が消費する電力を入力変数の数の指数オーダーから多項式オーダーに低減する手法を開発した。 この手法により、光論理回路の消費電力を既存の CMOS 論理回路と同程度に保ちつつ、遅延性能 は CMOS 論理回路のおよそ 3 倍程度に向上させることができることを明らかにした。さらに、光 スイッチを用いたニューラルネットワーク回路アーキテクチャを幅広く調査し、特徴を整理し た。代表的な光ニューラルネットワークアーキテクチャは MIT の研究グループが開発した MIT 型 と Princeton 大学が開発した Princeton 型の 2 種類に大別できることを明らかにした。MIT 型 は、マッハツェンダ干渉計を格子状に配置して超低遅延推論を実現する。Princeton 型は、リン グ変調器によるアナログ乗算器と光受光器によるアナログ累算器を組み合わせることにより小 面積な光回路で推論処理を実現する。本研究課題では、MIT型でも Princeton 型でもない新たな 光二ューラルネットワークアーキテクチャを考案し、光回路シミュレータによりその有効性を 明らかにした。本研究課題で新たに提案した光ニューラルネットワークアーキテクチャは、光の 波長分割多重技術を用いて、光積和演算を並列化する。 具体的には 100 種類の波長の光を用いて ベクトル行列積演算を 100 並列で実行する。 この技術により、一つの光積和演算器で 100 種類の 積和演算を並列に実行できることが明らかにした。演算のスループットを向上できるだけでな く、面積効率をおよそ100倍に向上できる。これらの研究成果は国内外の会議で発表した。

#### 5 . 主な発表論文等

「雑誌論文 〕 計2件(うち査読付論文 2件/うち国際共著 0件/うちオープンアクセス 0件)

| 「無誌論又」 計2件(つら直流1)論又 2件/つら国際共者 0件/つらオーノノアクセス 0件)                         |               |

|-------------------------------------------------------------------------|---------------|

| 1 . 著者名                                                                 | 4 . 巻         |

| Ishihara Tohru, Shinya Akihiko, Inoue Koji, Nozaki Kengo, Notomi Masaya | 14            |

| 2.論文標題                                                                  | 5.発行年         |

| An Integrated Nanophotonic Parallel Adder                               | 2018年         |

|                                                                         | 6.最初と最後の頁     |

| ACM Journal on Emerging Technologies in Computing Systems               | 1~20          |

|                                                                         |               |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                 | <u></u> 査読の有無 |

| 対象単元開文のかけ (プラグルオフラエット nax が)                                            | 有             |

|                                                                         |               |

| オープンアクセス                                                                | 国際共著          |

| オープンアクセスではない、又はオープンアクセスが困難                                              | -             |

| 1.著者名                                                                                   | 4 . 巻               |

|-----------------------------------------------------------------------------------------|---------------------|

| MATSUO Ryosuke、SHIOMI Jun、ISHIHARA Tohru、ONODERA Hidetoshi、SHINYA Akihiko、NOTOMI Masaya | E102.A              |

| 2.論文標題                                                                                  | 5 . 発行年             |

| Methods for Reducing Power and Area of BDD-Based Optical Logic Circuits                 | 2019年               |

| 3 . 雑誌名                                                                                 | 6.最初と最後の頁           |

| IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences | 1751 ~ 1759         |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                                 | <u> </u><br>  査読の有無 |

| https://doi.org/10.1587/transfun.E102.A.1751                                            | 有                   |

| オープンアクセス                                                                                | 国際共著                |

| オープンアクセスではない、又はオープンアクセスが困難                                                              | -                   |

# [学会発表] 計11件(うち招待講演 4件/うち国際学会 7件)

1.発表者名

Tohru Ishihara, Jun Shiomi, Naoki Hattori, Yutaka Masuda, Akihiko Shinya, and Masaya Notomi

2 . 発表標題

An Optical Neural Network Architecture based on Highly Parallelized WDM-Multiplier-Accumulator

3 . 学会等名

IEEE/ACM Workshop on Photonics-Optics Technology Oriented Networking, Information and Computing Systems (招待講演) (国際学会)

4 . 発表年 2019年

1.発表者名

Tohru Ishihara

2 . 発表標題

Nanophotonic Circuit Design based on Binary Decision Diagram

3 . 学会等名

EMN Milan Meeting on Photonics (招待講演) (国際学会)

4.発表年

2019年

| 1 | . 発表者名 |  |  |  |  |

|---|--------|--|--|--|--|

|   |        |  |  |  |  |

Jun Shiomi, Tohru Ishihara, Hidetoshi Onodera, Akihiko Shinya, and Masaya Notomi

# 2 . 発表標題

Integrated Optical Neural Networks Exploiting Light Speed Approximate Parallel Multipliers

#### 3.学会等名

5th International Workshop on Optical/Photonic Interconnects(招待講演)(国際学会)

# 4 . 発表年

2019年

#### 1.発表者名

Ryosuke Matsuo, Jun Shiomi, Tohru Ishihara, Hidetoshi Onodera, Akihiko Shinya, Masaya Notomi

#### 2 . 発表標題

BDD-based Synthesis of Optical Logic Circuits Exploting Wavelength Division Multiplexing

### 3.学会等名

Asia and South Pacific Design Automation Conference (国際学会)

# 4 . 発表年

2019年

#### 1.発表者名

Jun Shiomi, Tohru Ishihara, Hidetoshi Onodera, Akihiko Shinya, Masaya Notomi

#### 2 . 発表標題

An Integrated Optical Parallel Multiplier Exploiting Approximate Binary Logarithms towards Light Speed Data Processing

#### 3.学会等名

IEEE International Conference on Rebooting Computing (国際学会)

#### 4.発表年

2018年

### 1.発表者名

Takumi Egawa, Tohru Ishihara, Hidetoshi Onodera, Akihiko Shinya, Shota Kita, Kengo Nozaki, Kenta Takata, Masaya Notomi

#### 2 . 発表標題

Multi-Level Optimization for Large Fan-In Optical Logic Circuits using Integrated Nanophotonics

# 3.学会等名

IEEE International Conference on Rebooting Computing (国際学会)

# 4.発表年

2018年

| 1. 発表者名                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------|

| Jun Shiomi, Tohru Ishihara, Hidetoshi Onodera, Akihiko Shinya, and Masaya Notomi                                      |

|                                                                                                                       |

| 2.発表標題                                                                                                                |

| A Light Speed Optical Approximate Parallel Multiplier and Its Applications                                            |

|                                                                                                                       |

|                                                                                                                       |

| 3.学会等名<br>Workshop on Photonics-Optics Technology Oriented Networking, Information, and Computing Systems(招待講演)(国際学会) |

| workshop on Photonics-Optics Technology Offented Networking, Information, and Computing Systems(指行論,與)(国际子云)          |

| 4 . 発表年                                                                                                               |

| 2018年                                                                                                                 |

| 1.発表者名                                                                                                                |

| 服部直樹,増田豊,石原亨,塩見準,新家昭彦,納富雅也                                                                                            |

|                                                                                                                       |

|                                                                                                                       |

| 2 . 発表標題<br>ニューラルネットワークの集積ナノフォトニクス実装に適した回路構造探索                                                                        |

| ニューンパーシーンの未扱ングンは「ニンバス状に足らに口頭間に派派                                                                                      |

|                                                                                                                       |

| 3 . 学会等名                                                                                                              |

| 電子情報通信学会VLSI設計技術研究会                                                                                                   |

| 4.発表年                                                                                                                 |

| 2020年                                                                                                                 |

| 1.発表者名                                                                                                                |

| 松尾亮祐、塩見凖、石原亨、小野寺秀俊、新家昭彦、納富雅也                                                                                          |

|                                                                                                                       |

|                                                                                                                       |

| 2 . 発表標題                                                                                                              |

| BDDに基づく光論理回路の素子数削減と消費電力低減                                                                                             |

|                                                                                                                       |

| 3.学会等名                                                                                                                |

| 3.字云寺石<br>電子情報通信学会VLSI設計技術研究会                                                                                         |

|                                                                                                                       |

| 4.発表年<br>2019年                                                                                                        |

| 2010 1                                                                                                                |

| 1.発表者名                                                                                                                |

| 塩見凖、石原亨、小野寺秀俊、新家昭彦、納富雅也                                                                                               |

|                                                                                                                       |

| 2.発表標題                                                                                                                |

| までは、                                                                                                                  |

|                                                                                                                       |

|                                                                                                                       |

| 3 . 学会等名                                                                                                              |

| DAシンポジウム2018                                                                                                          |

| 4.発表年                                                                                                                 |

| 2018年                                                                                                                 |

|                                                                                                                       |

|                                                                                                                       |

1.発表者名

松尾亮祐、塩見凖、石原亨、小野寺秀俊、新家昭彦、納富雅也

2 . 発表標題

波長多重を用いた二分決定グラフに基づく光論理回路の合成

3 . 学会等名

DAシンポジウム2018

4.発表年

2018年

〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6.研究組織

|  | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |  |

|--|---------------------------|-----------------------|----|--|