# 科学研究費補助金研究成果報告書

平成23年6月9日現在

研究種目:特定領域研究 研究期間:2006~2009 課題番号:18063006

研究課題名(和文) ナノMOSFETの揺らぎとデバイスインテグリティ

研究課題名(英文) Nano MOSFET Fluctuations and Device Integrity

研究代表者:

平本 俊郎 (Hiramoto Toshiro) 東京大学・生産技術研究所・教授

研究者番号: 20192718

研究成果の概要(和文): 実測と三次元シミュレーションにより微細トランジスタの特性ばらつきについて検討を行った. 特性ばらつきに強いデバイス構造として,極薄埋込酸化膜を有する SOI トランジスタを挙げ,従来のバルクトランジスタとは逆に,しきい値電圧を高くするほど ばらつきが抑制されることを示した.また,製造後に特性ばらつきを自己抑制する新しい手法を考案し,その効果をシミュレーションにより実証した.

研究成果の概要(英文): Random variability has been studied by measurements and simulation. It has been clarified that SOI MOSFETs with very thin buried oxide is less sensitive to random dopant fluctuations. A new method of self-suppression of variability after chip fabrication has been proposed and its validity has been demonstrated by simulation.

#### 交付決定額

(金額単位:円)

|         | 直接経費         | 間接経費 | 合 計          |

|---------|--------------|------|--------------|

| 2006 年度 | 11, 800, 000 | 0    | 11, 800, 000 |

| 2007 年度 | 11, 800, 000 | 0    | 11, 800, 000 |

| 2008 年度 | 13, 800, 000 | 0    | 13, 800, 000 |

| 2009 年度 | 13, 800, 000 | 0    | 13, 800, 000 |

|         |              |      |              |

| 総計      | 51, 200, 000 | 0    | 51, 200, 000 |

研究分野:集積デバイス工学

科研費の分科・細目:電気電子工学・電子デバイス・電子機器 キーワード:特性ばらつき,しきい値電圧,SOI,SRAM

#### 1. 研究開始当初の背景

大規模集積回路 (VLSI) を構成する MOS トランジスタは、性能向上のため年々微細化されている.トランジスタの寸法が小さくなると、さまざまなばらつき要因が顕在化し、トランジスタの特性がばらつき、集積回路が動作しない、あるいは歩留まりが著しく低下する等の問題が発生する.ゲート長寸法が50nm程度にまで微細化されていた当時でも、すでにばらつきの問題は深刻となっており、各半導体メーカーが対策に追われていた.将来、ゲート長がさらに微細化されることは明白であり、ナノスケールに微細化されたトラ

ンジスタのばらつき原因の究明と対策は急 務であった.

### 2. 研究の目的

本研究では、トランジスタ特性の実測とシミュレーションにより、トランジスタの特性 ばらつきを定量的に把握するとともに、特性 ばらつきの影響を受けにくい微細 MOS トランジスタ構造を提案することを目的とした.

### 3. 研究の方法

実際に膨大な数のトランジスタを測定す ることにより、微細トランジスタのしきい値 電圧ばらつきを把握した.一方,特性ばらつきに強いデバイス構造を研究するために,不純物ゆらぎを考慮した三次元デバイスシミュレーションを行った.さらに,特性ばらつきを製造後に抑制するという全く新しい方法を研究の過程で考案し,その効果をシミュレーションにより実証した.

#### 4. 研究成果

本報告では、SOI 基板を用いた特性ばらつきに強いデバイス構造の研究と、製造後に特性ばらつきを抑制する新手法について報告する.

### (1) SOI MOSFET の特性ばらつき解析

一般に、微細トランジスタのランダムな特性ばらつきは、チャネル中に存在する不純物の数と位置が揺らぐことによって引き起こされていることが知られている。この特性ばらつきの問題を抑制するために、SOI (Silicon-on-Insulator)基板上にトランジスタを形成し、トランジスタのチャネルには不純物をドープしない構造が提案されている。ところが、チャネル中に不純物をドープしないと、しきい値電圧の微調整を行うことが困難となる。

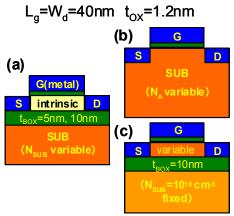

そこで本研究では、特性ばらつきを抑制しつしきい値電圧調整を可能とする構造として、薄い埋込酸化膜を有する SOI MOSFET の特性ばらつきを三次元シミュレーションにより検討した。このトランジスタでは、埋込酸化膜直下の基板に不純物をドープすることでしきい値電圧調整が可能である。図 1 にデバイス構造を示す。比較のため、従来のバルクトランジスタとチャネル不純物ドープした SOI MOSFET についてもシミュレーションを行った。

図 1. シミュレーションに用いた構造. (a) チャネルドープしない薄膜埋込酸化膜 SOI MOSFET. (b) バルク MOSFET. (c) チャネルドープ SOI MOSFET.

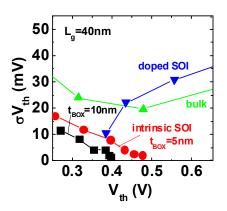

図 2. Vth ばらつきの Vth 依存性のシミュレーション結果.

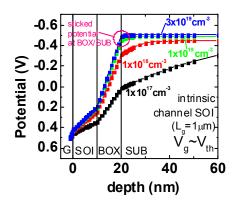

図 2 に、しきい値電圧ばらつき( $\sigma$ Vth)としきい値電圧(Vth)の関係である. バルクトランジスタとチャネルドープ SOI トランジスタでは、Vth が高くなるほどばらつきが増大しまう. これは Vth が高いトランジスタほど 不純物が多くチャネルに含まれるので、その揺らぎが大きくなることに起因する. ところが、チャネルドープしない薄膜埋込酸と比び SOI MOSFET では、逆に Vth が高くなるほど  $\sigma$ Vth が抑えられることが明らかとなった. これは、埋込酸化膜直下の不純物濃度を高いた、これは、埋込酸化膜/基板界面のポテンシャルのシミュレーション結果から見て取れる(図3).

以上のように、薄膜埋込酸化膜 SOI MOSFET では、特に Vth が高い超低消費電力向け用途のトランジスタで、高い Vth と特性ばらつき抑制を両立できることが明らかとなり、将来のデバイス構造として有望であることがわかった.一方、SOI MOSFET ではランダムテレグラムノイズが低減することも、実験により明らかにした.

図 3. シミュレーションにより得られたチャネルドープしない薄膜埋込酸化膜 SOI MOSFET におけるポテンシャルの深さ方向分布.

## (2) 製造後の特性ばらつき自己修復手法

特性ばらつきの問題に対処するには、トランジスタのばらつき自体を抑制することも重要だが、一方でトランジスタがばらついても回路を動作させる工夫も必要である.本研究では、スタティックメモリ(SRAM)において特性ばらつきを自動的に修復し、ばらつきの影響を抑制する新手法を提案した.

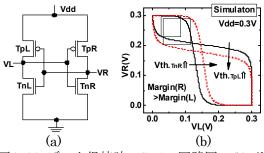

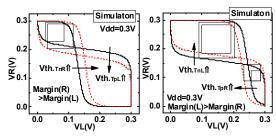

SRAMは通常6個のトランジスタで構成されるが、データは内部の4個のトランジスタで保持されている.図4(a)はデータ保持時におけるSRAMセルを示す.図4(b)がそのバラフライカーブである.リテンションノイズマージン(RetNM)はバタフライカーブ内部における左右の正方形のうち小さい正方形の一辺の長さと定義される.RetNMが0V以下の場合SRAMセルはデータを保持することができない.

図4. (a) データ保持時のSRAM回路図. (b) リテンションノイズマージン特性.

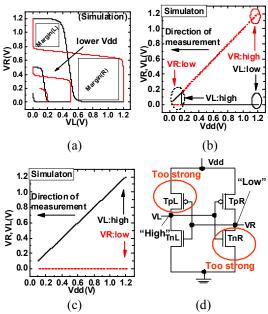

図5. (a) 電源電圧低下に伴う双安定崩壊. (b) 初期状態VR=high のときのVR, VL-Vdd特性. (c) 初期状態VR=low のときのVR, VL-Vdd特性. (d) 低Vdd時のバイアス条件.

図4(b)の例では左右のマージンのうち、左側のマージンが小さいことがわかるが、これは図4(a)においてTpLおよびTnRのしきい値電圧が低いことが原因となっている.そこで、本研究ではSRAM内部のしきい値電圧が低いトランジスタのしきい値電圧を選択的にシフトさせ、図4(b)のようにバタフライカーブを調整し、RetNMを向上させる手法を提案する.

SRAMにおける双安定状態崩壊を示したも のが、図5である. 図5(a)では、電源電圧が1.2V のとき左側のマージン (Margin(L)) が小さく, 電源電圧低下によってMargin(L)が0Vになっ ていく現象が確認できる. この現象をVL, VR ノード電圧からより詳細に示したものが図 5(b)(c)であり、電源電圧低下に伴いMargin(L) が0Vになったことによって低電源電圧時は このSRAMセルは必ずVR=low, VL=highが安 定状態となることがわかる. これはTpLおよ びTnRが相対的に強い(しきい値電圧が低い) からである. さらに、その時の回路図を示し たものが図3(d)であり、しきい値電圧が相対的 に低いトランジスタにのみゲート電圧が印加 されていることがわかる. すなわち, 電源電 圧を低下させることによってVL, VRノード 電圧はSRAMのアンバランス特性から一意に 決定し、さらにしきい値電圧が低いトランジ スタにのみ自動的にゲート電圧が印加されオ ン状態となっている.

図6. リテンションノイズマージンの向上.

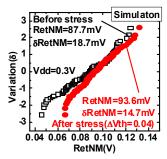

ここで、バイアス条件Vdd=3.5V、Vsub=-6Vを印加する. しきい値電圧が低いトランジスタのみがオン状態なので、そのしきい値電圧が基板ホットエレクトロンストレスにより上昇する. 一方、しきい値電圧が高いトランジスタのしきい値電圧はシフトを行うことができる. すなわち、ストレスによってしきい値電圧が低いトランジスタのしきい値電圧のみを選択的に高Vth側へシフトさせることができる. その過程をシミュレーションした結果が図6であり、本手法によってRetNMが向上したことを確認できる.

上記の過程をすべてのSRAMセルに同時に

一括適用すると、SRAMの不安定性を自己修復できる。図7にモンテカルロシミュレーションの結果を示す。本手法適用前後のSRAMセル100個におけるRetNMの分布である。この図から、RetNMの分布が本手法によって向上し、特にRetNMの最悪値付近のセルが大きく向上していることが確認できる。

以上より、全てのSRAMセルに一括に本手法を適用することにより、SRAM特有のアンバランス性を積極的に利用してRetNMを自己修復させることができることが明らかとなった

図 7. 本手法適用前後の RetNM の分布.

# 5. 主な発表論文等 (研究代表者、研究分担者及び連携研究者に は下線)

〔雑誌論文〕(計12件)

- [1] C. Lee, A. T. Putra, K. Shimizu and <u>T. Hiramoto</u>, "Threshold Voltage Dependence of Threshold Voltage Variability in Intrinsic Channel Silicon-on-Insulator No. 4, Issue 2, 04DC01, April, 2010 (查読有).

- [2] A. T. Putra, T. Tsunomura, A. Nishida, S. Kamohara, K. Takeuchi, and <u>T. Hiramoto</u>, "Impact of Oxide Thickness Fluctuation and Local Gate Depletion on Threshold Voltage Variation in Metal-Oxide-Semiconductor Field-Effect-Transistors", Japanese Journal of Applied Physics, Vol. 48, No. 6, 064504, 2009 (查読有).

- [3] <u>平本俊郎</u>, 竹内潔, 西田彰男,「MOSトランジスタのスケーリングに伴う特性ばらつき」, 電子情報通信学会会誌, Vol. 92, No. 6, pp. 416 426, 2009 年 (査読有).

- [4] A. T. Putra, A. Nishida, S. Kamohara, T. Tsunomura, and <u>T. Hiramoto</u>, "Consideration of Random Dopant Fluctuation Models for Accurate Prediction of Threshold Voltage Variation of Metal-Oxide-Semiconductor Field-Effect Transistors in 45nm Technology and Beyond", Japanese Journal of Applied Physics, Vol. 48, No. 4, 044502, 2009 (查読

有).

- [5] A. T. Putra, A. Nishida, S. Kamohara, and <u>T. Hiramoto</u>, "Random Threshold Voltage Variability Induced by Gate-Edge Fluctuations in Nanoscale Metal-Oxide-Semiconductor Field-Effect Transistors", Applied Physics Express, Vol. 2, No. 2, 024501, 2009 (査読有).

- [6] <u>平本俊郎</u>, 竹内潔, 西田彰男, 「増大する 微細 MOS トランジスタの特性ばらつき: 現状と対策」, 電気学会論文誌 C, Vol. 128, No. 6, pp. 820 824, 2008 年 6 月 (査読有).

- [7] T. Ohtou, <u>T. Saraya</u>, and <u>T. Hiramoto</u> (Invited), "Variable Body-Factor SOI MOSFET with Ultrathin Buried Oxide for Adaptive Threshold Voltage and Leakage Control", IEEE Transactions on Electron Devices, vol. 54, no. 1, pp. 40 46, January, 2008 (查読有).

- [8] T. Ohtou, N. Sugii, and <u>T. Hiramoto</u>, "Impact of Parameter Variations and Random Dopant Fluctuations on Short-Channel Fully Depleted SOI MOSFETs With Extremely Thin BOX", IEEE Electron Devices Letters, Vol. 28, No. 8, pp. 740 742, August, 2007 (查読有).

- [9] T. Hiramoto, T. Nagumo, T. Ohtou, and K. Yokoyama (Invited), "Device Design of Nanoscale MOSFETs Considering the Suppression of Short Channel Effects and Characteristics Variations", IEICE Transactions on Electronics, Vol. E90-C, No. 4, pp. 836 841, April, 2007 (査読有).

- [10] T. Ohtou, K. Yokoyama, K. Shimizu, T. Nagumo, and <u>T. Hiramoto</u>, "Threshold-Voltage Control of AC Performance Degradation-Free FD SOI MOSFET With Extremely Thin BOX Using Variable Body-Factor Scheme", IEEE Transactions on Electron Devices, Vol. 54, No. 2, pp. 301 307, February, 2007 (查読有).

- [11] T. Nagumo and <u>T. Hiramoto</u>, "Design Guideline of Multi-Gate MOSFETs With Substrate-Bias Control", IEEE Transactions on Electron Devices, Vol. 53, No. 12, pp. 3025 3031, December, 2006 (査読有).

- [12] A. T. Putra, M. Saitoh, G. Tsutsui, and <u>T. Hiramoto</u>, "Modeling of Body Factor and Subthreshold Swing in Bulk Metal Oxide Semiconductor Field Effect Transistors in Short-Channel Regime", Japanese Journal of Applied Physics, Vol. 45, No. 8A, pp. 6173 6176, August, 2006 (查読有).

- [1] J. Nishimura, <u>T. Saraya</u>, and <u>T. Hiramoto</u>, "Statistical Comparison of Random Telegraph Noise (RTN) in Bulk and Fully Depleted SOI MOSFETs", Ultimate Integration of Silicon (ULIS), Cork, Ireland, March 16, 2011.

- [2] T. Hiramoto (Invited), "Measurements and characterization of statistical variability", Workshop on Simulation and Characterization of Statistical CMOS Variability and Reliability, The International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Royal Hotel Carlton, Bologna, Italy, September 9, 2010.

- [3] T. Hiramoto, T. Saraya, and C. Lee, "Effect of Back Bias on Variability in Intrinsic Channel SOI MOSFETs", International Symposium on Technology Evolution for Silicon Nano-Electronics (ISTESNE), Tokyo Institute of Technology, June 3, 2010.

- [4] M. Suzuki, <u>T. Saraya</u>, K. Shimizu, T. Sakurai, and <u>T. Hiramoto</u>, "Simultaneously improvement of Write and Static Noise Margins in SRAM by Post-Fabrication Self-Convergence Technique", Workshop "The Fruits of Variability Research in Europe", Design, Automation & Test in Europe (DATE), International Congress Centre in Dresden, Dresden, Germany, March 12, 2010.

- [5] T. Hiramoto (Keynote), "Variability research: accomplishments and future directions a Japanese perspective", Workshop "The Fruits of Variability Research in Europe", Design, Automation & Test in Europe (DATE), International Congress Centre in Dresden, Dresden, Germany, March 12, 2010.

- [6] M. Suzuki, <u>T. Saraya</u>, K. Shimizu, T. Sakurai, and <u>T. Hiramoto</u>, "Improvement of Static Noise Margin in SRAM by Post-Fabrication Self-Convergence Technique", International Semiconductor Device Research Symposium (ISDRS), TP7-03, University of Maryland, MD, USA, December 10, 2009.

- [7] I. Yamato, T. Mama, T. Tsunomura, A. Nishida, and <u>T. Hiramoto</u>, "Anomalous Back-Bias Dependence of Threshold Voltage Variability in NMOSFETs Due to High Concentration Regions near Source and Drain", International Semiconductor Device Research Symposium (ISDRS), WP5-04, University of Maryland, MD, USA, December 9, 2009.

- [8] C. Lee, A. T. Putra, K. Shimizu, and <u>T. Hiramoto</u>, "Vth Dependence of Vth Variability in Intrinsic Channel SOI

- MOSFETs with Ultra-Thin BOX", International Conference on Solid State Devices and Materials (SSDM), Sendai, October 7, 2009.

- [9] M. Suzuki, <u>T. Saraya</u>, K. Shimizu, T. Sakurai, and <u>T. Hiramoto</u>, "Post-Fabrication Self-Convergence Scheme for Suppressing Variability in SRAM Cells and Logic Transistors", Symposium on VLSI Technology, Kyoto, pp. 148 – 149, June 16, 2009.

- [10] A. T. Putra, T. Tsunomura, A. Nishida, S. Kamohara, K. Takeuchi, S. Inaba, K. Terada, and <u>T. Hiramoto</u>, "A New Methodology for Evaluating VT Variability Considering Dopant Depth Profile", Symposium on VLSI Technology, Kyoto, pp. 116 117, June 16, 2009.

- [11] I. Yamato, A. T. Putra, and <u>T. Hiramoto</u>, "Impact of Lateral Dopant Profile on Threshold Voltage Variability in Scaled MOSFETs", Silicon Nanoelectronics Workshop, Kyoto, pp. 35 – 36, June 13, 2009.

- [12] T. Hiramoto (Invited), "Characterization of CMOS Variability Utilizing 1M-DMA and Takeuchi Plot", Workshop on Test Structure Design for Variability Characterization, DoulbleTree Hotel, San Jose, CA, USA, November 13, 2008.

- [13] T. Hiramoto (Plenary), "Measuring and Understanding Device Variability", ESSDER/ ESSIRC Variability Workshop, Edinburgh International Conference Centre, Edinburgh, UK, September 19, 2008.

- [14] A.T. Putra, T. Tsunomura, A. Nishida, S. Kamohara, K. Takeuchi, and <u>T. Hiramoto</u>, "Impact of Fixed Charge at MOSFETs' SiO2/Si Interface on Vth Variation", International Conference on Simulation of Semiconductor Devices and Processes (SISPAD), Hakone Prince Hotel, Kanagawa, Japan, September 9, 2008.

- [15] T. Hiramoto, M. Kobayashi, and J. Chen (Invited), "Mobility and Variability in Silicon Nanowire MOSFETs", 14th International Symposium on the Physics of Semiconductors and Applications (ISPSA-2008), Korea, Ramada Plaza Jeju Hotel, Jeju, p. 192, August 27, 2008.

- [16] A. T. Putra, T. Tsunomura, A. Nishida, S. Kamohara, K. Takeuchi, and <u>T. Hiramoto</u>, "Impact of Atomic Oxide Roughness and Local Gate Depletion on Vth Variation in MOSFETs", IEEE Silicon Nanoelectronics Workshop, S1205, Hilton Hawaiian Village, HI, USA, June 15, 2008.

- [17] K. Takahashi, A. T. Putra, and <u>T. Hiramoto</u>, "FinFETs with Both Large Body Factor and High Drive-Current", International

- Semiconductor Device Research Symposium (ISDRS), University of Maryland, MD, USA, WP9-01-11, December 12, 2007.

- [18] A. T. Putra, A. Nishida, S. Kamohara, T. Tsunomura, and <u>T. Hiramoto</u>, "Impact of Local Poly-Si Gate Depletion on Vth Variation in Nanoscale MOSFETs Investigated by 3D Device Simulation", International Semiconductor Device Research Symposium (ISDRS), University of Maryland, MD, USA, WP8-03, December 12, 2007.

- [19] T. Hiramoto (Invited), "Robust Design of Transistors: Present Status and Measures to Characteristic Variations", 2007 Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (AWAD 2007), Commodore Hotel Gyeongju Chosun, Korea, pp. 5 – 8, June 25, 2007.

- [20] K. Takahashi, T. Ohtou, A. T. Putra, K. Shimizu, and <u>T. Hiramoto</u>, "Body Factor and Leakage Current Reduction in Bulk FinFETs", Silicon Nanoelectronics Workshop, Rihga Royal Hotel Kyoto, pp. 95 97, June 10, 2007.

- [21] A. T. Putra, A. Nishida, S. Kamohara and <u>T. Hiramoto</u>, "Random Vth Variation Induced by Gate Edge Fluctuations in Nanoscale MOSFETs", Silicon Nanoelectronics Workshop, Rihga Royal Hotel Kyoto, pp. 73 –74, June 10, 2007.

- [22] <u>T. Hiramoto</u> and M. Kobayashi, "Characteristics Variation in Silicon Nanowire Transistors", 3rd International Nanotechnology Conference on Communication and Cooperation, Brussels, Bergium, April 17, 2007.

- [23] M. Kobayashi and <u>T. Hiramoto</u>, "Experimental Study on Quantum Structure of Silicon Nano Wire and Its Impact on Nano Wire MOSFET and Single-Electron Transistor", Technical Digests of IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, pp. 1007 – 1009, December 11, 2006.

- [24] T. Ohtou, T. Saraya, K. Shimokawa, Y. Doumae, Y. Nagatomo, J. Ida and T. Hiramoto, "Experimental Demonstrations of Superior Characteristics of Variable Body-Factor (γ) Fully-Depleted SOI MOSFETs with Extremely Thin BOX of 10nm", IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, pp. 877 880, December 13, 2006.

- [25] A. T. Putra, T. Ohtou, and T. Hiramoto, "Critical Substrate Bias in Variable-Threshold Voltage CMOS with Short Channel FD SOI MOSFETs," IEEE Silicon Nanoelectronics Workshop,

- Honolulu, HI, USA, pp. 159 160, June 12, 2006.

- [26] T. Ohtou, N. Sugii, and <u>T. Hiramoto</u>, "Impact of Parameter Variations and Random Dopant Fluctuations on Short-Channel Fully-Depleted SOI MOSFETs with Extremely Thin BOX"IEEE Silicon Nanoelectronics Workshop, Honolulu, HI, USA, pp. 15 16, June 11, 2006.

- [27] T. Hiramoto and T. Nagumo (Invited), "Multi-Gate MOSFETs with Back-Gate Control", 2006 International Conference on Integrated Circuit Design and Technology (ICICDT), Padova University, Padova, Italy, pp. 80 81, May 25, 2006.

〔図書〕(計1件)

<u>平本俊郎</u>, 内田建, 竹内潔, 杉井信之,「集積ナノデバイス」, 丸善, pp.199 – 221, 2009年11月.

#### [産業財産権]

○出願状況(計1件)

名称:ラッチ回路の電圧特性調整方法および

半導体装置の電圧特性調整方法

発明者:平本俊郎,鈴木誠,桜井貴康

権利者:東京大学

種類:特許

番号:特願 2009-141510 出願年月日:2009年6月12日

国内外の別:国内

- 6. 研究組織

- (1) 研究代表者

平本 俊郎 (Hiramoto Toshiro) 東京大学・生産技術研究所・教授 研究者番号: 20192718

(3) 連携研究者

更屋 拓哉 (Saraya Takuya) 東京大学・生産技術研究所・助手 研究者番号:90334367