# 科学研究費補助金研究成果報告書

平成21年4月1日現在

研究種目:基盤研究(B)研究期間:2006~2008

課題番号:18300014

研究課題名(和文) 実行パス情報に基づき自律的に最適化を行う高性能チップマルチプロセ

ッサの研究開発

研究課題名 (英文) High Performance Chip Multiprocessor with Self Optimization

Capability Based on Frequently Executed Paths

研究代表者

馬場 敬信(BABA TAKANOBU) 宇都宮大学・工学研究科・教授

研究者番号:70092616

#### 研究成果の概要:

本基盤研究では、プログラムの実行経路(これをパスと呼ぶ)情報を取得して、その情報を元に、より高性能な実行を行えるように自律的な最適化を行うチップマルチプロセッサの研究開発を行った。本研究の着想は、頻繁に実行されるループ(ホットループ)においては実行されるパスが極めて限定される場合が多いこと、またその限定されたパスには規則性があり高い確率で次のパスを予測可能であること、に基づいている。このため、限られたパスの中から次に実行するパスを予測し、予測したパスに対応したスレッドコードを投機的にマルチスレッド実行して、高性能化を達成する実行モデルを考案した。さらに、この実行モデルを詳細化し、実行モデルを実現するためのソフトウェアシステムを設計・開発し、同時にハードウェアアーキテクチャを設計して、シミュレータの開発を行った。また、提案システムにおける性能改善の見積り実験を行い、逐次コードを対象として非投機実行と比べて、 $1.5\sim3.0$  倍の高速化が達成できることを明らかにした。これらの成果は、添付した学協会誌論文、国際会議論文、口頭発表、著書により公表するとともに、特許として申請したものが、成立に至っている。この中で、国際会議発表において Best Paper Award を 1 件受賞し、国内学会の口頭発表により学生奨励賞を 4 件受賞している。

#### 交付額

(金額単位:円)

|        |              |             | (334)        |

|--------|--------------|-------------|--------------|

|        | 直接経費         | 間接経費        | 合 計          |

| 2006年度 | 6, 000, 000  | 1, 800, 000 | 7, 800, 000  |

| 2007年度 | 5, 700, 000  | 1, 710, 000 | 7, 410, 000  |

| 2008年度 | 2, 700, 000  | 810, 000    | 3, 510, 000  |

| 総計     | 14, 400, 000 | 4, 320, 000 | 18, 720, 000 |

研究分野:総合領域

科研費の分科・細目:情報学・計算機システム・ネットワーク

キーワード:高性能計算機システム、チップマルチプロセッサ、パスベース最適化

# 1. 研究開始当初の背景

半導体集積回路技術の発展とともに、チップ上のトランジスタ資源は増大の一途をたどり、本基盤研究に着手した時点において、一つのチップ上に複数のCPUコアを搭載した

チップマルチプロセッサがコンピュータシステムの重要な課題となることは明らかであった。さらに、このようなチップマルチプロセッサにおいて、集積回路技術の発展が、CPUコア数の増大を可能とすることも予想できたことであった。このことは現在の研究期

間終了時点における商用のチップマルチプロセッサの普及によっても裏付けられている。

このような状況下において、我々は、豊富なトランジスタ資源を活用して、チップマルチプロセッサの性能をいかに自動的に効効を重要な課題と考えた。即ち、既存の多くのプログラムは基本的に逐次存を前提に作成されているため、制御依存による制約からその並列化ッサッではない。このため、プロセッサがる場ではない。このため、プロセッサがある性能を自動的に引き出す技術が主要な意味をもつ。このような状況を踏まえて、我々は、チップ自身に自律的に最適化をある能力をもたせることが有効であるとの認識を深めた。

このような構想を具体化するに当って、 我々はベンチマークプログラムを用いた予 備実験を行い、プログラム中には繰り返し実 行されるコード領域(ホットスポット)が存 在し、かつこれらのコード領域には繰返し実 行されるループ(ホットループ)が存在する ことを明らかにした。さらに、ホットループ における実行経路(パス)の振舞に局所性が あり、上位2つまでのパスで全体の8割以上 を占める場合が多いことを明らかにした。

以上の背景、予備実験の結果を踏まえ、並列化が困難な逐次コードの高速化を大きな目標として、ホットループを対象に、そのループ内の頻出パスを検出し、その出現パターンを活用した最適化を自律的に行うチップマルチプロセッサを研究開発することを研究テーマとして定めた。

### 2. 研究の目的

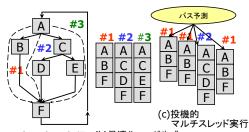

【全体構想】本研究は、ホットループ内の ホットパスに着目した最適化を行うが、具体 的には、上位2つのホットパスに限定したパ スベースの投機的マルチスレッド実行モデ ルを実現する。本実行モデルにおいては、図 1に示すように、実行開始後に、(a)ホットル ープを検出するとともに、パスプロファイリ ングによりホットループ内のホットパスを 特定し、(b)コードスケジューリングによりパ スごとに最適化した投機的なスレッドコー ドを生成し、(c)パス出現の規則性を活用した パス予測期の予測に応じて、スレッドコード を投機的に実行する、の手順で実行を進める。 また、これらをすべてチップマルチプロセッ サ自身が取得した実行パス情報に基づいて、 自律的に行う。

【具体的な研究目的】このような実行モデルの実現を目指して、本研究の具体的な研究目的は、以下の4点である。

(1) 低オーバヘッドで柔軟な実行プロファ

(a)実行パスの把握 (b)最適化コード生成

#### 図1 2パス限定投機実行方式

イリング機構の研究

- (2) 限定したパスに沿った動的かつ自律的 なマルチスレッドコード生成・最適化機 構の研究

- (3) パス情報取得とパス予測に基づく投機 実行を支援するチップマルチプロセッ サの研究

- (4) ベンチマークプログラムを用いた提案 モデルとその実現機構の有効性評価

#### 3. 研究の方法

2. に述べた研究目的を達成するために以下の手順に沿って具体的な研究を行なった。

### (1) ループ内のパスに限定したパスプロファ イラの研究開発

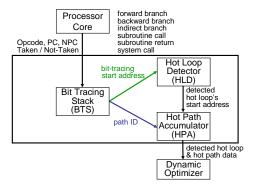

図2に設計したループパスプロファイラの構成を示す。ビットトレーシングスタック(BTS)がループ内限定のパス検出を行い、この結果をホットループ検出器(HLD)とホットパス累積器(HPA)に送る。HLD に蓄積した特定のアドレスから始まるループパスが一定の閾値を越えた時点でホットループと判定し、そのときHPA に累積されていた同じ先頭アドレスをもつパスをホットループパスとして出力する。本ループパスプロファイラに

**図2** ホットループおよびループパス検 出器の構成

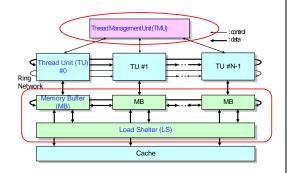

図3 2パス限定投機実行プロセッサ

ついては、ソフトウェアシミュレータを 試作してさまざまなベンチマークを用 いて実験を繰り返すとともに、設計パラ メータの調整を行った。

(2) 2 パス限定投機コードを実行するチップ マルチプロセッサアーキテクチャの設計 とシミュレータの試作

2 パス限定投機コードを実行するチップマルチプロセッサアーキテクチャを設計し、そのシミュレータを試作した。本プロセッサの構成を図3に示す。本プロセッサの特徴は、投機的なマルチスレッド実行を支援するための、プロセッサ間の支援するための、プロセット間のを支援するための、プロセット間のと、投機はに加えて、パスの予測機構と予測に基づく投機的な実行機構を備えている点にある。

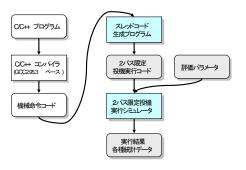

(3) ループパスに沿った投機コードのジェネ レータ

ループパスに沿った投機コードの生成アルゴリズムを明らかにし、このアルゴリズムに基づくコードジェネレータを研究開発した。本ジェネレータでは、特に投機的に実行するパスを2本までに限定することを踏まえて、スレッド間の依存関係を考慮したレジスタの転送機構などを工夫している。図4に、コード生成からシミュレーションまでの流れを示す。

## 4. 研究成果

本研究により得られた成果を以下に要約する。

- (1) 試作したホットループパスプロファイラ を用いた実験により、小規模のハードウェアによって、 $1 \sim 2$  位パスが高精度で 検出可能なことを明らかにした。

- (2) 研究開発したループパスプロファイラを 用いた実験により、SPEC CINT2000 の 8 つのベンチマークプログラムにおける 上位5位までの全40個のホットループ中、 実に39個のホットループにおいて上位2 本までのホットパスが80%以上を占めて

**図4** 2 パス投機コードの生成とシミュレーション

いることを明らかにした。

- (3) 試作したコードジェネレータによって、 逐次コード中のホットループから、ホットなループパスに沿った投機コードが生成されることを検証した。

- (4) 2 パス限定投機コードを実行するプロセッサのシミュレータにより、2 パス限定コードが実行できることを検証した。ただし、本シミュレータについては、メモリの動作に一部問題があり、継続的な検証が必要となっている。

- (5) 提案システムにおける性能改善の見積り 実験を行い、非投機実行と比べて、1.5~ 3.0 倍の高速化が達成できることを明ら かにした。

本研究に関しては、さらにプログラム実行時の制御フローやメモリアクセスの「偏り」に着目した基礎的な研究や、VLIWチップマルチプロセッサを対象とした自己最適化の研究などを行なっている。

# 5. 主な発表論文等

これらの成果は、添付した学協会誌論文、 国際会議論文、口頭発表、著書により公表するとともに、特許として申請したものが、成立に至っている。この中で、国際会議発表において Best Paper Award を1件受賞し、国内学会の口頭発表により学生奨励賞を4件受賞している。

(研究代表者、研究分担者及び連携研究者には下線)

[雑誌論文](計15件(期間中22件発表))

T. Baba, T. Yokota, K. Ootsu, J. Yoneda, K. Sato, H. Jutori, H. Yanome, Two-Path Limited Specul ative Multithreading Processor, Proc. 20th I ASTED International Conference on Parallel and Distributed Computing and Systems (PDCS2008),

- 查読有, 2008, pp. 348-355.

- 2) T. Baba, H. Yanome, K. Ootsu, T. Yokota, A Hardwa re Hot Loop Path Detector for Dynamic Paralleliz ation and Optimization, Proc. 4th IASTED International Conference on Advances in Computer Science and Technology (ACST 2008), 查読有, 2008, pp. 270-279.

- 3) <u>大津金光</u>, 横田隆史, <u>馬場が信</u>, プログラムループ の実行頻度分布に関する一考察, 電子情報通信学会 論文誌(A), 査読有, Vol. J91-A, No. 12, 2008, pp12 13-1218.

- 4) <u>T. Yokota</u>, <u>K. Ootsu</u>, <u>T. Baba</u>, Entropy Representa tion of Memory Access Characteristics and Cache Performance, Proc. 4th IASTED International Con ference on Advances in Computer Science and Tech nology (ACST 2008),查読有,2008,pp280-285.

- 5) <u>K. Ootsu</u>, <u>T. Yokota</u>, <u>T. Baba</u>, Run-time Binary Co de Patching and Its Application, Proc. 12th IAST ED International Conference on Software Enginee ring and Applications (SEA 2008), 查読有, 2008, pp106-111.

- 6) Y. Zhang, <u>K. Ootsu</u>, <u>T. Yokota</u>, <u>T. Baba</u>, Thread P ipelining with Clustered Data Communication on Commodity CMPs, Proc. 20th IASTED International Conference on Parallel and Distributed Computin g and Systems (PDCS2008), 查読有, 2008, pp342—347.

- 7) Y. Zhang, <u>K. Ootsu</u>, <u>T. Yokota</u>, <u>T. Baba</u>, Clustered Decoupled Software Pipelining on Commercial CM P, Proc. 14th IEEE International Conference on P arallel and Distributed Systems (ICPADS'08), 查読有, 2008, pp. 681-688.

- 8) <u>T. Yokota</u>, <u>K. Ootsu</u>, <u>T. Baba</u>, Potentials of Branch Predictors: from Entropy Viewpoints, Proc. I nternational Conference on Architecture of Computing Systems (ARCS 2008), 查読有, 2008, pp. 273—285.

- 9) <u>T. Yokota</u>, <u>K. Ootsu</u>, <u>T. Baba</u>, Adaptation Level a

- nd Injection Control in a Quasi-Globally Adapti ve Routing, Proc. 20th IASTED International Conf erence on Parallel and Distributed Computing an d Systems (PDCS2008), 查読有, 2008, pp. 112-117. Best Paper Award受賞

- 10) <u>T. Yokota</u>, <u>K. Ootsu</u>, <u>T. Baba</u>, Introducing Entro pies for Representing Program Behaviors and Bran ch Prediction Performances, Proc. Workshop on Ex perimental Computer Science (ExpCS 2007), 查読有, 2007, http://doi.acm.org/10.1145/1281700.12817 17.

- 11) <u>K. Ootsu</u>, T. Kobayashi, H. Ogawa, <u>T. Yokota</u>, <u>T. Baba</u>, A Hot Path Based Thread Partitioning Techn ique for Thread Pipelining Model, Proc. IASTED I nternational Conference on Advances in Computer Science and Technology (ACST 2007), 查読有, 200 7, pp. 293-298

- 12) <u>T. Baba</u>, T. Masuho, <u>T. Yokota</u>, <u>K. Ootsu</u>, Design of a Two-Level Hot Path Detector for Path-Based Loop Optimizations, Proc. IASTED International Conference on Advances in Computer Science and T echnology (ACST 2007), 查読有, 2007, pp. 23-28.

- 13) 横田隆史,大津金光,馬場敬信,プログラムの実行学動と分岐予測性能を表現するエントロピーの提案 情報処理学会論文誌コンピューティングシステム,査読有, Vol. 48, No. SIG 18 2007, pp. 12-31.

- 14) <u>T. Yokota</u>, <u>K. Ootsu</u>, <u>F. Furukawa</u>, <u>T. Baba</u>, Entro py Properties in Program Behaviors and Branch Pr edictors, Proc. 18th IASTED International Confe rence on Parallel and Distributed Computing and Systems (PDCS 2006), 查読有, 2006, pp. 448-453.

- 15) 岡大輔、<u>古川文人</u>、月川淳、<u>大津金光</u>、横田隆史、 <u>馬場教信</u>、VLIWシミュレーション環境HA-MENにお ける拡張性を重視した広域命令スケジューラの実装、 先伸/計算基盤システムシンポジウム SACSIS 2006 論文集、Vol. 2006, No. 5, 査読有, 2006, pp. 256-25 7.

[学会発表](計37件(期間中50件発表))

- 1) 矢野目秀人, <u>大津金光</u>, 横田隆史, <u>馬場敬信</u>, ループパスに基づいたプログラムの挙動解析, 電子情報通信学会コンピュータシステム研究会(CPSY), 2008.11.18, 北九州学術研究都市.

- 2) 小川大仁,大津金光,横田隆史,馬場敬信, ループ構造を考慮したパスベーススレッド分割手法の検討,電子情報通信学 会コンピュータシステム研究会(CPSY), 2008.11.18,北九州学術研究都市.

- 3) 五井孝典, 横田隆史, 大津金光, 馬場敬 信, PISA based VLIW Processor への割 込み/例外制御機能の実装, 情報処理学 会 第 71 回全国大会, 2009. 3. 10, .

- 4) 石井浩登,月川淳,<u>古川文人</u>,<u>横田隆</u>史,<u>大津金光</u>,馬場敬信,PISA based VLIW Processor 向けクロス環境の構築,情報処理学会 第 71 回全国大会,2009.3.10.

- 5) 安西由行、大津金光、横田隆史、馬場敬 信, CMP におけるキャッシュメモリ階層 構成の違いによる電力性能評価、情報 処理学会 第71回全国大会, 2009.3.10.

- 6) 佐藤裕輔, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場</u> <u>敬信</u>, 拡張容易な CMP シミュレータの電 力評価環境構築, 情報処理学会 第 71 回 全国大会, 2009. 3. 11.

- 7) 水沼光, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, ループ並列化における命令移動によるデータ依存同期待ち削減法の検討, 情報処理学会 第 71 回全国大会, 2009.3.11.

- 8) 阿部武志, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, グラフ理論に基づくスレッド分割手法におけるループ展開の適用検討, 情報処理学会 第 71 回全国大会, 2009.3.11.

- 9) 伊里拓也,小川大仁,大津金光,横田 <u>隆史</u>,馬場敬信,パスベーススレッド分 割手法に基づいた自動並列化システム の実装,情報処理学会第71回全国大会, 2009.3.11.

- 10) 津田翼, 矢野目秀人, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, ホットループパス検出機構における動的最適化に向けたパラメータの検討, 情報処理学会 第71回全国大会, 2009.3.11.

- 11) 中島伸吾,<u>横田隆史</u>,<u>大津金光</u>,<u>馬場</u> <u>敬信</u>,動的最適化のためのハードウェ アホットパス検出機構の実装,情報処 理学会 第71回全国大会,2009.3.12.

- 12) 米田淳一,福田明宏,十鳥弘泰,佐藤 和史,大津金光,横田隆史,馬場敬信, 2 パス限定投機システムの提案 - スレ ッド実行機構,情報処理学会 第71回全

- 国大会, 2009.3.12.

- 13) 佐藤和史,福田明宏,十鳥弘泰,米田淳一,大津金光,横田隆史,馬場敬信, 2 パス限定投機システムの提案 - マル チスレッド制御機構,情報処理学会第 71 回全国大会,2009.3.12.

- 14) 十鳥弘泰,福田明宏,佐藤和史,米田淳一,大津金光,横田隆史,馬場敬信, 2 パス限定投機システムの提案 - メモリアクセス機構,情報処理学会第71回 全国大会,2009.3.12.

- 15) 福田明宏,十鳥弘泰,佐藤和史,米田淳一,大津金光,横田隆史,馬場敬信,2パス限定投機システムの提案 スレッドコード生成処理系,情報処理学会第71回全国大会,2009.3.12.

- 16) 篠原啓志, 大津金光, 横田隆史, 馬場 敬信, 次世代マルチコアプロセッサの 試験評価を目的とした PS3 クラスタシス テムの構築, 情報処理学会 第71回全国 大会, 2009.3.12.

- 17) <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, 動的 バイナリ変換処理のためのユーザーレベルホットスポット検出システム, 情報 処理 学会 第 70 回全国大会, 2008.3.13.

- 18) 小川大仁, 伊里拓也, <u>大津金光</u>, <u>横田</u> <u>隆史</u>, <u>馬場敬信</u>, ループ細分を適用したパスベーススレッド分割手法の初期 評価, 情報処理学会 第 70 回全国大会, 2008. 3. 14.

- 19) 中島伸吾, 横田隆史, 大津金光, 馬場 敬信, ループに限定したハードウェア ホットパス検出機構, 情報処理学会 第 70 回全国大会, 2008. 3. 14.

- 20) 阿部武志, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場</u> <u>敬信</u>, グラフ理論に基づくスレッド分 割手法の適用検討, 情報処理学会 第 70 回全国大会, 2008. 3. 14.

- 21) 伊里拓也,小川大仁,大津金光,横田隆史,馬場敬信,ループ分割により関数境界を越えたパスベーススレッド分割手法の検討,情報処理学会第70回全国大会,2008.3.14.

- 22) 矢野目秀人,須貝佳彦,<u>大津金光</u>,<u>横</u> 田隆史,馬場敬信,パスに含まれる命 令数を考慮したハードウェアホットル ープパス検出機構,情報処理学会 第 70 回全国大会,2008.3.15.

- 23) 矢野目秀人,増保智久,大津金光,横田隆史,馬場敬信,ループに限定したハードウェアホットパス検出機構,電子情報通信学会コンピュータシステム研究会(CPSY),信学技報,2007.8.3,旭川市大雪クリスタルホール.

- 24) 芝崎諒, 大津金光, 横田隆史, 馬場敬信, 複雑なループ制御に対応したバイナ

リレベル自動並列化処理の実装,電子情報通信学会コンピュータシステム研究会(CPSY),信学技報,2007.8.3,旭川市大雪クリスタルホール.

- 25) <u>横田隆史</u>, <u>大津金光</u>, <u>馬場敬信</u>, エントロピーによるメモリアクセス特性の表現とキャッシュ性能, 情処研報, 計算機アーキテクチャ研究会, 2007. 8. 3, 旭川市大雪クリスタルホール.

- 26) 増澤英樹, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, バイナリレベルマルチスレッド 化におけるループアンローリングの効果, 電子情報通信学会コンピュータシステム研究会(CPSY), 信学技報, Vol. 106, No. 436, 2006, pp. 69-74.

- 27) 小林崇彦, 大津金光, 横田隆史, 馬場敬信, パスの実行頻度を考慮したマルチスレッドコード生成手法の検討, 電子情報通信学会コンピュータシステム研究会(CPSY), 信学技報, Vol. 106, No. 199, 2006, pp. 7-12.

- 28) 増保智久, 鈴木智, <u>大津金光</u>, <u>横田隆</u> <u>史</u>, <u>馬場敬信</u>, 動的最適化を支援する 2 レベルホットパス検出機構の設計, 電 子情報通信学会コンピュータシステム 研究会 (CPSY), 信学技報, Vol. 106, No. 199, 2006, pp. 13-18.

- 29) 芝崎諒, 大津金光, 横田隆史, 馬場敬信, 複雑な制御流を含むループに対応したバイナリレベル自動並列化処理系の実装, 情報処理学会 第 69 回全国大会, 2007. 3. 6, 早稲田大学.

- 30) 増澤英樹, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, マルチスレッドコードへのループアンローリング適用による高速化, 情報処理学会 第 69 回全国大会, 2007. 3. 6, 早稲田大学.

- 31) 豊田貴志,佐藤智一,大津金光,横田 隆史,馬場敬信,バイナリコードにお けるスレッド間メモリアクセス依存の 実行時チェック手法,情報処理学会 第 69 回全国大会,2007.3.6,早稲田大学.

- 32) 小川大仁, 小林崇彦, <u>大津金光</u>, <u>横田隆史</u>, <u>馬場敬信</u>, パスの実行頻度を考慮したスレッド分割手法の初期評価, 情報処理学会 第69回全国大会, 2007. 3.6, 早稲田大学.

- 33) 青木勲, 古川文人, 月川淳, <u>横田隆史</u>, <u>大津金光</u>, <u>馬場敬信</u>, VLIW 実験環境 CHA-MEN を開発基盤とした CMP シミュレ ータの一実装, 情報処理学会 第 69 回全 国大会, 2007. 3. 6, 早稲田大学.

- 34) 矢野目秀人,佐藤和史,高橋恭平,増 保智久,<u>大津金光</u>,横田隆史,馬場敬 信,MPEG2 エンコーダにおけるコード最 適化の適用とその効果,情報処理学会 第 69 回全国大会,2007.3.6,早稲田大

学.

- 35) 佐藤和史, 矢野目秀人, 高橋恭平, 増保智久, <u>大津金光</u>, 横田隆史, <u>馬場敬信</u>, MPEG2 デコーダにおけるコード最適化の適用とその効果, 情報処理学会 第69回全国大会, 2007. 3. 6, 早稲田大学.

- 36) 米田淳一,古川文人,月川淳,<u>大津金光</u>,横田隆史,馬場敬信,CHA-MEN 広域命令スケジューラ用プロファイラの実装,情報処理学会 第 69 回全国大会,2007.3.7,早稲田大学.

- 37) 三村貴志, 中島伸吾, <u>横田隆史</u>, <u>大津</u> <u>金光</u>, <u>馬場敬信</u>, PISA ベース VLIW プロセッサの FPGA による試作, 情報処理学会 第 69 回全国大会, 2007. 3. 7, 早稲田大学.

#### [産業財産権]

○取得状況(計1件)

名称:自己最適化演算装置

発明者:馬場敬信,横田隆史,大津金光

権利者:国立大学法人宇都宮大学

種類:特許

番号:第 3879002 号 取得年月日:2006.11.17

国内外の別:国内

〔その他〕 ホームページ

http://aquila.is.utsunomiya-u.ac.jp/

#### 6. 研究組織

(1)研究代表者

馬場 敬信(BABA TAKANOBU) 宇都宮大学大学院・工学研究科・教授 研究者番号:70092616

(2)研究分担者

横田 隆史(YOKOTA TAKASHI) 宇都宮大学大学院・工学研究科・准教授 研究者番号:90334078

大津 金光(00TSU KANEMITSU) 宇都宮大学大学院・工学研究科・助教 研究者番号:00292574

## (3)連携研究者

古川 文人(FURUKAWA FUMIHITO) 帝京大学ラーニングテクノロジー開発 室・助教

研究者番号:50407889