#### 研究成果報告書 科学研究費助成事業

今和 4 年 5 月 2 3 日現在

機関番号: 32407

研究種目: 基盤研究(C)(一般)

研究期間: 2018~2021

課題番号: 18K04288

研究課題名(和文)ソフトウェア無線に適した高感度で帯域可変な3相信号処理無線受信LSI設計技術

研究課題名(英文)LSI design techniques for a highly-sensitive variable-bandwidth three-phase software-defined wireless receiver

研究代表者

宇賀神 守(Ugajin, Mamoru)

日本工業大学・基幹工学部・教授

研究者番号:90506164

交付決定額(研究期間全体):(直接経費) 3.400.000円

研究成果の概要(和文):高感度の無線通信用LSIでは雑音の小さい信号源回路の実現が重要である。本研究では、トランジスタのもつ信号遅延により信号源雑音が増大するメカニズムを理論およびシミュレーションにより明確にした。さらに、直交信号などの多位相信号間のフィードバック信号処理により信号遅延による影響を除去できる信号源回路アーキテクチャを考案し、4相の信号源ICを試作・評価することで、その効果を実証した。

研究成果の学術的意義や社会的意義トランジスタのもつ信号遅延の縮小は、より微細な製造プロセスによって実現することもできる。しかしながら、製造プロセスの微細化は製造コストの大幅な増大を招く。本研究は、コスト上昇無しに高周波な無線通信用LSIを実現するための技術であり、産業的に有意義である。また多位相信号間の信号処理により信号遅延の影響を除去するという新しい考え方による回路アーキテクチャの研究であり、学術的意義も大きい。

研究成果の概要(英文): Realization of a low phase-noise voltage-controlled oscillator (VCO) is especially important for highly-sensitive wireless transceiver ICs. This study clarified the mechanism of a phase-noise degradation due to a transistor delay using theoretical analysis and simulations. Moreover, the study devised a phase-adjusting circuit architecture which could remove the transistor-delay effect. The circuit architecture used poly-phase VCO output signals. Quadrature VCOs with the phase-adjusting architectures were fabricated using 180-nm CMOS and showed a low-phase-noise performance than that of a conventional VCO.

研究分野:無線用のアナログ集積回路

キーワード: 電圧制御発振回路 位相雑音 トランジスタ遅延 位相調整回路 直交信号

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

#### 1.研究開始当初の背景

「インターネットオブシングス(IoT)」という言葉で表されるような、数多くのセンサーデータをまとめて、クラウドなどのデータサーバーに蓄積・利用する研究が盛んに行われている。IoT技術を実現するには、低コストで小型軽量な、しかも目的にかなった無線通信を行える無線センサー機器が求められる。これらの無線通信では、データの種類によって、広帯域な無線を使ってデータを短時間に送受信する場合や、非常に狭帯域な無線を使う場合など、多様な無線通信方式の利用が要望される。このため、センサーの種類によって、さらには同じセンサーでも通信目的によって無線帯域および変復調方式を柔軟に変更できることが望まれる。上記のような無線方式を柔軟に変更できる技術としてソフトウェア無線がある。

## 2.研究の目的

本研究は、ソフトウェア無線に最適な回路構成として、ダイレクトコンバージョン構成と中間周波数構成の両方の構成を外部制御信号により柔軟に選択でき、かつ低位相雑音の内部発振回路を併せ持つことで隣接チャネル耐性のよい無線受信回路の設計技術確立を目指す。このため具体的には以下の2つの回路技術の確立を目的とした。

## (1) 3位相の LC 電圧制御発振回路 (VCO)

3 相 VCO の発生する 3 相信号を用いた位相補正により LC 共振周波数と発振周波数を一致させ、VCO の位相雑音低減と高周波発振を同時に実現する。

## (2) IF 帯域・周波数を柔軟に可変制御できる複素フィルタ回路

IF 可変時の回路安定性が確保できるオペアンプを用いたスイッチキャパシタ型の3相アクティブRC 複素フィルタを実現する。

## 3.研究の方法

(1)まず理論および AC 解析を用いて、トランジスタのもつ信号遅延時間が VCO 位相雑音を増大させるメカニズムを明確にする。次にシミュレーションにより、その信号遅延の影響を最小化する VCO 回路構成の最適化を行う。最後に TSMC のチップ試作サービスを通して、プロトタイプ試作を行い実測により効果を検証する。

(2)スイッチトキャパシタの換算抵抗を可変にする手法として、スイッチング周波数を可変にする手法と、キャパシタアレイを作成して2進数的に容量値を可変にする手法を検討する。さらにこれら2手法の最適な組み合わせ構成を検討する。

### 4. 研究成果

#### (1)トランジスタ遅延と VCO 位相雑音の理論的検討

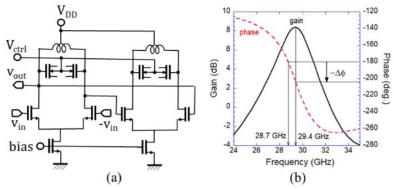

$30 \mathrm{GHz}$  帯 VCO 回路を低コストの  $180 \mathrm{nm}$  CMOS 技術で作成した場合の技術課題を検討した。 AC 解析により、図 1 に示すようにトランジスタの信号遅延により約 24 ° の位相遅れが生じる。 この位相遅れが VCO 位相雑音を悪化させるメカニズムには 3 種類あることを理論的に突き止めた。 下記の位相雑音に対する Leeson の解析式を用いて説明する。

$$L(\Delta f) = \frac{2kTF}{P_{osc}} \left\{ 1 + \left( \frac{1}{\phi'(f_{osc})\Delta f} \right)^2 \right\} \left( 1 + \frac{f_{1/f}}{\Delta f} \right) \quad ---- \text{(Leeson } \mathcal{O}\vec{z}\vec{b})$$

位相遅延により、発信周波数が LC 共振周波数よりも低くなることで、LC 共振回路のインピーダンスが低下し、ループゲインが減少する。これにより Leeson 式の出力信号振幅  $P_{osc}$  が小さくなることにより位相雑音が 1dB 程度大きくなる。

図 1 (b)に示すように、位相の周波数に対する変化率の絶対値  $|\phi'(f)|$  は LC 共振周波数で最大であり、発信周波数において減少している。これにより位相雑音が 2dB 程度大きくなる。電流源ノイズが VCO 位相雑音に与える感度は、=0°で最小になる。すなわち 24°の位相遅れにより電流源ノイズに対する感度が大きくなり、位相雑音悪化が起こる。このことにより、電流源ノイズの影響を最小にするには、3 位相出力の VCO は不適格であり、4 位相(直交)の VCO に検討対象を変更する必要があることを明らかにした。

図 1 . シミュレーションした差動 VCO の(a)ハーフオープンループ回路構成 (b) ゲインと位相

#### (2)位相調整型直交 VCO 回路の考案

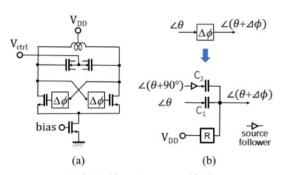

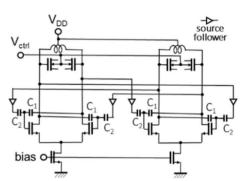

上記 の検討結果から 4 位相の直交 VCO にフォーカスして研究を進めた。上記 から の位相雑音悪化を除去する回路構成として図 2 の位相調整回路を考案した。 4 位相出力のうち通常の出力と 90°位相が進んでいる信号を電圧加重平均することで、位相遅れの無い信号を作成し、トランジスタのゲート端子に戻す回路構成である。図 3 に位相調整回路の付いた VCO 全体回路構成(直交 VCO)を示す。

図2.(a) 位相調整回路をもつ差動型 VCO 回路構成(b) 2個の容量とソースフォロワー回路による位相調整回路

図3. 位相調整回路の付いた直交 VCO 構成

# (3)試作結果による位相調整型 VCO 性能の実証

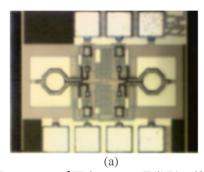

通常型の差動 VCO 2 個(図 4 (a) ) および 位相調整回路付き直交 VCO (図 4 (b) ) を TSMC 社の 180-nm CMOS 技術を用いて作成した。位相調整回路に用いた  $C_1$  と  $C_2$  の値は、それぞれ 600 fF および 60 fF である。図(a)と(b)の面積差は、 $C_1$  と  $C_2$  による面積の増加が原因である。

図4.チップ写真: (a) 通常型の差動 VCO 2 個 、(b) 位相調整回路付き直交 VCO

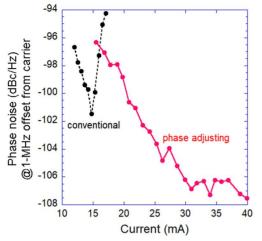

図 5 にオフセット周波数 1 MHz における位相雑音と消費電流の測定結果を示す。測定時の電圧条件は、 $V_{DD}=2.2V$ 、  $V_{ctrl}=0V$ である。差動型 VCO と直交 VCO をともに 1 個分の消費電流を表している。直交 VCO の消費電流は、 4 個のソースフォロワーの消費電流を含んでいる。位相調整型直交 VCO は動作可能な電流範囲が広く、位相雑音の最小値が約 6dB 小さくできることが判った。

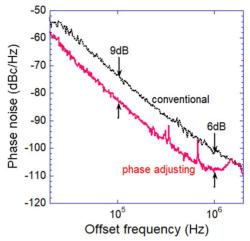

図 6 にオフセット周波数と位相雑音の関係 ( 測定結果 ) を示す。測定バイアスは図 5 の位相 雑音が最小になる条件にした。したがって、通常型 VCO と位相調整型直交 VCO の消費電流は、 それぞれ  $14.8\,\mathrm{mA}$  および  $39.9\,\mathrm{mA}$  である。図  $6\,\mathrm{mS}$  からオフセット周波数が  $100\,\mathrm{kHz}$  および  $1\,\mathrm{MHz}$  において、 位相調整構成により位相雑音がそれぞれ  $9\,\mathrm{dB}$  および  $6\,\mathrm{dB}$  縮小できていることがわかる。オフセット周波数  $1\,\mathrm{MHz}$  における  $3\,\mathrm{dB}$  の位相雑音劣化は、測定エラーによるものと考えている。

図5.オフセット周波数1MHzにおける位相雑音 と消費電流の関係(測定結果)

図 6 . オフセット周波数と位相雑音の関係 (測定結果)

## (4)スイッチトキャパシタによる可変抵抗の検討

スイッチトキャパシタの換算抵抗を可変にする手法として、スイッチング周波数を可変にする手法と、キャパシタアレイを作成して 2 進数的に容量値を可変にする手法の 2 手法の最適な組み合わせ構成を検討し、可変範囲や可変精度により最適な組み合わせ方法について知見を得た。

## < 引用文献 >

Mamoru Ugajin, Yuya Kakei, Nobuyuki Itoh, A quadrature voltage-controlled oscillator using phase-adjusting architecture for suppressing phase noise, IEICE Electronics Express, Vol.18 (No.10), 20210173, 2021 年 05 月

#### 5 . 主な発表論文等

「雑誌論文〕 計1件(うち査読付論文 1件/うち国際共著 0件/うちオープンアクセス 1件)

| 「推認論又」 計「什(つら直説的論文 「什)つら国際共者 「「什)つらオーノファクセス 「什)                                               |           |

|-----------------------------------------------------------------------------------------------|-----------|

| 1.著者名                                                                                         | 4 . 巻     |

| Ugajin Mamoru、Kakei Yuya、Itoh Nobuyuki                                                        | 18        |

|                                                                                               |           |

| 2.論文標題                                                                                        | 5 . 発行年   |

| A quadrature voltage-controlled oscillator using phase-adjusting architecture for suppressing | 2021年     |

| phase noise                                                                                   |           |

| 3.雑誌名                                                                                         | 6.最初と最後の頁 |

| IEICE Electronics Express                                                                     | 20210173  |

|                                                                                               |           |

|                                                                                               |           |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                                       | 査読の有無     |

| 10.1587/elex.18.20210173                                                                      | 有         |

|                                                                                               |           |

| オープンアクセス                                                                                      | 国際共著      |

| オープンアクセスとしている(また、その予定である)                                                                     | -         |

| 〔学会発表〕 | 計3件 | (うち招待講演 | 0件/うち国際学会 | 0件) |

|--------|-----|---------|-----------|-----|

|        |     |         |           |     |

1.発表者名

筧祐弥、宇賀神守、伊藤信之

2 . 発表標題

位相補正による直交LC電圧制御発振器の位相雑音低減

3.学会等名

電子情報通信学会 東京支部学生会 第26回研究発表会

4 . 発表年 2021年

1. 発表者名

筧祐弥、宇賀神守、伊藤信之

2 . 発表標題

位相補償構成による4相LC電圧制御発振器の位相雑音低減

3.学会等名

電気学会電子回路研究会

4.発表年

2020年

1.発表者名 宇賀神 守

2.発表標題 2段の多相周波数変換と多相アクティブ複素フィルタを用いた高イメージ抑圧無線受信回路構成

3.学会等名

平成30年 電気学会 電子・情報・システム部門大会

4 . 発表年

2018年

| ĺ | 図書〕 | 計0件 |

|---|-----|-----|

| ĺ | 図書〕 | 計0件 |

〔産業財産権〕

〔その他〕

-

6.研究組織

|       | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

|-------|---------------------------|-----------------------|----|

|       | 伊藤 信之                     | 岡山県立大学・情報工学部・教授       |    |

| 研究分担者 | (Itoh Nobuyuki)           |                       |    |

|       | (10598519)                | (25301)               |    |

## 7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|