# 科学研究費補助金研究成果報告書

平成21年6月22日現在

研究種目:若手研究(B) 研究期間:2007~2008

課題番号:19760244

研究課題名(和文) 窒化物系半導体トランジスタのノーマリーオフ・低オン抵抗化

研究課題名(英文) Normally-off and Low On-Resistance

Nitride-based Semiconductor Transistor

研究代表者 井手 利英 (TOSHIHIDE IDE)

独立行政法人産業技術総合研究所・エネルギー半導体エレクトロニクス研究ラボ・研究員

研究者番号:90397092

研究成果の概要: GaN トランジスタのノーマリーオフ化,低オン抵抗化を微細加工技術の導入により実現した.ノーマリーオフ化はゲートリセス構造を用いることでしきい値電圧+0.5V を実現した.低オン抵抗化についてはゲート長等の素子寸法を短縮することで 0.1mΩ·cm² を実現した.またこれらを両立するゲート構造を提案し電磁界解析,実験ともに実証した.

#### 交付額

(金額単位:円)

|         |           |         | ( ****    |

|---------|-----------|---------|-----------|

|         | 直接経費      | 間接経費    | 合 計       |

| 2007年度  | 2,700,000 | 0       | 2,700,000 |

| 2008 年度 | 700,000   | 210,000 | 910,000   |

| 年度      |           |         |           |

| 年度      |           |         |           |

| 年度      |           |         |           |

| 総計      | 3,400,000 | 210,000 | 3,610,000 |

研究分野:工学

科研費の分科・細目:電気電子工学,電子デバイス・機器

キーワード:GaN, AlGaN, トランジスタ, ノーマリーオフ, 短ゲート長化, オン抵抗

## 1.研究開始当初の背景

GaNに代表される窒化物系半導体は絶縁破壊電界,飽和ドリフト速度などの物性値に優れ,通信用高周波デバイスのみでなくパワースイッチングデバイス用材料として期待されている.しかし,窒化物系半導体パワーデバイスの実用化にはまだ遠い.その理由はネゲートバイアスをオフにしたときにチャフに変断(ノーマリーオフ化)が増大する,という問題があるからであるよって、GaN系トランジスタをパワーデバイス構造がよっして実用化するにはノーマリーオフ化,低オン抵抗化を両立可能なデバイス構造が

必要であった.

(1) ノーマリーオフ化:GaNトランジスタを代表するHEMTでは高いシートキャリア濃度のためにノーマリーオフ化が困難である.最近ではしきい値電圧が0 Vを超える素子も報告されているが,実用レベルの+2 Vまでは程遠い.これまでAIGaN障壁層の薄膜化,リセスゲート構造,フッ素系プラズマ表面処理,p型キャップ層,AIGaN/GaN/AIGaNダブルへテロ構造等の報告があるが,低オン抵抗化と両立したものはない.その原因は,ゲート・両立したものはない.その原因は,ゲート・関リのアクセス領域(ゲート・ソース間,ゲート・ドレイン間)のキャリアも枯渇させ,シート抵抗を大幅に増大させる構造やプロセスであったからである.

(2) 低オン抵抗化:これまでノーマリーオフ 化を試みた素子のオン抵抗はノーマリーオ ン素子と比べて一桁以上も高い.低オン抵抗 化にはソースとドレインのオーミックコン タクト抵抗の低減, ソース・ドレイン間のチ ャネル抵抗の低減が必要である.GaN系の主 なn型オーミックコンタクト構造はTi/Al系金 属をアニールして形成しているが,2次元電 子チャネルに直接コンタクトを形成する構 造,技術はまだ成熟していない.コンタクト 比抵抗は概ね10<sup>-6</sup> ~ 10<sup>-5</sup> Ω· cm<sup>2</sup>であり,デバイ スの利得,スイッチング速度などの各性能を 大幅に抑制している.実用化にはこの抵抗値 をさらに一桁下げる必要がある.チャネル抵 抗の低減については、最近では高AI組成 AlGaN, AlNをバリア層に用いてシートキャ リア濃度を増大する方法が主流であるが,し きい値電圧の低下を招くためノーマリーオ フ化の妨げになる.

本研究では,これらの問題に対して電子ビーム描画による微細加工技術を基盤とした新規のデバイス構造を開発することで解決を試みた.そしてノーマリーオフ化・低オン抵抗化の技術を導入した A(アンペア)級の GaN系トランジスタの実現を目指した.

### 2.研究の目的

(1) ノーマリーオフ化:下記の技術により,しきい値電圧を正バイアス化し,製作誤差0.1 V 以内の高い精度,再現性の実現を目指す

リセスゲート構造: リセス幅 0.1 μm 以下でエッチング深さ精度の高いドライエッチング技術を開発する.これにより空乏領域を必要最小限に抑え,素子を低オン抵抗化することができる.

フッ素系プラズマ表面処理:フッ素系プラズマ表面処理と前述のエッチング深さの両方を制御することで,しきい値電圧の正バイアス化とその制御を可能とする.従来はゲートプラズマ処理時にアクセス領域も処理され,チャネルが高抵抗化する問題があった.本研究ではリセスゲート構造形成中にゲート部のみプラズマ表面処理が可能なため,この問題を回避できる.

(2) 低オン抵抗化:下記の研究により,  $0.1 \text{ m}\Omega$ ·cm²よりも低い特性オン抵抗の実現を目指す.

低オーミックコンタクト抵抗化:本研究で新たに提案する多孔オーミックコンタクト構造を用いオーミックコンタクト比抵抗の  $5 \times 10^{-7} \, \Omega^{1} \, \mathrm{cm}^{2} \, \mathrm{以下までの低減を目指す.}$  従来構造でのコンタクト比抵抗は  $10^{-6} \, \sim 10^{-5} \, \Omega^{1} \, \mathrm{cm}^{2} \, \mathrm{であったが}$ ,本構造は緻密な設計に基づいてチャネルと直にオーミック接触を形成

できるため一桁の低下を見込める.また高濃度の不純物の注入による低抵抗化について も検討する.

低チャネル抵抗化:微細加工による短ゲート長化,短ゲート・ソース長化により低チャネル抵抗化を図る.ゲート長 0.1 μm 以下を高精度かつ再現性よく形成し,ゲート幅 5 mmを可能とするプロセスを開発する .また,ゲート・ソース長を 0.1 μm 以下に短縮する. 従来はアライメント精度,リフトオフプロセス,電極形状の問題により,ソース・ゲート長の短縮が困難であった.本研究では,ソース電極とゲート電極を高精度に分離する.とでソース・ゲート間の抵抗低減を図る.

#### (3) 最終目標

素子の最適化設計:ノーマリーオフ,低 オン抵抗の両立化と高耐圧化を考慮した最 適設計について調べる.最初は2次元電磁界 シミュレーションを中心に素子構造につい て調べた後に,素子製作と実証を行う.

上記の技術を集約してノーマリーオフかつ低オン抵抗の GaN-HEMT を製作し,耐圧 600 V,電流量 1 A 級の動作を目指す.

## 3.研究の方法

(1) ノーマリーオフ化:ゲートリセス構造とその作製プロセスについて研究し,ノーマリーオフ化としきい値電圧の制御技術の確立を目指す.手法としては電子ビーム描画,ドライエッチング,プラズマ表面処理を用いる.具体的には,

電子ビーム描画によりリセスエッチング用のマスクを形成する、マスクのエッチング耐性について調べ、不足する場合には従来の電子ビーム描画用レジストのマスクよりもエッチング耐性が大幅に向上する SiN, SiO2 等の無機材料も検討する.

リセスエッチングに必要な面内均一性よく,数 nm のエッチング量を制御可能な高精度エッチング条件を調べる.要求されるエッチング精度が前述の微細孔よりも高いため,新たなエッチング用ガスの選択も視野に入れ,リセス深さの再現性,均一性を高めるプロセスを開発する.

リセスエッチングした開口の表面にフッ素系プラズマで表面処理し、リセス深さとプラズマ表面処理の条件でGaN-HEMTのしきい値電圧制御を可能とする、プラズマ表面処理でのマスクの損傷についても調べて処理条件を検討する。

- p 型不純物の表面注入構造について新たに検討し pn 接合を用いた新規ノーマリーオフ構造の実現を目指す.

- (2) 低オン抵抗化: GaN-HEMT の低オン抵

抗化へ向けたオーミックコンタクト抵抗,チャネル抵抗の低減について研究する.オーミックについては微細孔構造を用いる.チャネルについては短ゲート長化,短ゲートソース長化を実施する.具体的には,

微細加工を取り入れた多孔オーミックコ ンタクト構造による低抵抗オーミックコン タクトを実現する. AlGaN 層に GaN チャ ネルまで到達するサブum サイズの微細な孔 を多数開け,電極用金属を蒸着する.これに より2次元電子ガスをのキャリア濃度,移動 度を高く保った状態で ,GaN チャネルへ直接 にオーミック接触を実現する .  $5 \times 10^7 \Omega$ ・ cm<sup>2</sup> 以下のコンタクト比抵抗を目指す.オー ミックコンタクトへのイオン注入による高 不純物濃度化について検討する. 具体的には 最近成果の多い Si 系不純物の注入を目指す. オーミック電極材料について検討をする. 具 体的には Si を含んだ金属材料を用いてオー ミック電極を形成することで低抵抗化を目 指す.

電子ビーム描画とリセスエッチングによる微細加工で低チャネル抵抗化,相互コンダクタンスの向上,高周波化のためにゲート長を0.1 μm 以下に短縮する.しかし,ゲート長 LG と AlGaN バリア層厚 dAlGaN のアステートにが5以下では短チャネル効果にしているので、AlGaN バリア層厚も薄くすることが判明しているので、AlGaN バリア層厚も薄くすることが当明しているので、AlGaN バリア層厚も薄くすることが必要な場合には SiO2 等を用いた無機レジストではいる電子ビーム描画プロセスの導入も対する.これらの技術を開発し,高精度かつス長の素子構造を実現する.

電流コラプスの影響を取り除くために AlGaN 上部に SiN 膜を形成する. そのため の SiN 成膜プロセスを開発する.

## (3) 素子の最適化設計と大面積化

リセスエッチングについて, ノーマリーオフ化に加えて高い耐圧を維持できるプロセス条件について検討する.電磁界シミュレーションにより素子構造の最適化により高耐圧化へとつなげる.それにより, ゲート・ドレイン間隔をさらに短縮して低オン抵抗化の実現を目指す.耐圧とゲート長の関係を調べ短ゲート長化, 短ゲート・ソース長化の限界を示し, 素子製作を行うことで実証する.

大面積化のプロセス開発を行い, TEG サイズからゲート幅数 mm オーダまで素子の大型化を図る.そして600V/1A級の大型素子の作製・評価を実施する.

#### 4. 研究成果

## (1) ノーマリーオフ化

リセスエッチング用マスク,表面パッシ ベーション,層間絶縁膜等の数々の用途で必 要となる SiN 膜の形成方法について確立し た. 蒸着, プラズマ CVD, 熱 CVD 法につい て検討を行い,低温堆積,カバレッジ,高絶 縁耐圧を満たす成膜方法としてプラズマ CVD 法を選定し、その形成条件を確立した. 電子ビーム描画とドライエッチングにより, SiN 膜へリセスエッチング用マスクの形成し、 ゲート長 0.2μm に相当するマスク形成を可 能とするプロセスを確立した. また,プラ ズマCVDのN2プラズマ発生条件を制御する ことでAlGaN/GaNウェハのシート抵抗が高 抵抗化することがわかった.その要因として は表面のチャージアップが考えられ,新たな ノーマリーオフ化のプロセスへ発展させる 可能性を見出した.このプロセスによる 2DEG チャネルの空乏化による新たなノー マリーオフ構造を試みたが ,N₂ プラズマ表面 処理ではチャネル電流を阻止するのみでゲ ート制御を実現することはできなかった。

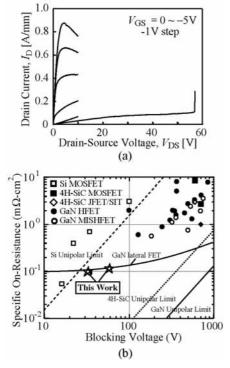

電子ビーム描画と塩素ドライエッチングによりリセスゲート構造を形成し、ゲート電極下部の AlGaN 厚を 5nm 以下とすることでノーマリーオフ化を実現した。図 1 にノーマリーオフ化した素子の直流特性を示す。ゲートしきい値電圧は  $0.0 \sim +0.5 \rm V$  が得られた。ゲート金属と AlGaN 層の間に 10nm 以下の薄い  $SiO_2$  膜を用いることで  $+7 \rm V$  までゲート電圧が印加できた。

図 1 ノーマリーオフ HEMT の特性.

CF4 プラズマ表面処理ではエッチング作用によりしきい値が若干増加する効果は得られたがプラスのしきい値電圧には至らなかった.またしきい値制御が可能な安定した変化も得られなかった.

Li 系化合物の素子表面への堆積&加熱による pn 接合形成およびノーマリーオフ化を試みたがゲートリーク電流が増加するのみで pn 接合を形成できなかった.

## (2) 低オン抵抗化

多孔構造によるオーミックコンタクト低減を目指し、電子ビーム描画とドライエッチングにより半径  $r=0.2\sim0.5\mu m$  程度の微小孔を充填率  $10\sim90\%$  で形成したオーミックコンタクト構造を形成し、評価した.しかし、孔を形成する前と比べてコンタクト抵抗は若干上昇し、 $10^{-5}$   $\Omega\cdot cm^2$  前半程度となった.原因としてエッチングガスと表面の反応による電極領域の低キャリア濃度化やエッチングから電極形成に至るまでの間での表面処理に問題があると考えられる.またシリサイド系材料をオーミックに用いて低抵抗化を図ったが目立った改善は得られなかった.

電子ビーム描画による短ゲート長化,短ゲート・ソース長化について実施し,ゲート 長  $0.1\mu m$ ,ゲートソース長  $0.5\mu m$  の HEMT で  $0.1m\Omega cm^2$ を実現した.図 2に低オン抵抗素子の特性を示す、特性オン抵抗 $0.12m\Omega cm^2$ の素子では耐圧 56Vとなり、GaN-HEMT の理論限界を超える性能が得られた.

図2 低オン抵抗 HEMT の直流特性と理論 曲線に対する得られた素子の性能.

上述した SiN 形成条件を用い,電流コラプスの影響を防ぐための SiN 保護膜の効果について検討した. SiN 膜の形成することでドレイン電流の減少を 10%以下に押さえることができた.

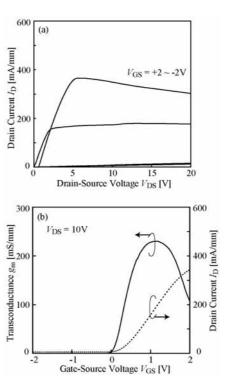

#### (3) リセスゲート構造での高耐圧設計

リセスゲートによるノーマリーオフ化と低オン抵抗化を両立させるために短リセス長化を試み,最短 0.2 µ m のリセス長でのノーマリーオフ動作を実現した.相互コンダクタンスが大幅に改善され,最大相互コンダクタンス 220mS/mm が得られた.DC 特性を図3に示す.

図 3 低オン抵抗・ノーマリーオフを実現した HEMT の DC 特性 .

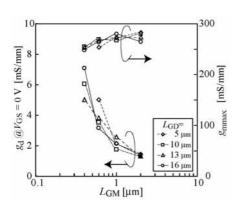

リセス長に比べて大幅に長いゲート電極 長をもつ構造を採用することで(例:リセス 長 0.2 µm に対してゲート金属長 1.0 µm 以 上)ゲートのドレイン端に発生する高電界を 分散し、ノーマリーオフ・低オン抵抗・高耐 圧を全て満たす構造をシミュレーションに て確認することができた.そして実際の素子 を作製・評価することで,ゲートのドレイン 端の高電界を分散できた指標となるドレイ ンコンダクタンスの減少が見られた.加えて, オン抵抗,相互コンダクタンスがリセス長に 依存し,短リセス長にすればゲート長を長く してもこれらの性能が維持されることを実 験的に示した.ドレインコンダクタンスと最 大相互コンダクタンスのゲート電極長依存 性を図4に示す.

図4 ドレインコンダクタンスと最大相互コンダクタンスのゲート電極長依存性.

大型素子の作製についてはゲート長 1.5mm の素子において電流 0.5A, オン抵抗 20 の素子が得られたが,ピンチオフ特性に ついて改善の余地が残った.これはゲート形 成プロセスで改善可能と思われる.

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文](計 1 件)

T. Ide, M. Shimizu, S. Yagi, M. Inada, G. Piao, Y. Yano, N. Akutsu, H. Okumura, and K. Arai, Low on-resistance AlGaN/GaN HEMTs by reducing gate length and source-gate length, phys. stat. sol. (c) 5, No. 6, pp. 1998–2000 (2008), 查読有

#### [学会発表](計 2 件)

井手 利英 , 濵名 通徳 , 朴 冠錫 , 八木 修一 , 矢野 良樹 , 清水 三聡 , AlGaN/GaN MOS-HFET への CF4 プラズマ表面処理の効果 ,第 56 回応用物理学関係連合講演会 , 2009/03/31 , 筑波大学

<u>井手 利英</u>,清水 三聡,八木 修一,朴 冠錫,生方 映徳,矢野 良樹,奥村 元,荒井 和雄,AIGaN/GaN HEMT へのプラズマ CVD による SiN 表面保護膜形成,第55 回応用物理学関係連合講演会,2008/03/29,埼玉大学

## 6.研究組織

#### (1)研究代表者

井手 利英(IDE TOSHIHIDE)

産業技術総合研究所・エネルギー半導体エレ

クトロニクス研究ラボ・研究員

研究者番号:90397092

(2)研究分担者

#### (3)連携研究者