#### 研究成果報告書 科学研究費助成事業

今和 5 年 6 月 2 8 日現在

機関番号: 35302 研究種目: 若手研究 研究期間: 2019~2022

課題番号: 19K20238

研究課題名(和文)非同期回路に基づく高信頼・低消費電力な次世代型身体ネットワーク用ICチップの開発

研究課題名(英文) Development of highly reliable and low power IC chip for the body area network based on asynchronous circuit

#### 研究代表者

近藤 真史 (Kondo, Masafumi)

岡山理科大学・工学部・准教授

研究者番号:90590133

交付決定額(研究期間全体):(直接経費) 3.200,000円

研究成果の概要(和文):本研究は,デジタル補聴器等に代表される生体信号処理プロセッサ(DSP)の低消費電力化および小面積化を目的として,これに内蔵される演算器の新たな構成法を提案している.まず,単一の全加算器を用いて逐次的に演算を行う直列乗算器を対象に,クロックパルスを用いない非同期式回路に基づく制御手法を導入することにより,消費電力を約32%,回路面積を約90%削減することに成功している.次に,生体信号処理において下位ビットの演算結果が冗長な点に着目し,特に最大積から乗数を逐次減算することによりよれてアメルビットから演算結果を確定可能な手法を提案・設計した結果,十分な精度を維持しつつも,消費電 力を約75%削減している.

研究成果の学術的意義や社会的意義 提案の乗算器では、単に非同期的な制御手法を導入するだけでなく、更に一対の加算器を相補的に制御すること で従来の非同期回路では不可避であった休止相を隠蔽する手法を提案しており、これは非同期回路の新たな設計 手法を切り開くものである.これに続くトランケート乗算器の直列化については、これまでに類似の報告はなされておらず、さらにこれを減算で効率的に実現する手法は極めて高い独創性を備えている. これらの直列乗算器については種々の性能で通じてその有効性が確認されており、この種の生体用信号処理 プロセッサを内蔵する医療機器への応用,さらにはそれらの機器を必要とする患者の"生活の質"の改善効果を期

研究成果の概要(英文): In this study, I proposed a new architecture for low-power and small-area Multiply and Accumulation (MAC) for a biological signal processor implemented in digital hearing aids.

The proposed MAC is based on a serial multiplier that performs operations sequentially using a full adder. By applying a control method based on an asynchronous circuit without clock pulses, I

succeeded in reducing power consumption by about 32% and circuit area by about 90%.

In addition, I proposed a multiplication method that confirms the product from the upper bits by sequentially subtracting the partial product from the maximum product that is statically determined by the number of operation bits. I designed the serial multiplier based on the proposed calculation method, confirmed its operation by simulation, and showed its effectiveness of it through the error evaluation with the truncation of lower bits.

研究分野: 計算機工学

キーワード: 直列演算器 非同期式回路 乗算器 メタステーブル

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

### 1.研究開始当初の背景

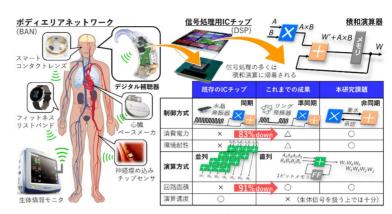

図 1 研究概要

現在,これら生体内外に配置された無線機器から様々な生体信号を取得し,それらを統合的に管理するボディエリアネットワーク(BAN)が注目されている(図 1 左). BAN によれば生体内外の信号を簡便かつリアルタイムに計測できるため,患者は体調管理が容易となり,医療従事者はより適切・迅速な治療が可能となる.そして将来的には,体内のインプランタブル機器と連動して直接的に治療や投薬を行う手法が検討されるなど,次世代の医療技術基盤として期待されている③.こうしたBANの概念は2012年にIEEE 802.15.6として規格・標準化され,特にこれを構成するICチップ(以下,BAN-IC)には,生体内外で長時間動作する低消費電力性と,生体情報が漏洩しない高信頼性が強く求められている.

## 2. 研究の目的

上述の背景のもと本研究では,クロックを用いない非同期回路の制御手法を最大限活かすことにより,低消費電力性と高信頼性を兼ね備えた BAN-IC の開発・実装を目的とする(図 1 右).本研究ではこれを確実に達成するため,以下の段階目標(1)~(5)を設定する.まず,(1)準同期直列演算器のリング発振器を要求-承認信号からなる非同期回路に置換してクロックを取り除き,更なる低消費電力性とインプランタブル機器にも適用し得る環境耐性を与える.また,(2)非同期回路と積和演算における冗長な演算を削減し,演算時間の短縮とこれに係る消費電力の削減を図る.次に,(3)BAN-IC に対する信号の入出力形態,すなわち直列の入出力に適した AD コンバータと無線暗号化回路を設計し,これらもまた非同期回路として制御することで高信頼かつ無駄のないデータの授受を実現する.そして,(4)再構成型 IC チップ(FPGA)に対する実装実験を通じてその動作を十分に確認した上で,(5)BAN-IC の実装を行い,種々の特性解析を以ってその有効性を確認する.

#### 3.研究の方法

本研究では,上述の目的(1)~(5)を段階的に実施する計画であったが,(2)についてより効率的・発展的な冗長演算の削減手法を検討可能となった点,(3)の暗号化に係る内容の一部に類似した先行研究が発表された点を踏まえて,以下は主に(1)~(3)で採った手法について述べる.

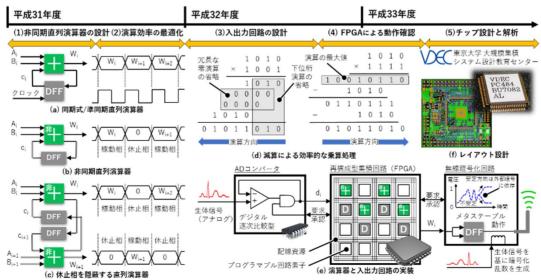

図 2 研究方法

(1) 非同期直列演算器の設計: 非同期回路では演算完了のタイミングに対応するクロックが存在しないため,クロックに代わる制御手法として二線化を施す必要がある. 二線化では 1 桁のデータを 01 または 10 の 2 桁で表し,00 を無効なデータとして扱う. そして,回路上に有効なデータが存在する状態を稼動相,存在しない状態を休止相といい,8 相を交互に繰り返すことで演算完了のタイミングを検知する. 本研究では,直列演算器における演算が加算器のそれに限定される点に着目し,加算器のみに二線化を施して非同期直列演算器を実現する(図 2(b)). ここで,休止相の挿入に伴って通常の 2 倍の演算時間を要するとともにそれに起因して消費電力が増大する可能性がある.そこで本研究では更に一対の加算器を配置し,二対の加算器で稼動相と休止相をそれぞれ相補的かつ交互に処理することにより,非同期回路特有の休止相に係る無効な演算を隠蔽する方針を採っている(図 2(c)).

(2)<u>演算効率の最適化</u>:積和演算器の演算時間や消費電力の大部分を乗算が占めるため,本研究では以下の観点から冗長な演算を削減し,演算器の更なる高性能化を図る(図 2(d)).

- 零乗算に係る部分積の省略:乗算において,乗数が0である桁に対応する部分積の演算結果は全て0となる.したがって乗数が0である場合,その部分積の算出に係る処理を省略するよう制御を加えることにより,期待値的に乗算における加算回数を約半分に削減できる.

- トランケート乗算の導入:乗算結果における下位桁は微小な信号変化を表し,デジタル信号処理の過程で生じる丸め誤差を考慮するとその重要度は特に低いものとなる.そこで本研究では,下位桁を予め省略・補間するトランケート乗算を(1)の直列演算器に応用し,演算回数とそれに起因する消費電力の更なる半減化を図る.ただし,一般的な乗算手法では桁上げを考慮して下位桁から順に演算必要がある.これに対して本研究では,乗算結果の取り得る最大値から順に減算を行うことで桁上げに係る演算を排除し,上位桁のみを対象とした乗算を実現する.

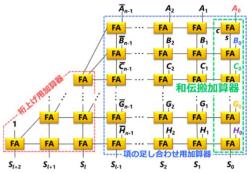

(3)入出力回路の設計:直列演算器は1桁ずつ演算を行うため,入力となるADコンバータもこれに対応した逐次比較型を採用し,入力から演算まで無駄のないデータの授受を実現する(図2(e)左).特に,(1)~(2)を経て設計された直列演算器の演算性能を担保するためには,複数の演算器を用いた並列処理が必須であり,さらにそれらの演算結果を足し合わせる桁上げ保存加算器(CSA)が必要となる.そこで本研究では,CSAには各演算器の下位ビットから順に結果が確定する点に着目し,和を逐次的に加算する和伝搬加算器を定義した上で(図3),これをさらに直列演算器として再構成する方針を採る.

図 3 A~H項の和Sを求めるCSA

# 4. 研究成果

上述の(1) ~ (3)の各演算器を論理ゲートレベルで設計し,シミュレーションを通じて所望の動作を確認するとともに,(4)の FPGA 実装時における消費電力と所要面積の解析を行った(図 4).

図中の AR-MUL はアレイ型並列乗算器, RO-MUL はリングオシレータを用いた直列乗算器, DA-MUL は(1)の相補制御型直列乗算器, TR-MUL は(2)のトランケート型直列乗算器を表しており, いずれも 16 ビット演算時の解析結果である. 図 4 より, 提案の直列乗算器 DA-MUL および TR-MUL は, 既存のそれに比して優れた低消費電力性と小面積性を実現している

続いて、(3)の桁上げ保存加算器の解析結果を図5に示す、図中のP-CSAは既存の並列CSA、S-CSAは提案の直列CSAであり、DFFが追加で必要となるものの、LUT数では大幅な小面積性を達成できている.特に、提案のS-CSAは単にDFFを増やすのみを以って多ビット化に対応できるため、LUT数は項数に依存することなく、一定の面積で演算可能な結果が示されている.

| 乗算器    | 消費電力<br>[nJ] | 回路面積<br>(LUT・DFF) |

|--------|--------------|-------------------|

| AR-MUL | 4.25         | 64 · 960          |

| RO-MUL | 3.38         | 83 · 54           |

| DA-MUL | 2.89         | 85 · 92           |

| TR-MUL | 2.15         | 67 · 49           |

# 図 4 各演算器の解析結果

| 桁上げ保存<br>加算器 | 項数 | 回路面積<br>(LUT・DFF) |

|--------------|----|-------------------|

|              | 4  | 367 · -           |

| P-CSA        | 8  | 667 · -           |

|              | 16 | 1267 • -          |

|              | 4  | 133 · 53          |

| S-CSA        | 8  | 133 • 41          |

|              | 16 | 133 • 65          |

図 5 CSA の回路面積の比較

# <参考文献>

- [1]Mordor Intelligence LLP, "Global Wearable Medical Devices Market," Healthcare(Aug.2017)

- [2]D.Fitzpatrick, "Implantable Electronic Medical Devices," Elsevier (Oct. 2014)

- [3]杉本千佳,河野隆二,"最先端医療を実現する生体内外センサネットワーク技術 -生体に低 侵襲で高信頼な医療のために-,"情報処理学会誌, Vol.54, No.6, pp.606-611 (June 2013)

#### 5 . 主な発表論文等

「雑誌論文〕 計1件(うち査読付論文 1件/うち国際共著 0件/うちオープンアクセス 0件)

| 「維誌論又」 計1件(つら直読的論文 1件/つら国際共者 0件/つらオーノファクセス 0件) |             |

|------------------------------------------------|-------------|

| 1.著者名                                          | 4. 巻        |

| 永田将大,近藤真史, 茅野功,横川智教, 佐藤洋一郎                     | 104         |

| 2.論文標題                                         | 5.発行年       |

| 相補制御に基づく休止相を隠蔽可能な非同期式直列乗算器の一構成法                | 2021年       |

| 3.雑誌名<br>電子情報通信学会和文論文誌A                        | 6.最初と最後の頁 - |

| 掲載論文のDOI (デジタルオブジェクト識別子)                       | 査読の有無       |

| なし                                             | 有           |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難         | 国際共著        |

# ------〔学会発表〕 計9件(うち招待講演 0件/うち国際学会 0件) 1.発表者名 〔学会発表〕

千田奈侑,近藤真史,浜田篤,横川智教,佐藤洋一郎

2 . 発表標題

ビットシリアル積和演算器に対する直列桁上げ保存加算器の一構成法

3.学会等名

第72回電気・情報関連学会中国支部連合大会

4.発表年 2021年

1.発表者名

永田将大, 近藤真史, 茅野功, 横川智教, 佐藤洋一郎

2 . 発表標題

動的なパルス生成機構に基づいたトランケート型直列乗算器の一構成法

3 . 学会等名

第71回電気・情報関連学会中国支部連合大会

4.発表年

2020年

1.発表者名

辻明里, 近藤真史, 永田将大, 横川智教, 佐藤洋一郎

2 . 発表標題

メタステーブル動作に基づいて承認信号を動的に譲渡する非同期式ツリーアービタの一構成法

3. 学会等名

第71回電気・情報関連学会中国支部連合大会

4.発表年

2020年

| 1.発表者名<br>永田将大,近藤真史,池田大地,茅野功,横川智教,佐藤洋一郎           |

|---------------------------------------------------|

|                                                   |

| 2 . 発表標題<br>冗長な零乗算を省略可能な非同期式直列乗算器の一構成法            |

| 3.学会等名                                            |

| 第19回情報科学技術フォーラム(FIT2020)                          |

| 4 . 発表年<br>2020年                                  |

| 1.発表者名<br>永田将大,近藤真史,茅野功,横川智教,有本和民,佐藤洋一郎           |

| 2.発表標題<br>デジタル補聴器用DSPを対象とした休止相の隠蔽による非同期式直列乗算器の高速化 |

| 3 . 学会等名<br>電子情報通信学会技術研究報告(CAS)                   |

| 4 . 発表年<br>2019年                                  |

| 1.発表者名<br>恵谷大陸,近藤真史,岡本大地,茅野功,永田将大,横川智教,佐藤洋一郎      |

| 2 . 発表標題<br>最大積からの逐次減法に基づく直列乗算器の基礎検討              |

| 3 . 学会等名<br>第70回電気・情報関連学会中国支部連合大会                 |

| 4 . 発表年<br>2019年                                  |

| 1.発表者名<br>近藤真史,茅野功,佐藤洋一郎,横川智教                     |

| 2 . 発表標題<br>非同期式回路に基づく医用デジタル機器の超低消費電力化            |

| 3 . 学会等名<br>第24回岡山リサーチパーク研究・展示発表会                 |

| 4.発表年<br>2019年                                    |

|                                                   |

| 1.発表者名<br>永田将大,近藤真史,池田大地,茅   | 野功,横川智教,佐藤洋一郎         |    |

|------------------------------|-----------------------|----|

| 2 . 発表標題<br>最大積からの逐次減法に基づく直列 | 乗算器とその負数演算手法          |    |

| 3.学会等名<br>電子情報通信学会技術研究報告(CAS |                       |    |

| 4 . 発表年<br>2020年             |                       |    |

|                              |                       |    |

| 1.発表者名<br>永田将大,近藤真史,伊丹聖貴,池   | 田大地,茅野功,横川智教,佐藤洋一郎    |    |

| 2.発表標題<br>逐次減算に基づく直列乗算器を用い   | たFIRフィルタの設計と実装        |    |

| 3.学会等名<br>2020年電子情報通信学会総合大会  |                       |    |

| 4 . 発表年<br>2020年             |                       |    |

| 〔図書〕 計0件                     |                       |    |

| 〔産業財産権〕                      |                       |    |

| 〔その他〕                        |                       |    |

| -                            |                       |    |

| 6 . 研究組織                     |                       |    |

| 氏名<br>(ローマ字氏名)<br>(研究者番号)    | 所属研究機関・部局・職<br>(機関番号) | 備考 |

|                              |                       |    |

7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|