# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成24年5月15日現在

機関番号: 1 4 5 0 1 研究種目:基盤研究(B) 研究期間:2008~2011 課題番号:20360161

研究課題名(和文) FD-SOIのトータルばらつき抑制効果による

超低電圧動作ディペンダブルSRAM

研究課題名(英文) Super-Low-Operating-Voltage Dependable SRAM

Using Total Variability Suppression Effects in FD-SOI

研究代表者

川口 博 (KAWAGUCHI HIROSHI)

神戸大学・大学院システム情報学研究科・准教授

研究者番号:00361642

研究成果の概要 (和文): グローバルばらつきを抑制する FD-SOI 基板バイアス制御技術とローカルばらつきを動的に補償可能な 7T/14T (7トランジスタ/14トランジスタ) メモリセルを提案した。基板バイアス制御回路は自動的にグローバルばらつきを検知し、適切な基板バイアスを与えることでメモリセルのマージンを最大化させる。150-nm 486-kb FD-SOI SRAM に適用し、基板バイアスを印加しない場合と比較して、FSコーナーにおける動作電圧下限を 0.14V 改善し、0.42V で動作することを確認した。7T/14T ディペンダブルメモリセルの評価としては、150-nm 576-kb FD-SOI SRAM を試作した。14T ディペンダブルモードでは 2 つのメモリセルで 1 ビットの情報を保持することでビットエラーレートを改善し、7T 通常モードに比べてリテンション電圧下限を 0.15V、動作電圧下限を 0.32V 低減させることを確認した。

研究成果の概要(英文): We proposed a substrate bias control scheme for an FD-SOI SRAM that suppresses inter-die variability and a 7T/14T (7-transistor / 14-transistor) memory cell that can be dynamically compensate its intra-die variability. The proposed substrate bias control circuits detect inter-die threshold-voltage variation automatically, and then maximize read/write margins of memory cells to supply the substrate bias. We confirmed that a 150-nm 486-kb FD-SOI SRAM operates at 0.42 V, in which an FS corner can be compared as much as 0.14 V. For the 7T/14T dependable memory cell verification, we fabricated a 150-nm 576-kb FD-SOI SRAM. The 14T dependable mode allocates one bit in a 14T cell and improves its bit error rate. In our measurements, the minimum retention voltage and the minimum operating voltage were reduced by 150 mV and 320 mV in the 14T dependable mode over the 7T normal mode, respectively.

#### 交付決定額

(金額単位:円)

|        |              |             | (====================================== |

|--------|--------------|-------------|-----------------------------------------|

|        | 直接経費         | 間接経費        | 合 計                                     |

| 2008年度 | 1, 900, 000  | 570,000     | 2, 470, 000                             |

| 2009年度 | 7, 300, 000  | 2, 190, 000 | 9, 490, 000                             |

| 2010年度 | 3, 300, 000  | 990, 000    | 4, 290, 000                             |

| 2011年度 | 1,600,000    | 480, 000    | 2, 080, 000                             |

| 総計     | 14, 100, 000 | 4, 230, 000 | 18, 330, 000                            |

研究分野:工学

科研費の分科・細目:電気電子工学、電子デバイス・電子機器

キーワード:SRAM、ディペンダブルVLSI、ばらつき、低電圧動作、FD-SOI

1. 研究開始当初の背景

(1) 情報通信・コンピュータ・交通などの重要な社会インフラはシリコンLSIによって支えられているといっても過言ではない。しか

しながら微細化・大規模化・高性能化が進む LSI では、放射線によるソフトエラーやトラ ンジスタが時間的に劣化する NBTI (negative bias temperature instability) などの物理 的エラーによる信頼性低下が問題となっている。加えて、あまりに複雑化したLSI設計やその製造・検査段階において発生する人為的エラーを完全には排除できない状況となっている。このことは製品がエラーを持ったまま出荷され、さらに偶発的なエラーも加わることを意味しており、もはや完璧に信頼できるLSIは望めない。

(2) 速度・電圧・温度・入出力信号の品質などのあらゆる外部環境を満足して動作することはもう不可能であり、信頼性の低下があってもそれを改善できる機構を持った LSI が望まれている。これがディペンダブル LSI である。

### 2. 研究の目的

- (1) 本研究ではディペンダブル SRAM に着目する。システム LSI においては SRAM の大容量化が進み、現在では総トランジスタ数の90%以上を占めるに至っている。LSI の動作マージンは組み込み SRAM が支配することが多く、本研究では低電源電圧でも高信頼性を維持するディペンダブル SRAM を追求する。ここでは外部環境の指標として電圧を用いているが、提案する SRAM では速度・温度などのその他の外部環境に対しても、高信頼性を確保できることに注意されたい。

- (2) SRAM の高信頼化技術を、2 つの手段でトータルに実現する。

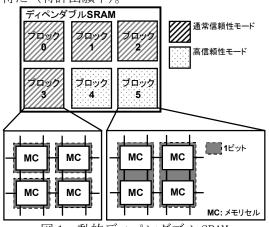

- (3) 最初の手段は1ビットの情報を動的に2個のメモリセルで保持することにより、しきい値のランダム(ローカル)ばらつきを抑制する高信頼性メモリセルである。低電源電圧でも高信頼性を得るために、我々は図1に示すように高信頼性モードでは1ビットの情報を2つのメモリセルで保持するという着想を得た(特許出願中)。

図1 動的ディペンダブル SRAM

1 ビットの情報を 1 個または 2 個のメモリセルで切り替えて保持する。要求する信頼性が

異なるプログラムやデータに対応できるように、SRAMブロックごとに動的にその信頼性を変更するアイデアである。通常の信頼性でよい SRAMブロックでは従来どおり、1メモリセルで1ビットの情報を維持する。しかし2個のメモリセルを結合した高信頼性メモリセルではドライブトランジスタのサイズの増大により、ランダムばらつきを抑制でき、低電源電圧動作を実現できる(ディペンダブルメモリセル)。

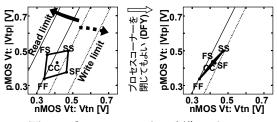

(4) 次の手段はプロセス (グローバル) ばら つき抑制により、更なる高信頼化を図る FD-SOI 基板制御技術である。nMOS のしきい 値 Vtn と pMOS のしきい値 Vtp のバランスを とるように制御する。つまり図2に示すよう にプロセスコーナーをマージン中間点とな る CC (nMOS が Center、pMOS も Center、つま り Vtn= |Vtp|) に収斂させる。プロセスコー ナーFS (nMOS が Fast=Vtn が小さい、pMOS が Slow= | Vtp | が大きい) と SF がなくなるの で、これは SRAM の歩留まり向上に直結する (いわゆる DFY: design for yield)。そのた めには nMOS のしきい値 Vtn を上げ、pMOS の しきい値|Vtp|を下げる、またはその逆の機 能が必要である (CC=Vtn=|Vtp|となることが 望ましい)。具体的にはFD-SOIの埋め込み酸 化膜層 BOX(buried oxide)下部から基板バイ アスを与えることにより、Vtn と Vtp をバラ ンスさせる。

図2 プロセスコーナー制御による 動作マージンの確保

### 3. 研究の方法

- (1) 平成 20 年度には精密な基板バイアスのキャラクタライズのために、実際に実チップ上に TEG (test element group)を作製し、測定した。また基板バイアスにより、nMOS のしきい値 Vtn と pMOS のしきい値 Vtp を同じ値にし、バランスを取ることが低電圧回路動作のために重要であるが、そのためにはプロセスばらつきを基板バイアスでフィードバック制御しながら、センスする回路が設計した。

- (2) 平成21年度、平成22年度には2個のメモリセルの内部ノードを接続する、ディペンダブルメモリセルと多数のメモリセルを敷き詰めたメモリマクロの設計について検討した。単体メモリセルとディペンダブルメモリセルの切り替えをする専用デコーダや低

電源電圧動作センスアンプの設計をした。ディペンダブルメモリセルが単体メモリセル より低電圧特性に優れていることをメモリ マクロにより実証した。

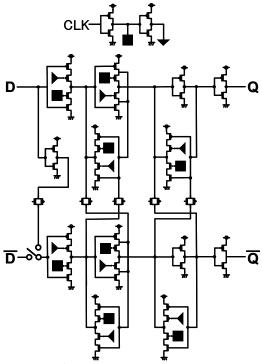

(3) 平成 23 年度には基板バイアス効果やデ ィペンダブルメモリセルのカップリング構 造をフリップフロップに応用した。フリップ フロップは演算器においてレジスタとして 多用されているが、セルライブラリにおいて 最も低電圧安定性が悪いもの1つとされて いる。SRAM における読み出しマージンやリテ ンションマージン (保持特性) と同じく、フ リップフロップでも FS のプロセスコーナー において最低動作電圧が特に高く、低電圧論 理回路設計を阻害している。フリップフロッ プの最低動作電圧を低減するためにディペ ンダブルメモリセルにヒントを得て、2 つの フリップフロップをカップリングさせたデ ィペンダブルフリップフロップを検討した。 2 つのフリップフロップに相補の入力を与え、 内部ノードをトランスミッションゲートで クロスカップリングした。つまり基板バイア ス効果や提案ディペンダブル回路形式をメ モリセルのみならず、フリップフロップへ拡 張した。この回路構成は通常の2倍の面積オ ーバーヘッドを伴うが、アプリケーションに よっては利用価値がある。

#### 4. 研究成果

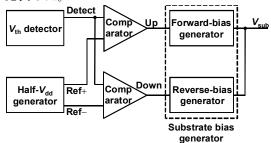

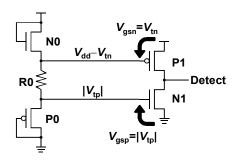

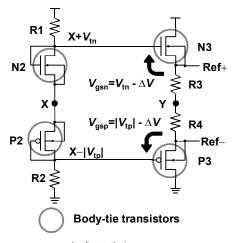

(1) 平成20年度には、0.13ミクロンFD-SOI プロセスにおいて基板バイアス効果のキャ ラクタライズを行い、3Vの基板バイアスによ りしきい値が 0.05V 変動することを確認した。 また自動的にチップ間のしきい値電圧のば らつきを検出し、SRAM の動作マージンが最大 となるように補正を行う基板バイアス制御 回路(図3)の提案を行った。しきい値電圧 検出回路(図4)の出力を0.5Vddと比較すれ ばよいが、このためには安定して、どんなプ ロセスコーナーにおいても中間電圧 0.5Vdd を出力する回路が必要である。つまり基板バ イアスに影響を受けないトランジスタが必 要となる。FD-SOI で基板バイアスを印加する と、原則として全てのトランジスタのしきい 値に影響を与えるが、body tie トランジスタ はボディーを制御できる安定なトランジス タであり、これを 0.5Vdd を出力する、 Half-Vdd 生成回路 (図 5) として利用した。 Body tie トランジスタは面積オーバーヘッド があるため、通常の設計で利用されることは ないが、Half-Vdd 回路などの基準回路として 最適なデバイスで、有用である。また Half-Vdd 回路についてはチップ上に数個あ ればよいと考えられ、心配される面積オーバ ーヘッドは無視できる。提案回路を通常の 6T で構成された 486-kb FD-SOI SRAM (図 6) に

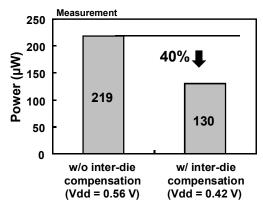

適用し、実測した。基板バイアスを印加しない場合と比較して、動作電圧下限を 0.14V 改善し、0.42V で動作することを確認した。またこの場合において、リーク電力が 40%削減されることを確認した(図 7)。この成果を IEEE International SOI Conference 2008 で発表した。

図3 提案基板バイアス制御回路

図4 しきい値電圧検出回路(Vth detector)

図 5 0.5Vdd 生成回路(Half-Vdd generator)

図 6 486-kb FD-SOI SRAM

図7 リーク電力削減効果

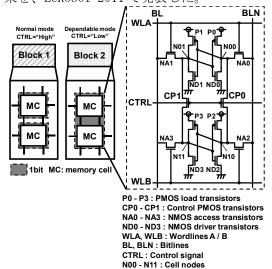

(2) 平成21年度、平成22年度には、新規メモリセルとして、7T/14Tディペンダブルメモリセル(図8)を考案した。2つの従来6Tメモリセルを1組として、双方の内部ノードを追加トランジスタで接続した構成となっている。提案メモリセルは二つの動作モードを持ち、それぞれ通常モード、高信頼性モードである。通常モードにおいて、従来の6TSRMと同様に1ビットのデータを1つのメモリセルで保持する。一方、高信頼性モードにおいて、1ビットのデータを2つのメモリセルで保持することにより、1つのメモリセルで発生するチップ内ばらつきを抑制することが

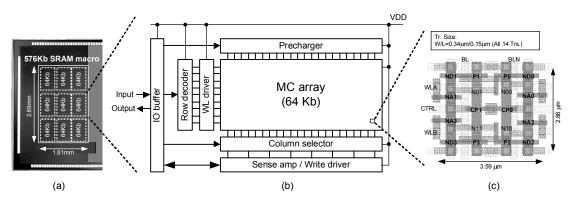

可能である。0.13 ミクロン FD-SOI プロセスを用いて、576-kb 7T/14T ディペンダブル SRAM (図 9) を設計、評価した。提案手法を用いない場合と比較して、リテンション電圧下限を0.15V 改善することを確認した。また、書き込み・読み出しの通常動作では、電圧下限を0.32V 改善することを確認した。この成果を、EUROSOI 2011 で発表した。

図8 7T/14T ディペンダブルメモリセル

図 9 (a) 576-kb 7T/14T ディペンダブル SRAM (b) 64-Kb ブロック図 (c) 7T/14T ディペンダブルメモリセルレイアウト

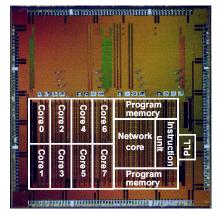

(3) 平成 23 年はディペンダブルフリップフロップ (図 10) を実装し、演算負荷が高い場合には高速で演算でき、演算負荷が低い場合には余剰なハードウェアリソースを利用して低電力動作が可能な SIMD マルチコアプロセッサ (図 11) を設計、測定した。提案アーキテクチャは 8 個の DSP からなり、高速動作時には 8 コア全てが高電源電圧で動作する。対して低電力動作時は 4 コアの DPS のみが動作し、余った残り 4 コアのハードウェアリソースを利用して、低電源電圧動作を達成する。

処理負荷の変動が激しいユビキタス信号処理に向いたものである。65nm プロセスのチップにおいても、ディペンダブルフリップフロップは 0.424V で 1MHz 動作が可能であることを確認した。(また同時に、ディペンダブルSRAM が電源電圧 0.5Vで 1MHz 動作が可能である事を確認した)。ディペンダブル SRAM とディペンダブルフリップフロップの両方を含む提案 DSP アーキテクチャは、0.5V・1MHz で 0.74mW という低消費電力性能を達成した。この成果を、PARMA2012 で発表した。

図10 ディペンダブルフリップフロップ

図11 SIMD マルチコアプロセッサ

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# 〔雜誌論文〕(計9件)

- ① S. Yoshimoto, T. Amashita, S. Okumura, K. Nii, M. Yoshimoto, and H. Kawaguchi, "Bit-Error and Soft-Error Resilient 7T/14T SRAM with 150-nm FD-SOI Process," IEICE Transactions on Fundamentals, 2012, to appear, 査読有り.

- ② S. Okumura, H. Fujiwara, K. Yamaguchi, S. Yoshimoto, M. Yoshimoto, and <u>H. Kawaguchi</u>, "A 0.15-um FD-SOI Substrate Bias Control SRAM with Inter-Die Variability Compensation Scheme," IEICE Transactions on

- Electronics, Vol. E95-C, No. 4, pp. 579-585, Apr. 2012, 査読有り.

- ③ K. Kugata, S. Soda, Y. Nakata, S. Okumura, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "Processor Coupling Architecture for Aggressive Voltage Scaling on Multicores," Proceedings of Workshop on Parallel Programming and Run-Time Management Techniques for Many-Core Architectures (PARMA), pp. 375-384, Feb. 2012, 查読有り.

- ④ 吉本 秀輔、山口 幸介、奥村 俊介、 吉本 雅彦、<u>川口 博</u>、「チップ間ばら つき及びチップ内ばらつきを抑制する 基板バイアス制御回路を備えた 0.42-V 576-Kb 0.15-um FD-SOI 7T/14T SRAM」、 電子情報通信学会技術研究報告、111 巻、 352 号、ICD2011-133、155-160 ページ、 2011 年 12 月、査読無し。

- (5) S. Yoshimoto, T. Amashita, S. Okumura, K. Yamaguchi, M. Yoshimoto, and H. Kawaguchi, "Bit Error and Soft Error Hardenable 7T/14T SRAM with 150-nm FD-SOI Process," Proceedings of IEEE International Reliability Physics Symposium (IRPS), pp. 876-881, Apr. 2011, 查読有り.

- ⑥ K. Yamaguchi, S. Okumura, M. Yoshimoto, and H. Kawaguchi, "0.42-V 576-kb 0.15-um FD-SOI SRAM with 7T/14T Bit Cells and Substrate Bias Control Circuits for Intra-Die and Inter-Die Variability Compensation," Proceedings of Workshop of the Thematic Network on Silicon on Insulator Technology, Devices and Circuits (EUROSOI), pp. 17-19, Jan. 2011, 査読有り.

- ① <u>H. Kawaguchi</u>, "(Invited) Low-Power Control Techniques for Silicon and Organic Circuits with Array Structures," Proceedings of IEEE Conference on Control Applications (CCA), pp. 326-333, July 2009, 査読有り.

- 8 山口 幸介、藤原 英弘、竹内 隆、大竹 優、吉本 雅彦、川口 博、「チップ間ばらつき補正機能を有する基板バイアス制御を用いた 0.42V 動作 486kb FD-SOI SRAM」、電子情報通信学会技術研究報告、108 巻、347 号、ICD2008-127、131-136ページ、2008 年 12 月、査読無し。

- (9) H. Fujiwara, T. Takeuchi, Y. Otake, M. Yoshimoto, and H. Kawaguchi, "An Inter-Die Variability Compensation Scheme for 0.42-V 486-kb FD-S0I SRAM

using Substrate Control," Proceedings of IEEE International SOI Conference, pp. 93-94, Oct. 2008, 査 読有り.

# 〔学会発表〕(計3件)

- (1) 吉本 秀輔、天下 卓郎、奥村 俊介、 山口 幸介、吉本 雅彦、川口 博、「ビットエラー耐性及びソフトエラー耐性 を備えた FD-SOI 7T/14T SRAM」、LSI と システムのワークショップ、2011 年 5 月 17 日、北九州市。

- ② <u>川口 博</u>、「(招待講演) 低電圧・低消費電力 SRAM」、IEEE Solid-State Circuits Society Kansai Chapter Technical Seminar、2009年12月2日、京都市。

- ③ 山口 幸介、藤原 英弘、竹内 隆、大 竹 優、吉本 雅彦、<u>川口 博</u>、「チップ間ばらつき補正機能を有する基板バイアス制御を用いた 0.42V 動作 486kb FD-SOI SRAM」、LSI とシステムのワークショップ、2009 年 5 月 18 日、北九州市。

## [産業財産権]

- ○出願状況(計2件)

- ① 名称:半導体メモリおよびプログラム 発明者:吉本 雅彦、川口 博、藤原 英 弘、奥村 俊介

権利者:財団法人新産業創造研究機構

種類:特許

番号:PCT/JP2009/050086 出願年月日:2009年1月7日 国内外の別:国外。

② 名称: フリップフロップ回路装置及びそれを用いたプロセッサ装置

発明者: 川口 博、吉本 雅彦、久賀田 耕

史、高木 智也、野口 紘希

権利者:株式会社半導体理工学研究センター

種類:特許

番号:特願 2011-125500 出願年月日:2011年6月3日

国内外の別:国内。

#### [その他]

ホームページ

http://www28.cs.kobe-u.ac.jp/ja/research/sram.htm

# 6. 研究組織

(1)研究代表者

川口 博 (KAWAGUCHI HIROSHI) 神戸大学・大学院システム情報学研究科・ 准教授

研究者番号:00361642