#### 研究成果報告書 科学研究費助成事業

今和 6 年 6 月 1 1 日現在

機関番号: 13501

研究種目: 基盤研究(C)(一般)

研究期間: 2020~2023

課題番号: 20K04597

研究課題名(和文)エナジーハーベスティング用間欠動作可能な高効率・広入出力電圧範囲の電源回路の開発

研究課題名(英文)Development of high efficiency and wide input / output voltage range power supply circuit with intermittent operation for energy harvesting

#### 研究代表者

佐藤 隆英 (SATO, TAKAHIDE)

山梨大学・大学院総合研究部・教授

研究者番号:10345390

交付決定額(研究期間全体):(直接経費) 3,400,000円

研究成果の概要(和文): エナジーハーベスティング向けのDC-DCコンバータを開発した。DC-DCコンバータは降圧、昇降圧、昇圧の3つの動作状態を持ち、広い入力出力電圧範囲を有する。主たる電流経路にスイッチが1個のみ存在するため高効率を有する。高効率化に資する制御回路およびその補助電源も提案している。電圧制御方式では、新たな制御回路により出力電圧の過渡変動を抑制し、発振を防いでいる。ヒステリシス制御方式では、誤差増幅器を不要とし、スイッチの駆動電圧を最適化することで効率を改善している。いずれの制御方式においても発電電力が低下した際にはスイッチを遮断することで発電素子とDC-DCコンバータを切り離し間欠動作が可能 である。

研究成果の学術的意義や社会的意義本研究により、高効率かつ広い入力電圧範囲を持つDC-DCコンバータが実現可能であることが示された。数mW程度の電源回路を汎用CMOSプロセスで作成する際には、スイッチの導通損失が効率を制限する問題があった。提案するDC-DCコンバータは、電流経路のスイッチを常に1個にした初の構成であり、従来回路に比べて高効率である。さらに昇圧、降圧、昇降圧の3つの動作状態を有し、広い入力電圧に対応するため、電圧変動の大きいエナジーハーベスト用の電源回路に最適である。提案回路の出力電圧範囲は広く、様々な用途への応用できる。提案回路の利用により、エナジーハーベスティングを用いた新たな装置の開発が加速される。

研究成果の概要(英文): A DC-DC converter for energy harvesting has been developed. This converter operates in three modes: step-down, buck-boost, and boost, covering a wide input-output voltage range. Due to the presence of only one switch in the main current path, it has high efficiency. Control circuits and their auxiliary power source have also been designed. In the voltage control the new control circuit suppresses transient fluctuations in the output voltage, thereby improving efficiency and stability. In the hysteresis control, efficiency is enhanced by eliminating the error amplifier and optimizing the driving voltage of the switch. In both control, when the generated power decreases, the switch can be shut off, disconnecting the generator from the DC-DC converter, allowing intermittent operation.

研究分野:アナログ集積回路設計

キーワード: DC-DCコンバータ スイッチング電源 効率改善 エナジーハーベスト

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

### 1. 研究開始当初の背景

ウェアラブル装置の一層の小型化および軽量化は、生体信号の長期モニタリングを可能とし、病気の早期発見や健康増進などに有用な新たな知見の獲得に有効である。小型な装置の長時間動作には、環境発電(エナジーハーベスティング)による電源供給が適する。しかし、小型の発電素子を用いたエナジーハーベスティングでは発電素子から得られる電力は、電圧の変動が大きいため 昇降圧型、 広い入力電圧範囲、 高効率の特徴を有する電源回路(DC-DC コンバータ)が必須となる。

従来このような用途にはバックブーストコンバータが用いられることが一般的であった。バックブーストコンバータはインバータの両端に 2 個のスイッチを接続した構成であり、入力側または出力側のスイッチのいずれかを交互にオンオフすることで降圧動作または昇圧動作を行うことができる。しかし、以下の問題を有していた。 昇圧および降圧動作のみが実現可能であり、昇降圧動作はできない、 昇圧型の電源回路と降圧型の電源回路の縦続接続のためそれぞれの回路で損失が生じ、効率が低い、 電源回路内部の大電流が流れる経路に複数個のスイッチ数が存在し、効率が低い。バックコンバータとチャージポンプを用いることで特定の条件下での効率を改善した構成が提案されているが完全には解決されていなかった。

以上の背景から、広い入力電圧範囲を有し高効率な新たな昇降圧コンバータの実現が望まれていた。

# 2. 研究の目的

本研究では、エナジーハーベスティングでの利用に適した DC-DC コンバータの開発を目的とした。開発する DC-DC コンバータは、 昇降圧型、 広い入力電圧範囲、 高効率であることが必要である。数値目標として、入力電圧範囲  $0.5V\sim5V$ 、出力電圧範囲  $0V\sim5V$ 、電力効率 90%以上とした。また、発電素子の発電電圧が低い場合に、負荷への電力供給を間欠的に行う構成および制御方法についても検討する。

### 3. 研究の方法

上記の目標を達成するための方法として以下を実施した。

- (1) DC-DC コンバータ内の主たる電流経路上に損失の原因となるスイッチを1個のみ使用する 構成の新たな DC-DC コンバータの提案と動作確認

- (2) 提案する DC-DC コンバータの実現に必要な回路ブロック (制御回路および補助電源回路)の提案。特に、効率に優れた回路ブロックの開発

- (3) 入力電力が負荷の消費電力に至らない場合の間欠動作の検討

### 4. 研究成果

研究の方法(1)~(3)を実施し、それぞれ以下の成果を得た。

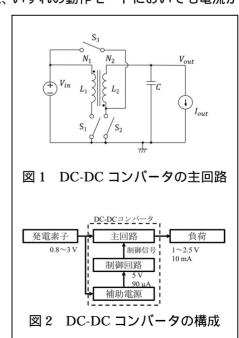

(1) 図1を主回路とする DC-DC コンバータを提案し、その動作を確認した。図1は用いるスイッチの組み合わせにより降圧、昇圧、昇降圧の3種類の動作を実現できる。入力出力電圧に応じて動作モードを切り替えて動作するため、バックコンバータとチャージポンプを組み合わせた昇降圧型の電源回路に比べ入出力電圧範囲が広い。また、いずれの動作モードにおいても電流が

経由するスイッチは1個のみであるため、従来のバックプースコンバータに比べて電力効率に優れることを明らかにした。図1の主回路は、図2のように制御回路および補助電源と共に用いることでDC-DCコンバータとして動作する。理論解析により、3種の動作モードの効率の理論値を求め、降圧および昇圧動作に比べ昇降圧動作時は効率が低いことを明らかにした。これは昇降圧動作では一方の状態のみ負荷に電力を供給するため降圧および昇圧動作に比べ電流が大きくなることに起因する。

- (2) DC-DC コンバータの制御方法として電圧制御および、安定性の補償が不要なヒステリシス制御を導入し、それぞれの制御方法において効率を最適化する回路ブロックを提案した。

- ・電圧制御

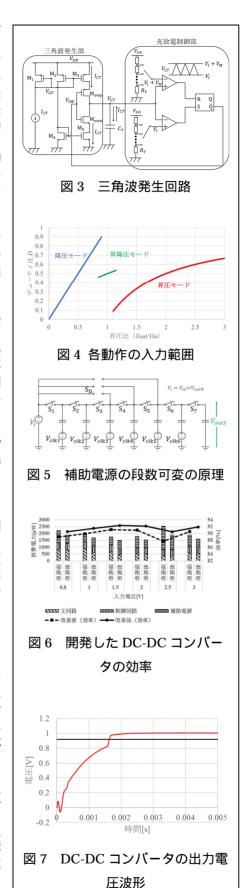

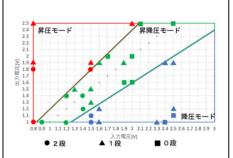

高効率な DC-DC コンバータとするためには昇降圧動作 する動作範囲を制限し、降圧動作または昇圧動作を用い ることが効果的である。また、回路の動作状態が遷移す る際に出力電圧が変動し、意図しない動作状態まで遷移 すると回路は発振状態となることが知られている。昇降 圧動作は降圧動作と昇圧動作の間に存在するため、昇降 圧動作の動作範囲を狭めると出力電圧の過渡的な変動 (オーバーシュートまたはアンダーシュート)により、 降圧動作から昇降圧動作(または昇圧動作から昇降圧動 作)に動作状態が遷移した際に、昇降圧動作を通過し昇 圧動作(または降圧動作)に遷移する現象が生ずる。昇 圧動作への遷移後の出漁電圧は過渡的に所望の値より 大きくなるため、制御回路は、動作状態を昇圧動作から 昇降圧動作に(または降圧動作から昇降圧動作に)戻そ うとする。しかし、動作状態の遷移時に再び出力電圧の 過渡的な変動が生ずるため、動作状態は昇降圧動作を通 過し再び降圧動作(または昇圧動作)となる発振状態と なる。この発振は、従来の制御回路では誤差増幅器から 生成される制御信号が急に変化できないため、動作状態 が変更された場合に駆動信号(PWM信号のデューティ 比)が引き継がれることに起因する。 遷移後の動作状態 に必要となるデューティ比は、遷移前の動作状態で必要 なデューティ比とは異なる。遷移前のデューティ比の制 御信号で遷移後の動作を開始するため、動作状態の遷移 時に制御信号にステップ状の誤差が入力されることに 相当する。この発振は昇降圧動作の動作範囲を過渡的な 変動より広く確保することで抑制することができるが 効率の改善効果が得られない。そこで動作状態の遷移時 に遷移後の動作状態に必要となるデューティ比を出力 可能な制御回路を提案した。制御信号は参照電圧と三角 波を比較して作成しているが、図3の回路を用いて三角 波のバイアス電圧を動作状態に応じて変更し、必要な制 御信号を得ることを可能とした。これにより昇降圧モー ドの動作範囲を必要最低限とすることができ効率が改 善した。図 4 に最終的に定めた各動作の入力範囲を示 す。横軸は出力電圧と入力電圧の比であり、縦軸がその 出力電圧で動作するために必要なデューティ比である。 入出力の電圧が出力電圧の 0.91 から 1.11 の範囲のみで 昇降圧動作を行う。その他の入力範囲では効率に優れる 降圧動作または昇圧動作で動作する。

次に補助電源回路で行った効率改善上の工夫を 2 点 述べる。 第 1 に補助電源回路の入力電圧を DC-DC コン バータの入力電圧またはDC-DCコンバータの出力電圧 のいずれか大きい電圧を選択して用いる構成を導入し た。補助電源はチャージポンプ回路で実現されるが昇圧 の際に各段で損失が生まれるため段数は少ないことが 望ましい。入力電圧をより大きな電圧に動的に変更する ことにより補助電源回路の必要段数を最小とすること ができるため損失の低減が実現される。第二に補助電源 を構成するチャージポンプの段数を入力電圧に応じて 可変とした。入力電圧を変更する構成では補助電源の入 力電圧は大きく変動する。そのためチャージポンプの構 成を図 5 のように構成することで入力電圧が大きく段 数が少なくても昇圧可能な場合には入力側の数段をス イッチでバイパスし少ない段数で動作可能なチャージ ポンプを導入した。また、補助電源回路は間欠動作とし

出力電圧が一定電圧以下となるまで動作を停止させることで一層の効率改善を実現している。

以上の回路技術を導入した DC-DC コンバータの効率のポストシミュレーション結果を図 6 に示す。出力電圧を 1.8 V とし、負荷として 10 mA の定電流源負荷を用いている。入力電圧を変更した際の効率を実践の折れ線グラフ(右軸)に示している。またそれぞれの消費電力の発生場所の内訳を棒グラフで示している。比較のため提案した回路技術を用いない場合の効率を破線で示している。これらの結果から、提案手法の導入により提案する DC-DC コンバータは入力電圧範囲全域にわたり 90%以上の効率が実現されていることがわかる。図 7 に入力電圧として

0.92 V を入力し、出力電圧を 1.0 V に設定した場合の 起動時の出力電圧の過渡応答を示す。時刻 1.8ms 付近 で降圧動作から昇圧動作に切り替わっているが、出力電 圧はオーバーシュートすることなく出力電圧は1.0 V に 収束している。このため回路動作は降圧動作から昇降圧 動作に遷移し昇降圧動作のまま安定して制御されてい ることがわかる。

### ・ヒステリシス制御

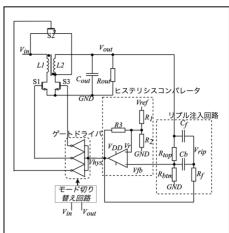

先に述べた電圧制御は誤差増幅器を用いた負帰還構成 であるため安定な制御回路の設計には経験を要する。ま た誤差増幅器には比較的大きな容量が必要となるため 回路規模および消費電力が大きくなる。そこで誤差増幅 器を用いた制御が不要なヒステリシス制御についても 検討をおこなった。ヒステリシス制御は図8に示す回路 で実現した。微小な電圧変動の下でヒステリシス制御を 行うため出力電圧のリプルを模擬した信号をコンパレ ータに入力し制御するリプル注入技術を用いている。そ の他の回路ブロックについても設計を行っている。特に DC-DC コンバータが所望の出力電圧となるまでの過渡 状態において制御不能状態に陥らないための制御方法 を提案している。これによりヒステリシス制御の DC-DC コンバータも間欠動作が可能となった。また、これ までのスイッチング電源回路では、MOS スイッチを駆 動する駆動信号の電源電圧は仕様素子の耐圧が許容す る最大電圧を用いることが回路設計の定石であった。こ の場合、スイッチにおける導通損失は最小とすることが できるが、スイッチのゲート容量を充放電する損失が大 きくなる。この点に着目し主回路部分の導通損失だけで はなく充放電損失も考慮した回路全体の損失が最小化 となる補助電源の必要段数(補助電源の出力電圧)を求 めた。その結果を図9に示す。補助電源の出力電圧を低

図 8 ヒステリシス制御を実現する回路構成

図 9 消費電力を最小とする補助 電源の段数

くすることで導通損失が増加する一方でスイッチの駆動回路における損失を低減できるため DC-DC コンバータ全体では効率が改善される。これらの技術を導入することにより、入力電圧 全域にわたり 87%以上の効率が実現可能であることを示した。

(3) 電圧制御およびヒステリシス制御いずれの制御方式においても入出力電圧を監視し、発電素子が負荷に必要となる電力を供給できない場合には主回路部分に内蔵されているスイッチを遮断することで発電素子と DC-DC コンバータを切り離すことが可能である。負荷に電力を供給しない間に発電素子から得られる電力を蓄電素子に蓄えるための二次電池の充放電制御回路と組み合わせることで間欠動作が可能となる。具体的な応用により充電素子に適する蓄電素子が変わるため安全かつ高効率な充放電制御回路の構成は今後の検討課題である。現状では DC-DC コンバータを実現するためチップ内の MOSFET でスイッチを構成する場合、スイッチの導通損失および駆動するための充放電に要する損失が大きい。 MEMS などの MOSFET 以外の代替素子は現状では損失、動作速度、耐用回数の点で MOSFET のスイッチを置き換えることは難しい。今後の新たな素子の登場に期待する。

#### 5 . 主な発表論文等

〔雑誌論文〕 計0件

| ( 学会発表 ) | 計7件 | (うち招待護演     | 0件/うち国際学会  | 1件)    |

|----------|-----|-------------|------------|--------|

| し十五九化」   |     | し ノンコロ 可明/宍 | 0斤/ ノン国际十五 | ידוי ד |

1.発表者名

坂本恵亮 佐藤 隆英, 小川 覚美

2 . 発表標題

3種の動作モードを有するDC-DCコンバータの開発

3.学会等名

電気学会 電子回路研究会

4.発表年

2022年

1.発表者名

向井一輝 佐藤 隆英, 小川 覚美

2 . 発表標題

ディクソン型チャージポンプを用いた低消費電力の容量・ディジタル変換器

3 . 学会等名

電気学会 電子回路研究会

4.発表年

2022年

1.発表者名

廣永駿輔、佐藤隆英、小川覚美

2 . 発表標題

スイッチング電源回路の補助電源用チャージポンプの小面積化および効率改善

3 . 学会等名

第34回 回路とシステムワークショップ

4 . 発表年

2021年

1.発表者名

柳直弥、佐藤隆英、小川覚美

2 . 発表標題

3種の動作モードを有するDC-DCコンバータのヒステリシス制御

3 . 学会等名

第28回 電気学会東京支部山梨・静岡東部支所研究発表会

4.発表年

2021年

| 1 | <b> </b> |

|---|----------|

|   | . жир б  |

Takahide Sato, Satomi Ogawa, Yutaka Tamura

# 2 . 発表標題

Step-up/step-down DC-DC converter whose current passes through only one switch

### 3 . 学会等名

2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS) (国際学会)

### 4.発表年

2020年

### 1.発表者名

廣永駿輔 佐藤隆英 小川覚美

### 2 . 発表標題

エナジーハーベスト用昇降圧電源回路に適した補助電源回路の開発

#### 3.学会等名

令和2年度第27回静岡東部・山梨支所合同研究発表会

### 4.発表年

2020年

### 1.発表者名

廣永駿輔 佐藤隆英 小川覚美

### 2 . 発表標題

チャージポンプの入力電圧源の切り替えによる小面積化および段数可変による効率改善

# 3 . 学会等名

電子情報通信学会 回路とシステム研究会

### 4.発表年

2021年

## 〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6.研究組織

| 0 | 7. 7. 7. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. |                       |    |

|---|-------------------------------------------------|-----------------------|----|

|   | 氏名<br>(ローマ字氏名)<br>(研究者番号)                       | 所属研究機関・部局・職<br>(機関番号) | 備考 |

### 7. 科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

# 8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|