# 科学研究費補助金研究成果報告書

平成23年 6月 1日現在

機関番号: 1 2 6 0 8 研究種目: 若手研究(B) 研究期間: 2009 ~ 2010 課題番号: 21760253

研究課題名(和文) MOVPE 選択再成長ソース領域による皿-V族 MOSFET の高駆動能力化 研究課題名(英文)High performance III-V MOSFETs using MOVPE selectively regrown source

研究代表者

金澤 徹 (KANAZAWA TORU)

東京工業大学・大学院理工学研究科・助教

研究者番号: 40514922

#### 研究成果の概要(和文):

将来の論理回路応用が期待される III-V 族 MOSFET の高電流動作を目指して、電子注入能力向上・寄生抵抗低減のため、有機金属気相成長法によって再成長した InGaAs ソース /ドレイン層を有する MOSFET 素子を作製した。チャネル長を 170 nm まで縮小化したデバイスで、最大 1.3 A/mm の高ドレイン電流と 0.8 S/mm の伝達コンダクタンスを実現した。この電流値は高移動度 III-V 材料としては非常に高い値であり、III-V 族チャネルによる高電流動作への再成長ソース構造の有効性を示す結果である。

#### 研究成果の概要 (英文):

III-V high mobility channels are a promising technology for future logic applications. To enhance the current injection and reduce the series resistance, heavily doped source/drain structures were formed by MOVPE regrowth. The maximum drain current of 1.3 A/mm and transconductance of 0.8 S/mm were obtained for the regrown souce/drain MOSFET with the channel length of 170 nm. The results show that regrown source is an effective way to improve the drain current of III-V MOSFETs.

## 交付決定額

(金額単位:円)

|         | 直接経費        | 間接経費        | 合 計         |

|---------|-------------|-------------|-------------|

| 2009 年度 | 1, 900, 000 | 570, 000    | 2, 470, 000 |

| 2010 年度 | 1, 500, 000 | 450, 000    | 1, 950, 000 |

| 年度      |             |             |             |

| 年度      |             |             |             |

| 年度      |             |             |             |

| 総計      | 3, 400, 000 | 1, 020, 000 | 4, 420, 000 |

研究分野:工学

科研費の分科・細目:電気電子工学、電子デバイス・電子機器

キーワード: MOSFET、高移動度チャネル、III-V族半導体、MOVPE

#### 1. 研究開始当初の背景

シリコン集積回路の高速化・高集積化はこれまで構成要素である MOS 電界効果トランジスタ(FET)の微細化(スケーリング)によって実現されてきた。しかしながら、近年では物性に起因する性能限界により単純なスケーリングのみでは要求される高性能化が困難となり、新たなブレークスルー技術が必要と

されている。

その一つが高移動度チャネル材料の導入であり、InGaAs をはじめとするⅢ-V族半導体は高い電子移動度と小さな有効質量から、n型 MOSFET のチャネル材料として期待され、近年盛んに研究がおこなわれている。

モンテカルロシミュレーションの報告によれば、チャネルの高駆動能力を発揮するため

にはソース/ドレインの高い電子濃度(~10<sup>20</sup> cm<sup>-3</sup>)が重要である。一方で、Ⅲ-V族材料は固溶限が比較的低いこと、高温での活性化に適さないこと等により Si プロセスで用いられるイオン打ち込み法では高濃度のドーピングが困難であるという問題がある。

そこで高濃度ドーピング実現のためにソース/ドレインを分子線エピタキシー法によって成長する手法が提案されている。

#### 2. 研究の目的

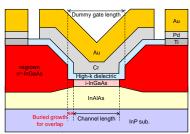

本研究課題の目的は MOSFET の高電流動作に必要なソース領域における高キャリア濃度を実現するため、高濃度ドーピングが可能な MOVPE 再成長によるソース/ドレイン形成を行い高駆動能力を実現することである。本研究で用いる構造を以下の図1に示す。

図1 デバイス構造模式図

MOVPE 再成長により形成した n+-InGaAs 層と、寄生抵抗低減を目的とした横方向埋め込み成長により形成されたソース領域とゲート電極のオーバーラップ、III-V 族薄膜チャネル構造を有しており、ゲート絶縁膜としては高誘電率材料を用いる。上記構造の実現のために以下の二つのステップを目指して取り組みを進めた。

(1) 再成長 MOSFET 作製プロセスの確立 第一の研究目的は再成長ソース/ドレイン層 を有するデバイスの作製プロセスを確立し、 その動作を実現することである。

#### (2) 高駆動能力動作の実現

再成長ソース/ドレイン構造を有するデバイスの動作を達成した後には、これらと適切なチャネル層構造、ゲートスタック構造およびチャネル長スケーリング等の技術を組み合わせた素子作製を行い、高電流動作の実現を目指す。

### 3. 研究の方法

#### (1)再成長型 MOSFET の作製

まず研究の初期段階としてチャネル長 2 μm の構造を用いて再成長ソース構造の形成を目指した。作製プロセスとしてチャネル上に形成した SiO<sub>2</sub> ダミーゲートを用いた MOVPE 選択再成長を提案し、各種の条件を調査した。また、ゲート電極とのオーバーラップ形成の

ためチャネル部へ形成したアンダーカット内への横方向埋め込み成長を行った。

#### (2) チャネル長のスケーリング

III-V 族チャネルにおいてもチャネル長の縮小化はなお重要であり、再成長ソースの効果は駆動能力が高くなる極微細チャネル構造において、より大きな効果を発揮することが期待される。電子ビーム露光を用いたダミーゲート形成を行うことで、ゲート長をサブミクロンオーダーまでスケーリングし駆動能力の改善を目指した。

#### (3) 高誘電率絶縁膜の導入

ゲート容量の増加と界面準位密度低減のため、誘電率が $SiO_2$ の二倍以上と大きい $Al_2O_3$ をセルフクリーニングと呼ばれる表面改善効果が顕著に見込める原子層堆積(ALD)法によって作製することを試みた。

また、併せて堆積前の表面処理条件や、堆積 後およびゲート電極蒸着後のアニールに依 存する絶縁膜および界面の品質を調査した。

## (4) 高電流動作の実現

(1)~(3)によって得られた技術を集約して高誘電率絶縁膜とサブミクロンチャネル構造、再成長ソース構造を併せ持ったデバイスの作製を行い、高電流動作を実現することを目指した。

#### 4. 研究成果

## (1) 再成長型 MOSFET の動作確認

ダミーゲートを用いた選択再成長によって 形成されたソース/ドレイン領域と SiO<sub>2</sub> ゲート絶縁膜を有する MOSFET を作製し、特性の 評価を行った。再成長層のドーピング濃度は 18 乗未満であり不十分であったものの、チャネル部アンダーカットへの横方向埋め込み 成長と MOSFET 動作を確認することができた。

## (2) 高電子濃度ソースの再成長

再成長ソース/ドレインの成長条件に関して温度条件の修正、In/Ga 組成比の調整、 $Si_2H_6$  流量の増加といった最適化を行うことによって、最大で $5\times10^{19}$  cm $^{-3}$  までのキャリア濃度が得られることを確認した。これは III-V 族材料の固溶限を上回り、イオン打ち込み法では達成困難な値である。さらに成長時の流速を 3 m/s 程度とすることで、再成長層へのクラックの発生を抑制し、平坦性の向上が見込めることを明らかとした。

#### (3) サブミクロンデバイスの作製

駆動能力の向上を目指して、電子ビーム露光 によってダミーゲートを形成しサブミクロ ンスケールのチャネル長を有するデバイス

の作製を行った。ゲート絶縁膜として 20 nm と厚いSiO₂を用いたにもかかわらず、最大で 0.8 A/mm のドレイン電流、0.5 S/mm の伝達コ ンダクタンスという良好な特性が得られ、寄 生抵抗に関しても再成長を行わなかった場 合と比較して最大 70%程度の削減が見込め ることが明らかとなった。

#### (4) Al<sub>2</sub>O<sub>3</sub> ゲート絶縁膜の評価

MOS キャパシタ構造および再成長を用いな い簡易な MOSFET 構造を用いて ALD 法によ り堆積した Al<sub>2</sub>O<sub>3</sub> 絶縁膜の性質を評価した。 8~9 の比誘電率と膜厚 10 nm での低いリーク 電流から SiO2 の場合と比較して 1/4 程度まで 等価絶縁膜厚を薄くし、絶縁膜容量を改善す ることができた。実際のデバイス特性におい ても伝達コンダクタンスは二倍程度まで向 上した。さらにゲート電極蒸着後に 350°C、 90s という条件でアニールを行うことでSS に 関しても SiO<sub>2</sub> で 1 V/dec 以上であったのが 200 mV/dec 程度まで向上し、界面準位密度が 低減されていることを示唆する結果を得た。

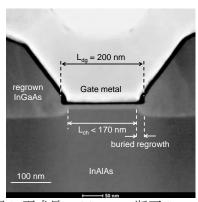

(5) 再成長ソースを用いた高電流動作の実現 本研究課題で取り組んだ駆動能力向上のた めの各々の技術を組み合わせたデバイスの 作製を行った。MOVPE 埋め込み再成長を行 って作製した III-V MOSFET の断面 SEM 像を 以下の図2に示す。

図 2 再成長 MOSFET の断面 SEM 像

再成長を行った InGaAs とチャネル領域が空 隙なくコンタクトしていることと、Cr/Al<sub>2</sub>O<sub>3</sub> 7.5 nm/InGaAs 12 nm というゲートスタック 構造が確認された。チャネル長はダミーゲー ト長 200 nm と埋め込みアンダーカット長 15 nm から真性部チャネル長は約 170 nm であ ることが分かった。また、再成長層のキャリ ア濃度はホール測定から 2.6×10<sup>19</sup> cm<sup>-3</sup>以上と 求められた。

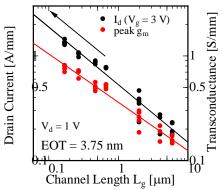

作製したデバイスの電流電圧特性を図3に示 す。最大ドレイン電流はゲート電圧3Vドレ イン電圧1Vという条件において1.34 A/mm

であった。これは高移動度Ⅲ-V族半導体を用 いた FET としては世界的に見てもこれまで の報告(1~1.23 A/mm)を上回る値である。伝達 コンダクタンスに関してもドレイン電圧 0.65 V において 0.8 S/mm 以上という良好な値が 得られた。チャネルの電子移動度は伝達コン ダクタンスと絶縁膜容量を用いて 1,690 cm²/Vs と見積もられこれは一般的な Si の値 と比較して優れた値である。

図3 再成長 MOSFET の電流特性

本デバイスの高駆動能力ははソース領域 の高電子濃度と Al<sub>2</sub>O<sub>3</sub> サイドウォール下部へ の横方向埋め込み成長を用いたオーバーラ ップ形成とそれに伴う寄生抵抗削減の結果 と考えられる。なお、寄生抵抗は現在 $0.5~\Omega$ mm 程度であり、ソース/ドレイン金属と半導 体間の寄生抵抗によるところが大きい。寄生 抵抗を考慮してデバイスの真性伝達コンダ クタンスを評価した場合、1.3 S/mm 以上の値 が見込まれることから、寄生抵抗を削減する ことでさらなる駆動能力の向上が見込める。 駆動能力のチャネル長依存性について以

下の図4に示す。スケーリング則に従った良 好な駆動能力の向上が確認された。高電流領 域においてもソースの高い電子濃度により キャリアの枯渇による性能劣化を防ぐこと ができていると考えられる。また、50 nm 程

度までのチャネル長縮小を行うことにより 国際半導体ロードマップが 2020 年頃の目標 値としているドレイン電流 2 A/mm を実現で きる可能性があることも示されている。

図 4 MOSFET 駆動能力のチャネル長依存性

以上の成果により、提案した再成長ソース/ドレイン構造を有する MOSFET の試作とプロセスの確立を行うことができた。また、これを用いることで III-V 族高移動度チャネルとしては非常に高いドレイン電流を実現し、本研究課題で用いた再成長ソース/ドレインの優位性を示すことができた。また、今後 100 nm 以下へのチャネル長スケーリングと絶縁膜容量の増加、コンタクト抵抗の低減等により、さらなる性能向上が見込める。

#### 5. 主な発表論文等

[雑誌論文] (計 2 件)

- ① R. Terao, <u>T. Kanazawa</u>, S. Ikeda, Y. Yonai, A. Kato, Y. Miyamoto, "InP/InGaAs Composite Metal-Oxide-Semiconductor Firld-Effect Transistors with Regrown Source and  $Al_2O_3$  gatedielectric Exhibiting Maximum Drain Current Exceeding 1.3 mA/ $\mu$ m", Applied Physics Express, vol. 4, pp. 054201-1-3, 2011, 查読有り

- ② <u>T. Kanazawa</u>, K. Wakabayashi, H. Saito, R. Terao, S. Ikeda, Y. Miyamoto, K. Furuya "Submicron InP/InGaAs Composite-Channel Metal-Oxide-Semiconductor Field-Effect Transistor with Selectively Regrown n<sup>+</sup>-Source", Applied Physics Express, vol. 3, pp. 094201-1-3, 2010, 查読有り

#### [学会発表](計 17 件)

① 金澤徹、寺尾良輔、山口裕太郎、池田俊介、米内義晴、加藤淳、宮本恭幸、「裏面電極を有するⅢ-V族量子井戸型チャネルMOSFET」、電子情報通信学会 電子デバイス研究会、2011年1月14日、東京

- ② Y. Miyamoto, H. Saito, <u>T. Kanazawa</u>, "Submicron-channel InGaAs MISFET with epitaxially grown source", 10th IEEE Int. Conf. Solid-State and Integrated Circuit Technology (ICSICT-2010), 2010/11/3, Shanghai, China

- ③ T. Kanazawa, R. Terao, Y. Yamaguchi, S. Ikeda, Y. Yonai, Y. Miyamoto, "InP/InGaAs MOSFET with back-electrode structure bonded on Si substrate using a BCB adhesive layer", 2010 Int. Conf. Solid State Devices and Materials (SSDM 2010), 2010/9/22, Tokyo

- <u>T. Kanazawa</u>, "InP/IGaAs Quantum Well Channel MOSFET Bonded on Silicon Substrate", 2nd Japanese-Russion Young Scientists Conf. Nano-Materials and Nano-Technology, 2010/9/21, Tokyo

- ⑤ 金澤徹、寺尾良輔、山口裕太郎、池田俊介、米内義晴、加藤淳、宮本恭幸、「Si 基板上貼付された裏面電極付 InP/InGaAs MOSFET」、第71回応用物理学会学術講演会、2010年9月14日、長崎

- 6 寺尾良輔、金澤徹、池田俊介、米内義晴、加藤淳、宮本恭幸、「Al<sub>2</sub>O<sub>3</sub> ゲート絶縁膜および再成長ソースを有するサブミクロン InP/InGaAs n-MOSFET」、第71回応用物理学会学術講演会、2010年9月14日、長崎

- 7 Y. Miyamoto, T. Kanazawa, H. Saito, K. Furuya, "InGaAs/InP MISFET with epitaxially grown source", 2009 Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (AWAD), 2010/06/25, Busan

- (8) Y. Miyamoto, <u>T. Kanazawa</u>, H. Saito, "InGaAs MISFET with epitaxially grown sourcce", The 3rd Int. Symp. Prganic and Inorganic Electronic Materials and Related Nanotechnologies (EM-NANO 2010), 2010/6/23, Toyama

- T. Kanazawa, K. Wakabayashi, H. Saito, R. Terao, T. Tajima, S. Ikeda, Y. Miyamoto, K. Furuya, "Submicron InP/InGaAs composite channel MOSFET with selectively regrown n<sup>+</sup>-source/drain buried in channel

undercut", The 22nd Int.Conf. Indium Phosphide and Related Materials (IPRM 2010), 2010/6/1, Takamatsu

- ⑩ 金澤徹、若林和也、斎藤尚史、寺尾良輔、 池田俊介、宮本恭幸、古屋一仁、「Ⅲ-V 族サブミクロンチャネルを有する高移動 度 MOSFET」、電気学会 電子デバイス研究 会,2010年3月26日,東京

- ① 若林和也、金澤徹、斎藤尚史、寺尾良輔、池田俊介、宮本恭幸、古屋一仁、「再成長ソースを有するサブミクロン InP/InGaAs nMOSFET の電流電圧特性」、第 57 回応用物理学会関係連合講演会,2010年3月19日、平塚

- ① 寺尾良輔、金澤徹、斎藤尚史、若林和也、 池田俊介、宮本恭幸、古屋一仁、「Al<sub>2</sub>0<sub>3</sub> ゲート絶縁膜を用いた InP/InGaAs チャ ネル n-MOSFET の電気特性」、第 57 回応用 物理学会関係連合講演会, 2010 年 3 月 19 日, 平塚

- ① 金澤徹、若林和也、斎藤尚史、田島智宣、 池田俊介、宮本恭幸、古屋一仁、「Al<sub>2</sub>O<sub>3</sub> ゲート絶縁膜を用いた InP/InGaAs コン ポジットチャネル MOSFET」電子情報通信 学会 電子デバイス研究会, 2010 年 1 月 14 日, 東京

- T. Kanazawa, H. Saito, K. Wakabayashi, T. Tajima, R. Terao, Y. Miyamoto, and K. Furuya, "Fabrication of InP/InGaAs Undoped Channel MOSFET with Selectively Regrown N<sup>+</sup>-InGaAs Source REgion", 2009 Int. Conf. Solide State Devices and Materials (SSDM 2009), 2009/10/7, Sendai

- (5) 若林和也、金澤徹、斎藤尚史、寺尾良輔、田島智宣、宮本恭幸、古屋一仁「再成長ソースを有するアンドープチャネル MOSFET」、第70回応用物理学会学術講演会、2009年9月8日、富山

- ⑩ 金澤徹、斎藤尚史、若林和也、寺尾良輔、 田島智宣、池田俊介、宮本恭幸、古屋一 仁、「MOVEP 再成長 n<sup>+</sup>-ソースを有するⅢ-V族高移動度チャネル MOSFET」、電気学 会 電気・情報・システム部門大会、2009 年9月4日、徳島

- T. Kanazawa, K. Wakabayashi, H. Saito, R. Terao, T. Tajima, S. Ikeda, Y. Miyamoto, K. Furuya, "InP/INGaAs-channel MOSFET with

MOVPE Selective Regrown Source", The 21st Int .Conf. Indium Phosphide and Related Materials (IPRM 2009), 2009/5/13, Newport Beach, USA

〔図書〕(計 件) 〔産業財産権〕 ○出願状況(計 1 件)

名称:電界効果トランジスタ 発明者:宮本恭幸、金澤徹 権利者:東京工業大学

種類:特許

番号: 特願 2010-204769

出願年月日: 平成22年9月13日

国内外の別:国内

6. 研究組織

(1)研究代表者

金澤 徹 (KANAZAWA TORU)

東京工業大学・大学院理工学研究科・助教

研究者番号: 40514922