# 科学研究費助成事業 研究成果報告書

令和 6 年 6 月 2 6 日現在

機関番号: 14301 研究種目: 若手研究 研究期間: 2021~2023

課題番号: 21K14209

研究課題名(和文)SiC集積回路の超広温域における論理閾値電圧安定化

研究課題名(英文)Logic threshold voltage stabilization in silicon carbide integrated circuits within a wide temperature range

### 研究代表者

金子 光顕 (Kaneko, Mitsuaki)

京都大学・工学研究科・助教

研究者番号:60842896

交付決定額(研究期間全体):(直接経費) 3,500,000円

研究成果の概要(和文):本研究では高温・高圧・放射線などの厳環境で動作する集積回路の開発に向け、ワイドギャップ半導体である炭化ケイ素 (SiC) による接合型電界効果トランジスタで構成された相補型回路(相補型JFET)の論理閾値電圧の安定化を目指した。JFETの閾値電圧を決定するイオン注入原子の横方向拡散量を結晶学的およびデバイス工学的に同定  $(0.4+0.5\,\mu\text{m})$  した。nチャネルJFETのチャネル領域に深いドナーを使用することを提案、ホール効果測定を行うことでドーパントとして硫黄が適していることを見出した。実際に硫黄ドープnJFETで構成された相補型JFETを作製し、室温 -200 での論理閾値電圧の安定化を実証した。

研究成果の学術的意義や社会的意義イオン注入はパワーデバイスを作製する際にも必須の工程であり、得られた横方向拡散量はパワーデバイス設計にも有用である。一般的に、イオン化エネルギーの大きい深いドナーはデバイス応用上不利と考えられており、その研究はあまり行われていなかい。特に、SドープSiC層を電子デバイスに適用した報告は1報に限られており、その理解が進んでいなかった。本研究では、相補型JFETにSドープSiC層を世界で初めて適用し、理論予測通りに論理閾値電圧の変動が抑えられることを証明できた点が意義深い。なお、明らかとなったデバイス特性は他のワイドギャップ半導体におけるデバイス作製の際にも適用可能であるため、その波及効果は高い。

研究成果の概要(英文): In this study, we aimed to stabilize the logic threshold voltage of complementary circuits consisting of junction field-effect transistors made of silicon carbide SiC), in order to develop integrated circuits that can operate in harsh environments. The amount of lateral diffusion of ion implanted atoms, which determines the JFET threshold voltage, was identified by crystallographic and device characterization. The use of deep donors in the channel region of n-channel JFETs was proposed, and sulfur was found suitable as a dopant by performing Hall effect measurements. We fabricated complementary JFETs composed of sulfur-doped nJFETs and demonstrated stabilization of logic threshold voltage from room temperature to 200 .

研究分野: 電子デバイス

キーワード: 炭化ケイ素 電界効果トランジスタ 論理回路

### 1. 研究開始当初の背景

現在主流のシリコン集積回路はn型およびp型の金属-酸化物-半導体(MOS)デバイスを利用している。高温動作に関して、シリコンが約200℃で真性領域に入り、n型とp型の区別がつかなくなるため、それ以上の温度での動作が不可能である。また、高放射線環境下では MOSFET のゲート絶縁膜であるシリコン酸化膜において界面近傍の酸化膜中に酸素空孔などの構造欠陥が存在し、放射線照射で発生したキャリアが欠陥に捕獲されることで閾値電圧がシフトしてしまう。上述のように、厳環境で動作する集積回路は多種多様な応用先が存在するが、既存のシリコン集積回路では材料物性の限界により動作不可能となり、未踏領域となっている。

シリコンの物性限界を打破する方法として、ワイドギャップ半導体の活用が考えられる。ワイドギャップ半導体とは、バンドギャップが広い半導体のことであり、堅牢な半導体材料であることが知られている。ワイドギャップ半導体の中でも、炭化ケイ素(SiC)は例外的に広範囲の n型、p型の伝導型制御が可能なため、集積回路の作製に適した材料である。また、SiC はパワー半導体用材料としても優れた材料物性を有しており、社会実装への強い要求から、学術界・産業界において広く研究開発が進んでいる。一方、パワー半導体用の研究が先行していたため、集積回路の研究は限られているのが現状である。

本研究では、接合型電界効果トランジスタ(JFET)をキーデバイスとして使用し、厳環境で動作する集積回路を開発することを目的とする。JFET はシリコン酸化膜をゲート部に使用しないため、酸化膜の信頼性の問題を回避できる。集積回路の作製はシリコン集積回路の実績から MOS デバイスが第一候補として挙げられるが、JFET により構成する点に独自性がある。

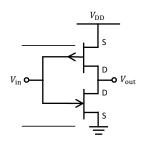

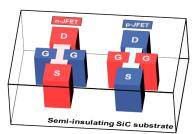

JFET を使用した回路構成として n 型と p 型のノーマリーオフ JFET を使用した相補型の回路構成を提案する(図 1)。相補型回路は静的消費電力が非常に小さく、厳環境の限られた資源における長時間動作が可能となり、実応用を見据えて回路構成を相補型で構成する点に創造性がある。既に、デバイス構造全てをイオン注入で作製することにより n 型および p 型の JFET の同一基板上への作製を行っており(図 2)、ノーマリーオフ型 JFET の室温-400℃動作の実証に成功している。

論理回路の安定動作を行う上で論理閾値電圧の決定および安定化は最重要課題である。図 1 に示したインバータであれば  $0 \rightarrow 1$  もしくは  $1 \rightarrow 0$  へ出力が変化する電圧が論理閾値電圧である。 論理閾値電圧は回路を構成する p チャネル JFET e n チャネル JFET n トランジスタ特性により決定される。トランジスタ特性のうち、最も影響が大きいものが JFET 自身の閾値電圧(回路の論理閾値電圧とは異なる)とドレイン電流である。厳環境で動作させることを考えた場合、温度変化によるデバイス特性の変化が論理閾値電圧の変化を引き起こす。既存のシリコン CMOS 集積回路では徹底した冷却を行うことで大きな温度変化が生じないことを前提にデバイス設計がなされている。シリコン CMOS 集積回路の設計ルールをそのまま本研究で提案している SiC 相補型 JFET 回路に適用すると、温度変化によるデバイス特性の変化を考慮できていないため、論理閾値電圧が大きく変動してしまう(図 3)。そこで本研究では、材料科学・電子デバイス工学的観点でトランジスタ特性を制御することにより室温-400℃の超広温域における論理閾値電圧の安定化を目指す。

図 1: 相補型 JFET インバータ 図 2: 作製した JFET の模式図

図 3: SiC JFET インバータの温 度特性(計算)

# 2. 研究の目的

上述の背景の下、本研究では以下の二つの主要課題について研究を行う。

- 【1】イオン注入チャネリング量の定量評価による閾値電圧制御

- 【2】深いドナーの探索と JFET の n チャネル領域への適用

### 3. 研究の方法

【1】イオン注入チャネリング量の定量評価による閾値電圧制御

SiC ヘイオン注入した Al および P の横方向拡散量の評価を行った。具体的には JFET のデバイス特性によるチャネリング量の導出と走査型電子顕微鏡および走査型静電容量顕微鏡による注入原子の直接観察の二つの方法で行った。

【2】深いドナーの探索と JFET の n チャネル領域への適用

深いドナーの候補として As、Sb、S、O が挙げられる。これらの原子をイオン注入した Hall 素子を作製し、活性化率・イオン化エネルギー等の物性値を評価した。

# 4. 研究成果

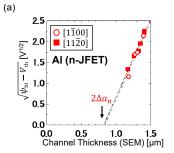

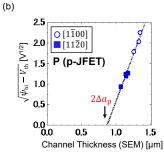

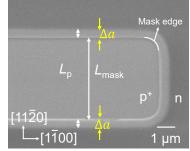

【1】イオン注入チャネリング量の定量評価による閾値電圧制御 nJFET に対して、マスク設計のチャ (a) ネル厚から横方向広がり量を $\Delta a_n$ と すると、nJFET の閾値電圧 $V_{th}$ の理論 式を変形することで、以下の式を導くことができる。

$$\sqrt{\psi_{\rm n} - V_{\rm th}} = \sqrt{\frac{qN_{\rm D}}{8\epsilon_{\rm s}}} (a_{\rm mask} - 2\Delta a_{\rm n})$$

ここで、 $\psi_n$ はゲート部の拡散電位、qは素電荷、 $N_D$ はチャネル部のドーピング密度、 $\epsilon$ 。は SiC の誘電率

図 4: JFET のデバイス特性からの横方向広がり量の導出

である。pJFET の閾値電圧に対しても同様の式を導くことができる。上記の式より、マスク設計のチャネル厚が異なる複数のデバイスの閾値電圧を求めることで $\sqrt{\psi_{\rm n}-V_{\rm th}}-a_{\rm mask}$ をプロットすることができ、その直線の x 軸との交点が  $2\Delta a$ となるため、横方向広がり量を導出することができる。

上記の式を作製した nJFET、pJFET の実験結果に対してそれぞれプロットしたものを図 4 に示す。理論式から予測される通り、比例関係となっていることがわかる。nJFET の結果からは Al、pJFET の結果からは P の横方向広がり量を導出することができる。チャネルを[1 $\bar{1}$ 00]および[11 $\bar{2}$ 0]の二つの方向に沿って形成した結果を示しているが、どちらもほとんど結果が変わらないことがわかる。切片から導出した Al および P の横方向広がり量( $2\Delta a_n$ および $2\Delta a_p$ )はそれぞれ 0.8 および  $0.9~\mu$  m となった。

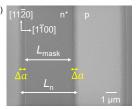

図 5 に Al の横方向拡散観察用ラインアンドスペース試料の表面走査型電子顕微鏡観察像を示す。走査型電子顕微鏡における観察では、p型領域、n型領域はそれぞれ明るい、暗いコントラストで像が得られる。このコントラストからp型領域の幅は  $5.4\,\mu$  m であることがわかる。イオン注入時のマスクの幅の設計値は  $5\,\mu$  m であったが、プロセス誤差が生じるため、直接マスク幅を計測する必要がある。今回は、 $SiO_2$  マスク形成時に SiC がわずかにエッチングされることで実際に形成したマスク幅を SiC 表面の走査型電子顕微鏡観察像から導出することができ、 $4.5\,\mu$  m であることがわかった。以上より、Al の横方向拡散の量は  $0.5\,\mu$  m であることが分かった。

図 6 に P の横方向拡散観察用ラインアンドスペース試料の表面走査型電子顕微鏡観察像を示す。図 5 の (a) [1120] n\*

Alの横方向拡散観察用ラインアンドスペー ス試料と n 型領域、p 型領域の位置が逆転 しているため、コントラストも逆転してい ることがわかる。図6には[1120]および[1 100]両方向の結果を示しており、n型領域の 幅はどちらも  $5.3 \mu m$  となった。一方、イオ ン注入時のマスク幅はそれぞれ 4.4、4.3 μm と なり、P の横方向拡散の量は約  $0.5 \mu m$  である ことがわかった。ここで、[1100]方向に沿って ラインアンドスペースを形成した試料では、 横方向拡散の量に異方性があることがわか り、上部、下部の横方向拡散の量はそれぞれ 0.6、 $0.4 \mu$  m と見積もられた。この非等方的な 横方向拡散は使用した試料が 4°のオフ角を 有していることに起因すると考えられる。SiC の結晶構造に起因して、[0001]方向には注入イ オンがより深くまで入り込むことが知られて いる。そのため、オフ角が存在すると、[0001] 方向に沿って注入イオンが侵入するため、横 方向拡散量に異方性が現れる。

図 5: [1100]方向にラインを形成した試料の表面走査型電子顕微鏡観察像

図 6: [1120]方向にラインを形成した試料の 表面走査型電子顕微鏡観察像

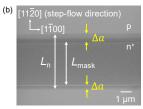

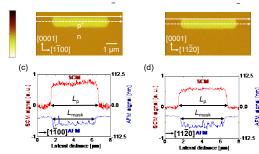

図 7: 断面走査型静電容量顕微鏡による観察像

図 7 に Al の横方向拡散観察用ラインアンドスペース試料の断面走査型静電容量顕微鏡観察像を示す。 $[11\bar{2}0]$ および $[1\bar{1}00]$ 両方向の観察像を示している。p型領域の幅を得るため、図中の点線に沿ったプロファイルを同図に赤線で示す。p型領域に該当する部分では明確に信号強度が変化しており、p型領域の幅は $[11\bar{2}0]$ および $[1\bar{1}00]$ 方向でそれぞれ 5.38、 $5.32 \mu m$  と導出することができた。走査型電子顕微鏡による観察の際と同様に、マスク形成幅を取得するため、同じ試料に対して原子間力顕微鏡により表面プロファイルを取得した。試料表面にあたる図中の直線におけ

る表面プロファイルを同図に青線で示す。断面試料形成時に保護膜を形成しているが、試料表面の研磨時に SiC と保護膜の研磨量が異なるため、表面プロファイルにより SiC の部分と保護膜の部分を切り分けることができる。表面プロファイルから導出したマスク幅は[ $11\bar{2}0$ ]および[ $1\bar{1}00$ ]方向でそれぞれ 4.72、 $4.66 \mu$  m と導出された。

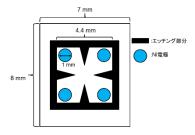

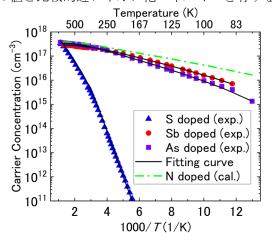

【2】深いドナーの探索と JFET の n チャネル領域への適用 As、Sb、S、O を注入した Hall 素子を作製した。作製した素子の 模式図を図 8 に示す。 n 型基板上の p エピ層へイオン注入を行うことで基板と電気的に絶縁し、注入層のみに電流が流れるような構造とした。ドライエッチングを行うことでクローバーリーフ形の Hall 素子を作製した。Hall 効果測定により求めた As、Sb、S イオン注入層のキャリア密度の温度依存性を図 9 に示す。図 9 には一般的なドナーである N をドープした SiC のキャリア密度の温度依存性も示した。N はイオン化エネルギーが小さいため、室温近傍でほぼ 100% イオン化しており、キャリア密度の温度変化が小さいことがわかる。As、Sb に関してもキャリア密度の温度依存性が小さいため、N と同じく比較的イオン化エネルギーの小さいドナーであることがわかる。-方、S ドープ SiC

図 8: 作製した Hall 素子の 模式図

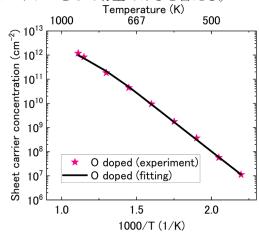

のキャリア密度は室温で注入原子密度よりも 2 桁以上小さく、またその温度依存性も大きいことがわかる。これは、S ドーパントのイオン化エネルギーが大きい事を示唆している。Hall 効果測定により求めた O イオン注入層のキャリア密度の温度依存性を図 10 に示す。SIMS 測定結果より、注入されたドーパントは深さ方向に均一に分布しておらず、注入層の厚さを定義することが困難であったため、シートキャリア密度として評価した。O イオン注入層は室温近傍では測定値が得られなかったため、400K 以上で測定できた結果を示した。シートキャリア密度が温度に依存して大きく変化していることがわかる。室温近傍で測定ができなかった原因としてキャリア密度が小さすぎることが考えられる。以上より、O ドーパントのイオン化エネルギーが大きいことが示唆された。

電荷中性条件の式に基づきフィッティングを行った。フィッティング結果を図 9、10 に線で示す。As、Sb はイオン化エネルギーが 60 meV 程度と N と同じくらい小さいドナーであることがわかる。一方、S、O はそれぞれ 340、900 meV とイオン化エネルギーが大きいことがわかる。 CJFET の p型 JFET に使用する Al のイオン化エネルギーが 200 meV であることを考えると、その値と比較的近いイオン化エネルギーを有する S が深いドナーとして有望であると言える。

図 9: As, Sb, S をイオン注入したした SiC 層 のホール効果測定結果

図 10: O をイオン注入した SiC 層のホール 効果測定結果

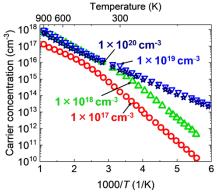

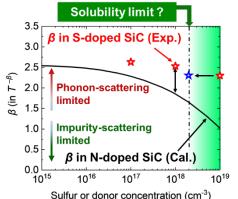

続いて、 $10^{17}\sim10^{20}\,\mathrm{cm}^{-3}$ の S 密度を有する SiC の Hall 効果測定を行った。Hall 効果測定によって得られたキャリア密度の温度依存性を図 11 に示す。 $10^{17}\,\mathrm{および}\,10^{18}\,\mathrm{cm}^{-3}$ の試料について、S 密度の上昇に伴い、同じ温度におけるキャリア密度が上昇していることがわかる。一方、 $10^{19}\,\mathrm{cm}^{-3}$  以上の試料については、S 密度に関わらず  $10^{18}\,\mathrm{cm}^{-3}$  の試料と 300 K 以上の温度範囲でほぼ同じキャリア密度となっていることがわかる。これは、SiC 中の S には固溶限界が存在するため、電気的に活性化している S 密度がいずれも  $2\times10^{18}\,\mathrm{cm}^{-3}$  程度となっていることに起因すると考えられる。得られたキャリア密度の温度依存性は電荷中性条件式によりフィッティングすることができた。

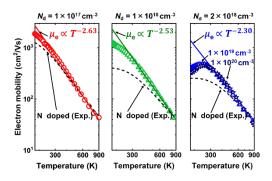

各 S 密度における電子移動度の温度依存性を図 12 に示す。300K 以上の温度範囲において、いずれ の試料においても温度上昇と共に移動度が低下し ていることがわかる。比較のため、N ドープ SiC 中 の電子移動度の温度依存性も同図に示した。室温付 近ではNドープSiCとSドープSiCの移動度の差 が大きいが、高温領域ではその差が小さくなってい る。移動度の温度依存性は、複数の散乱機構のうち、 どの散乱機構が支配的かによって決められており、 温度依存性の片対数プロットの傾きから支配的な 散乱機構を推測することが可能である。この傾きを βとすると、図 12 より各 S 密度における β の値 をフィッティングにより得ることができた。β を S 密度に対してプロットしたものを図 13 に示し た。比較のため、N ドープ SiC におけるβのドー ピング密度依存性も示した。N ドープ SiC では $\beta$ の値がドーピング密度によって大きく異なってお り、低ドーピング密度ではフォノン散乱が、高ド ーピング密度では不純物散乱が支配的であること に起因する。一方、S ドープ SiC では $\beta$  の値がド ーピング密度にほぼ依存しておらず、2.4程度とな っていることがわかる。この値はフォノン散乱が 支配的な散乱機構であるときに得られるものであ る。N ドープ SiC とは異なり、ドーピング密度の 広い範囲でフォノン散乱が支配的であることが わかった。

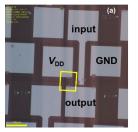

最後に、硫黄を n チャネル JFET のチャネル領域にドープした CJFET インバータを作製した。作製した JFET は全てサイドゲート構造を有する。 JFET の作製は高純度半絶縁性基板へのイオン注入により行った。チャネルのドーピング密度は  $1 \times 10^{17} \, \mathrm{cm}^{-3}$  とした。サイドゲート構造において閾値電圧を決定する横方向広がり量は上記【1】で得られた結果を考慮して設計を行った。作製した CJFET インバータの光学顕微鏡像を図 14 に示す。

先ず、硫黄をドープした n チャネル JFET の電流電圧特性の評価を行った。微小リーク電流が確認されたものの、正常なトランジスタ動作を確認した。閾値電圧の温度依存性を評価したところ、室温~100℃の範囲は理論予測と 0.1V 以下の誤差で一致していたが、温度上昇に伴い理論値との乖離が大きくなった。これは、上記微小リーク電流が温度上昇に伴い増大し、無視できないほど大きくなったことに起因する。このリーク電流により、高温動作限界は 200℃となった。これは、SiCの材料物性から予測される最高動作温度(約800℃)と比較して著しく低い値であるが、この原因は今回使用した半絶縁性基板の絶縁性が低かったことに起因しており、使用する基板の変更およびデバイス構造の改良により解決可能であ

図 11: 様々な S 密度を有するイオン注入 層の Hall 効果測定結果

図 12: 様々な S 密度を有するイオン注入 層の電子移動度の温度依存性

図 13: 様々な S 密度を有するイオン注入 層の β 値

図 14: 作製した CJFET インバータの光学 顕微鏡像

る。次に、室温~200℃の範囲で入出力特性を評価したところ、論理閾値電圧の変化が 0.06V と 非常に小さくなっていることが分かった。これは、一般的なドナーである窒素をドープした場合 と比較して 1/2 以下の小さな値であり、深いドナーをドープすることで論理閾値電圧の変動を抑 制できることを実証した。

# 5 . 主な発表論文等

〔雑誌論文〕 計7件(うち査読付論文 6件/うち国際共著 1件/うちオープンアクセス 0件)

| 〔雑誌論文〕 計7件(うち査読付論文 6件/うち国際共著 1件/うちオープンアクセス 0件)                                       |                 |

|--------------------------------------------------------------------------------------|-----------------|

| 1.著者名                                                                                | 4 . 巻           |

| Kaneko Mitsuaki, Nakajima Masashi, Jin Qimin, Maeda Noriyuki, Kimoto Tsunenobu       | -               |

| 2 . 論文標題                                                                             | 5.発行年           |

| 350 °C Operation of SiC Complementary JFET Logic Gates                               | 2023年           |

| 3.雑誌名                                                                                | <br>6.最初と最後の頁   |

| Proc. of 2023 IEEE CPMT Symposium Japan (ICSJ)                                       | 180, 183        |

| TTOC. OT 2023 TEEE OFMI Symposium Japan (1033)                                       | 100, 103        |

| 掲載論文のDOI (デジタルオプジェクト識別子)                                                             |                 |

| 10.1109/ICSJ59341.2023.10339600                                                      | 無               |

| オープンアクセス                                                                             | 国際共著            |

| オープンアクセスではない、又はオープンアクセスが困難                                                           | -               |

| 1 . 著者名                                                                              | 4 . 巻           |

| 金子 光顕、木本 恒暢                                                                          | J107-C          |

| 2.論文標題                                                                               | 5.発行年           |

| 高温環境での動作を可能にするSiC JFETを用いた相補型論理回路の研究                                                 | 2024年           |

| 3.雑誌名                                                                                | 6.最初と最後の頁       |

| 電子情報通信学会論文誌 C                                                                        | 145 ~ 153       |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                              | <br>  査読の有無     |

| 10.14923/transelej.2023JC10015                                                       | 有               |

| オープンアクセス                                                                             | 国際共著            |

| オープンアクセスではない、又はオープンアクセスが困難                                                           | -               |

| 1 . 著者名                                                                              | 4 . 巻           |

| Kaneko M.、Nakajima M.、Jin Q.、Kimoto T.                                               | 43              |

| 2 . 論文標題                                                                             | 5.発行年           |

| SiC Complementary Junction Field-Effect Transistor Logic Gate Operation at 623 K     | 2022年           |

| 3.雑誌名                                                                                | 6.最初と最後の頁       |

| IEEE Electron Device Letters                                                         | 997 ~ 1000      |

| 掲載論文のDOI (デジタルオブジェクト識別子)                                                             | 査読の有無           |

| 均取30001 (デンタルオフシェクトinkが) ナ )<br>10.1109/LED.2022.3179129                             | 重読の有無   有       |

|                                                                                      |                 |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                               | 国際共著            |

|                                                                                      |                 |

| 1.著者名                                                                                | 4 . 巻           |

| Matsuoka Taiga、Kaneko Mitsuaki、Kimoto Tsunenobu                                      | 62              |

| 2 . 論文標題                                                                             | 5.発行年           |

| Physical properties of sulfur double donors in 4H-SiC introduced by ion implantation | 2023年           |

| 3 . 雑誌名                                                                              | 6.最初と最後の頁       |

| Japanese Journal of Applied Physics                                                  | 010908 ~ 010908 |

| 掲載論文のDOI (デジタルオブジェクト識別子)                                                             | 査読の有無           |

| 10.35848/1347-4065/acb309                                                            | 有               |

| オープンアクセス                                                                             | 国際共著            |

| オープンアクセスではない、又はオープンアクセスが困難                                                           | -               |

| 1.著者名 Kaneko M.、Tsibizov A.、Kimoto T.、Grossner U.                                                                                      | 4.巻<br>70                  |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.論文標題<br>Nearly Ideal Breakdown Voltage Observed in Lateral p-i-n Diodes Fabricated on a SiC High-Purity<br>Semi-Insulating Substrate | 5 . 発行年<br>2023年           |

| 3.雑誌名 IEEE Transactions on Electron Devices                                                                                            | 6 . 最初と最後の頁<br>2153~2156   |

| 掲載論文のDOI (デジタルオブジェクト識別子)<br>10.1109/TED.2023.3245998                                                                                   | 査読の有無<br>有                 |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                 | 国際共著<br>該当する               |

| 1 . 著者名<br>Jin Qimin、Nakajima Masashi、Kaneko Mitsuaki、Kimoto Tsunenobu                                                                 | 4.巻<br>60                  |

| 2.論文標題<br>Lateral spreads of ion-implanted Al and P atoms in silicon carbide                                                           | 5 . 発行年<br>2021年           |

| 3.雑誌名<br>Japanese Journal of Applied Physics                                                                                           | 6.最初と最後の頁<br>051001~051001 |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.35848/1347-4065/abf13d                                                                                   | 査読の有無<br>有                 |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                 | 国際共著                       |

|                                                                                                                                        |                            |

| 1.著者名<br>Takahashi Katsuya、Tanaka Hajime、Kaneko Mitsuaki、Kimoto Tsunenobu                                                              | 4.巻<br>69                  |

| 2.論文標題 Carrier Trapping Effects on Forward Characteristics of SiC p-i-n Diodes Fabricated on High-Purity Semi-Insulating Substrates    | 5 . 発行年<br>2022年           |

| 3.雑誌名 IEEE Transactions on Electron Devices                                                                                            | 6 . 最初と最後の頁<br>1989~1994   |

| 掲載論文のDOI (デジタルオブジェクト識別子)<br>10.1109/TED.2022.3154673                                                                                   | 査読の有無<br>有                 |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                 | 国際共著<br>-                  |

| 〔学会発表〕 計18件(うち招待講演 8件/うち国際学会 11件) 1.発表者名                                                                                               |                            |

| Tsunenobu Kimoto,Keita Tachiki,Kyota Mikami,Mitsuaki Kaneko                                                                            |                            |

| 2. 発表標題<br>Progress of SiC MOSFETs and JFETs beyond Power Applications                                                                 |                            |

|                                                                                                                                        |                            |

3 . 学会等名

4 . 発表年 2023年

IME Workshop on Wide Bandgap Semiconductors 2023 (招待講演) (国際学会)

| - | 7V   |

|---|------|

| 1 | 举表者名 |

Tsunenobu Kimoto, Mitsuaki Kaneko

# 2 . 発表標題

Fundamentals of SiC Complementary MOSFETs and JFETs for Advanced IC Applications

#### 3.学会等名

20th International Conference on Silicon Carbide and Related Materials (ICSCRM2023)(招待講演)(国際学会)

## 4.発表年

2023年

## 1.発表者名

Qimin Jin, Chansoon Koo, Mitsuaki Kaneko, Tsunenobu Kimoto

#### 2.発表標題

Carrier compensating center density in n-type layers formed by ion implantation into high-purity semi-insulating 4H-SiC substrates

## 3.学会等名

20th International Conference on Silicon Carbide and Related Materials (ICSCRM2023)

# 4.発表年

2023年

#### 1.発表者名

Shunya Shibata, Taiga Matsuoka, Mitsuaki Kaneko, Tsunenobu Kimoto

### 2 . 発表標題

Over 600 operation of a bottom-gate p-JFET with double-well structure fabricated by ion implantation on an n-type SiC epilayer

### 3.学会等名

20th International Conference on Silicon Carbide and Related Materials (ICSCRM2023)

## 4.発表年

2023年

## 1.発表者名

Mitsuaki Kaneko, Taiga Matsuoka, Tsunenobu Kimoto

### 2 . 発表標題

A Sulfur-doped n-JFET for a reduced logic threshold voltage shift in a SiC CJFET inverter

# 3 . 学会等名

20th International Conference on Silicon Carbide and Related Materials (ICSCRM2023)

# 4.発表年

2023年

| 1 . 発表者名<br>Manato Takayasu,Taiga Matsuoka,Masahiro Hara,Mitsuaki Kaneko,Tsunenobu Kimoto                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 . 発表標題<br>Carrier transport and barrier height of S+-implanted SiC Schottky barrier diodes                                                                                                                                                                                                                                                              |

| 3 . 学会等名<br>20th International Conference on Silicon Carbide and Related Materials (ICSCRM2023)                                                                                                                                                                                                                                                           |

| 4 . 発表年<br>2023年                                                                                                                                                                                                                                                                                                                                          |

| 1 . 発表者名<br>Mitsuaki Kaneko,Noriyuki Maeda,Tsunenobu Kimoto                                                                                                                                                                                                                                                                                               |

| 2 . 発表標題<br>Minimum Channel Length for Suppressing Short-Channel Effects in SiC JFETs                                                                                                                                                                                                                                                                     |

| 3 . 学会等名<br>20th International Conference on Silicon Carbide and Related Materials (ICSCRM2023)                                                                                                                                                                                                                                                           |

| 4 . 発表年<br>2023年                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                           |

| 1 . 発表者名<br>Mitsuaki Kaneko,Masashi Nakajima,Qimin Jin,Tsunenobu Kimoto                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                           |

| Mitsuaki Kaneko,Masashi Nakajima,Qimin Jin,Tsunenobu Kimoto  2 . 発表標題                                                                                                                                                                                                                                                                                     |

| Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto  2 . 発表標題 SiC Complementary Junction Field-Effect Transistor Logic Gate Operation at 623 K [IEEE EDL]  3 . 学会等名                                                                                                                                                                            |

| Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto  2 . 発表標題 SiC Complementary Junction Field-Effect Transistor Logic Gate Operation at 623 K [IEEE EDL]  3 . 学会等名 The 23rd Kansai Colloquium Electron Devices Workshop (招待講演) (国際学会)  4 . 発表年                                                                                                |

| Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto  2 . 発表標題 SiC Complementary Junction Field-Effect Transistor Logic Gate Operation at 623 K [IEEE EDL]  3 . 学会等名 The 23rd Kansai Colloquium Electron Devices Workshop (招待講演) (国際学会)  4 . 発表年 2023年  1 . 発表者名 Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Noriyuki Maeda, Tsunenobu Kimoto |

| Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto  2. 発表標題 SiC Complementary Junction Field-Effect Transistor Logic Gate Operation at 623 K [IEEE EDL]  3. 学会等名 The 23rd Kansai Colloquium Electron Devices Workshop (招待講演) (国際学会)  4. 発表年 2023年  1. 発表者名 Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Noriyuki Maeda, Tsunenobu Kimoto     |

| Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto  2 . 発表標題 SiC Complementary Junction Field-Effect Transistor Logic Gate Operation at 623 K [IEEE EDL]  3 . 学会等名 The 23rd Kansai Colloquium Electron Devices Workshop (招待講演) (国際学会)  4 . 発表年 2023年  1 . 発表者名 Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Noriyuki Maeda, Tsunenobu Kimoto |

#### 1.発表者名

Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto

# 2 . 発表標題

High-Temperature Operation of SiC JFET-Based Complementary Circuits

#### 3 . 学会等名

2022 Asia-Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices (招待講演) (国際学会)

## 4.発表年

2022年

## 1.発表者名

Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto

## 2 . 発表標題

High temperature operation of SiC complementary JFET logic gates fully fabricated by ion implantation

## 3.学会等名

19th International Conference on Silicon Carbide and Related Materials (ICSCRM2022)(招待講演)(国際学会)

# 4.発表年

2022年

#### 1.発表者名

Taiga Matsuoka, Mitsuaki Kaneko, Tsunenobu Kimoto

### 2 . 発表標題

Anomalously high electron mobility in S-implanted n-type SiC

# 3 . 学会等名

19th International Conference on Silicon Carbide and Related Materials (ICSCRM2022)(国際学会)

## 4.発表年

2022年

## 1.発表者名

Shunya Shibata, Taiga Matsuoka, Mitsuaki Kaneko, Tsunenobu Kimoto

### 2 . 発表標題

Remarkable improvement of threshold voltage controllability in ion-implantation-based SiC JFETs by adopting bottom-gate structure

# 3 . 学会等名

19th International Conference on Silicon Carbide and Related Materials (ICSCRM2022)(国際学会)

# 4.発表年

2022年

| 1.発表者名<br>金子 光顕,中島 誠志,金 祺民,前田 憲幸,木本 恒暢                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------|

| 2 . 発表標題<br>高温動作集積回路を目指したSiC相補型JFETの基礎研究                                                                                          |

| 3 . 学会等名<br>応用物理学会先進パワー半導体分科会 第9回講演会(招待講演)                                                                                        |

| 4 . 発表年<br>2022年                                                                                                                  |

| 1 . 発表者名<br>松岡 大雅, 金子 光顕, 木本 恒暢                                                                                                   |

| 2.発表標題<br>Hall効果測定によるSイオン注入n型SiC層の電気的性質評価                                                                                         |

| 3 . 学会等名<br>応用物理学会先進パワー半導体分科会 第9回講演会 (招待講演)                                                                                       |

| 4 . 発表年<br>2022年                                                                                                                  |

| 1 . 発表者名<br>Katsuya Takahashi, Hajime Tanaka, Mitsuaki Kaneko, Tsunenobu Kimoto                                                   |

| 2.発表標題<br>Impacts of High-Concentration Carrier Traps on Electrical Characteristics of p-i-n Diodes on HPSI SiC Substrates        |

| 3 . 学会等名<br>13th European Conference on Silicon Carbide and Related Materials (ECSCRM2020・2021)(国際学会)                             |

| 4.発表年<br>2021年                                                                                                                    |

| 1 . 発表者名<br>Noriyuki Maeda, Mitsuaki Kaneko, Hajime Tanaka, Tsunenobu Kimoto                                                      |

| 2 . 発表標題<br>SPICE model reproducing the static and dynamic characteristics of a SiC complementary JFET inverter from 300 to 573 K |

| 3 . 学会等名<br>13th European Conference on Silicon Carbide and Related Materials (ECSCRM2020・2021)(国際学会)                             |

| 4 . 発表年                                                                                                                           |

2021年

| 1 . 発表者名<br>Mitsuaki Kaneko, Masashi Nakajima, Tsunenobu Kimoto                                                      |

|----------------------------------------------------------------------------------------------------------------------|

| 2. 発表標題<br>Suppression of a logic-threshold-voltage shift in a SiC complementary JFET logic gate at high temperature |

| 3.学会等名<br>13th European Conference on Silicon Carbide and Related Materials (ECSCRM2020·2021)(国際学会)                  |

| 4 . 発表年<br>2021年                                                                                                     |

# 〔図書〕 計0件

〔出願〕 計2件

| 産業財産権の名称         | 発明者         | 権利者     |  |  |

|------------------|-------------|---------|--|--|

| SiC相補型電界効果トランジスタ | 金子 光顕, 松岡 大 | 同左      |  |  |

|                  | 雅, 木本 恒暢    |         |  |  |

|                  |             |         |  |  |

| 産業財産権の種類、番号      | 出願年         | 国内・外国の別 |  |  |

| 特許、特願2022-065535 | 2022年       | 国内      |  |  |

| 産業財産権の名称<br>SiC接合型電界効果トランジスタ及びSiC相補型接合型電界効果トラ ンジスタ | 発明者<br>金子 光顯, 柴田 峻<br>弥, 木本 恒暢 | 権利者同左   |

|----------------------------------------------------|--------------------------------|---------|

| 産業財産権の種類、番号                                        | 出願年                            | 国内・外国の別 |

| 特許、特願2022-112930                                   | 2022年                          | 国内      |

# 〔取得〕 計0件

〔その他〕

\_

6 . 研究組織

| <br><u> </u> |                           |                       |    |  |

|--------------|---------------------------|-----------------------|----|--|

|              | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |  |

# 7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関    |  |  |  |

|---------|------------|--|--|--|

| スイス     | ETH Zurich |  |  |  |