## 科学研究費助成事業 研究成果報告書

平成 27 年 5月 21 日現在

機関番号: 11301

研究種目:特別推進研究 研究期間:2010~2014年度

課題番号: 22000010

研究課題名(和文) 原子オーダ平坦な界面を有する3次元立体構造トランジスタの

製造プロセスに関する研究

研究課題名(英文) Study on fabrication process of 3-D structured MOS transistor having

atomically flat gate insulator/Si interface

研究代表者

大見 忠弘 (OHMI, Tadahiro)

東北大学・未来科学技術共同研究センター・名誉教授

研究者番号: 20016463

交付決定額(研究期間全体)(直接経費): 478, 900, 000 円

研究成果の概要(和文):本研究では、任意のシリコン表面を原子スケールで平坦化するシリコン表面平坦化技術の開発に成功し、MOS デバイスの信頼性を劇的に向上させた。本技術により、ゲート絶縁膜とシリコンの界面が原子オーダで平坦になされた3次元立体構造 MOS トランジスタ製造への道が拓けた。本研究の成果は、シリコン結晶の有する全性能を駆使した、超低消費電力・超高速動作CMOSシリコンLSIの創出に大きく貢献するものである。

研究成果の概要 (英文): In this study, the atomically flattening technology of any crystalline silicon surface was developed; in the result the electrical reliability was drastically improved. By an introduction of this technology, 3-D structured MOS transistor having atomically flat gate insulator/Si interface can be fabricated.

研究分野:電気電子工学、電子・電気材料工学

キーワード:シリコン、MOSFET、LSI、半導体製造プロセス、半導体製造装置

### 1. 研究開始当初の背景

現状のシリコン集積回路(LSI)は、(100)シリコン表面上にだけ2次元平面形状のトランジスタを用いて製作されている。結果として、現状のシリコン技術はシリコン結晶の有する全性能を駆使することが全くできず、そのごく一部を活用しているにすぎない。そのため、ゲート絶縁膜の薄膜化と寸法微細化だけで進歩を遂げて来た現状のシリコン技術は完全に行き詰まり、LSIの性能向上が完全に停滞してしまっている。

## 2. 研究の目的

現状の困難を克服するには、任意のシリコン表面上に、ゲート絶縁膜とシリコンの界面が原子オーダで平坦になされた3次元立体構造 MOS トランジスタを製造するプロセス技術を創出して、シリコン結晶の有する全性能を駆使することにより、超低消費電力で文字通り超高速動作するバランスド CMOS シリコン LSI を創出することが本研究の目的である。すなわち、停滞している現状のシリコン LSI 技術を、その理論限界に向かって連続的

に超高速化させることである。そのために3次元立体構造 MOS トランジスタの側壁シリコン表面の原子オーダ平坦化が必要なのである。

## 3. 研究の方法

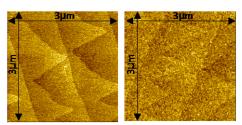

バランスド CMOS を構成するトランジス タは、(1)現状の Inversion Mode MOS トランジ スタから Accumulation Mode MOS トランジス タへ、(2)(100)面基板 2 次元平面形状から (551)SOI 基板 3 次元立体構造へ、(3)ゲート絶 縁膜/Si 界面の原子オーダ平坦化、これらの技 術を導入することにより電子・ホールの散乱 要因が原理的に消滅もしくは激減し、シリコ ンLSIの圧倒的な性能向上が実現される。し かし、これらの技術は、現状のシリコン技術 では全く実現不可能であり、我々が開発した ウルトラクリーンテクノロジーを駆使した ラジカル反応ベースの新しい製造技術によ りはじめて具現化される。図1は原子オーダ で平坦化された Si(100)表面をラジカル酸化 および従来の熱酸化した後の SiO<sub>2</sub>/Si 界面を 原子間力顕微鏡で測定した結果である。ラジ

カル酸化で形成した界面は原子1層のステップと原子オーダで平坦なテラスが維持されているのに対し、従来の熱酸化で形成したSiO<sub>2</sub>/Si界面は凸凹に粗れてしまっている。本研究では、我々が開発したダメージや汚染を一切与えないプラズマ装置を用いたラジカル反応ベースの新製造技術を駆使し、従来では全く実現不可能であった3次元立体構造シリコン表面および側壁面の原子オーダ平坦化を行う。

ラジカル酸化膜/Si界面 従来の熱酸化膜/Si界面 図1 原子間力顕微鏡で測定したSiO<sub>2</sub>/Si界面ラフネス

#### 4. 研究成果

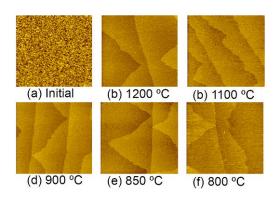

(1) 高純度 Ar 雰囲気熱処理平坦化技術の低温化

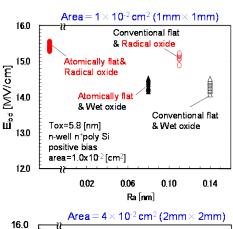

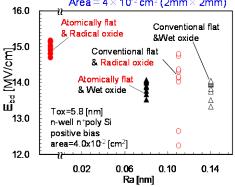

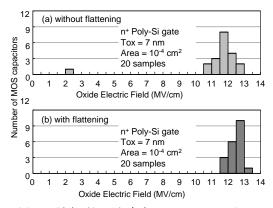

これまでに Si(100)基板について、1100℃以 上の温度でシリコン表面の平坦化を実現し ているが、SOI 基板では 1100℃の熱処理を行 うと SOI 層の剥がれが発生するため、シリコ ン表面の原子オーダ平坦化プロセスの熱処 理温度の低温化が要求される。そこで、平坦 化熱処理プロセスにウルトラクリーン技術 を導入し、熱処理時の Ar 雰囲気中の酸素と 水分を徹底的に低減することにより、シリコ ン表面の原子オーダ平坦化温度を 800℃まで 低温化することに成功し、SOI ウェーハに対 して原子オーダ平坦化が可能となるととも に、従来の高温処理ではきわめて困難であっ た LSI 製造への適応化が容易になった。図 2 は、(100)面シリコンウェハについて、(a)は平 坦化処理前のシリコン表面、(b)~(f)はそれぞ れ 1200℃、1100℃、900℃、850℃、800℃で 平坦化処理した後のシリコン表面を AFM で 測定した結果を示している。平坦化処理を行 ったシリコン表面は、ステップとテラスから 構成される表面を示しており、各ステップ高 さは原子1層に相当する0.135 nm程度であり、 ステップで囲まれたテラス内は原子オーダ で完全に平坦な表面を見事に実現している。 このようにして得られた原子オーダ平坦シ リコン表面上と従来のシリコン表面上に、従 来の熱酸化とラジカル酸化を用いてそれぞ れ酸化膜を形成し、電気的特性を測定し、形 成された酸化膜の信頼性を評価した。図3に 示すように、これまで測定面積が 1 mm × 1 mm と比較的小さい領域では、従来の熱酸化 に比べラジカル酸化で形成した酸化膜は、従

来のシリコン表面上でも絶縁破壊電界強度  $E_{bd}$ が  $15\,MV/cm$  付近に集中しており、非常に高い信頼性を有することを明らかにしているが、測定面積が  $2\,mm \times 2\,mm$  と大きくなるとサンプル間における  $E_{bd}$  のばらつきが大きくなり著しく信頼性が劣化することが明らかとなった。しかし、本研究で実現した原子オーダ平坦 Si 表面とラジカル酸化を組み合わせることにより、測定サンプルの面積を  $2\,mm \times 2\,mm$  と大きくしても高い  $E_{bd}$  を維持したまま電気的特性がばらつかなくなり、さらなる信頼性の向上を実現した。

図 2 (a)平坦化前、(b)~(f)平坦化後の AFM 画像

図 3 原子オーダ平坦シリコン表面上と従来のシリコン表面上に、従来の熱酸化とラジカル酸化を用いて形成した 5.8nm 厚さの酸化膜の絶縁破壊電界強度  $E_{tot}$

## (2) 高純度 Ar 雰囲気熱処理による Si(551) 表面の平坦化

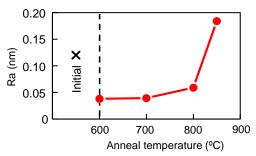

超高純度 Ar 雰囲気中熱処理による平坦化技術を(551)シリコン表面の平坦化に適用した。その結果、(100)シリコン表面では850℃の温度で原子オーダ平坦化が実現されたが、(551)シリコン表面では図4に示すように、850℃の熱処理により表面が極めて凹凸の激しい表面に粗れる結果となった。熱処理温度を600℃まで低温にすることにより、図4に示すように表面ラフネス(Ra)の小さい極めて平坦なシリコン表面が得られた。図51)シリコン表面の平坦化温度と表面ラフネスの関係を示す。これらの結果から、Si(551)表面はSi(100)表面と比較し、より低温でシリコン表面の平坦化が進行し易いことを意味している。

図 4 超高純度 Ar 雰囲気中 850℃および 600℃で熱処理した(551)シリコン表面の AFM 像(3μm×3μm)

図 5 (551) シリコン表面の平坦化温度と表面 ラフネスの関係

# (3) $Xe/H_2$ プラズマ処理による Si 表面の平 坦化

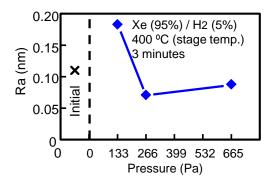

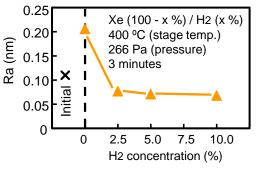

Fin-FET に代表される 3 次元立体構造の MOS トランジスタにおいて、頂面および側壁面を含めた任意の Si 表面の平坦化には、可能な限り低温化が要求される。そのため、熱エネルギーに替わるプラズマを用いたイオン照射エネルギーによりシリコン表面を活性化させ、シリコン表面を平坦化する平坦化技

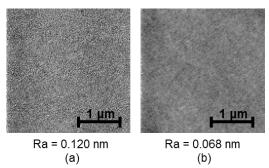

術を開発した。マイクロ波励起高密度プラズマ装置を用いて、 $Xe/H_2$ プラズマによるシリコン表面の平坦化を行った結果、図 6 に示すように、 $H_2$ 濃度が 10%、プロセス圧力が 266 Pa において、Si(100)表面が平均粗さで 0.039 nm まで平坦化された。さらに同条件において、図 7 に示すように、Si(551)表面も平均粗さで 0.068 nm まで平坦化に成功した。

図 6  $Xe/H_2$  プラズマを用いた Si(100)表面平 坦化のプロセス圧力依存性(上図)と  $H_2$  濃度依存性(下図)

図 7 (a) 平坦化前の Si(551)表面の AFM 像、 (b)  $Xe/H_2$ プラズマ平坦化を行った Si(551)表面の AFM 像

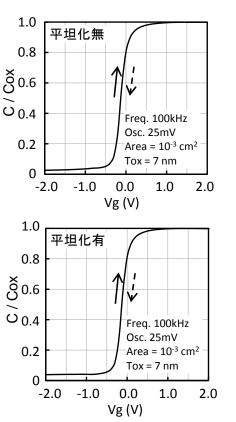

MOS デバイスに対して  $Xe/H_2$  プラズマによるシリコン表面平坦化の効果を検証するために、Si(100) 基板に対して、素子分離形成後、ゲート酸化膜形成直前に  $Xe/H_2$  プラズマ平坦化を行い、そのまま  $Kr/O_2$  プラズマを用いたラジカル酸化によるゲート酸化膜形成を行った。試作した MOS キャパシタにより

電気的特性を評価した。図8に試作したMOS キャパシタの C-V 特性を示す。Xe/H<sub>2</sub>プラズ マ平坦化の有/無に依らず、殆ど C-V カーブ が一致していることから、Xe/H。プラズマに よるプラズマダメージは発生していないこ とが示唆される。一方、図 9 に示すように、 平坦化を行わない従来のシリコン平坦面(約 0.1 nm の平均表面粗さ)を有する MOS キャ パシタに比べて、Xe/H2 プラズマ平坦化を行 った MOS キャパシタでは、絶縁破壊電界強 度が約1MV/cm向上するとともに、それぞれ 20 サンプルに対する絶縁破壊電界強度のば らつきも Xe/H<sub>2</sub>プラズマ平坦化を行うことに より小さくなった。これは、Xe/H2プラズマ 平坦化により、ゲート酸化膜/Si 界面が平坦 化され、絶縁破壊を誘起する電界集中箇所が 抑制されたためと考えられる。この結果から、 Xe/H<sub>2</sub>プラズマ平坦化は、MOS デバイスの電 気的信頼性向上に有効であることが実証さ れた。また、Xe/H<sub>2</sub>プラズマ平坦化はゲート 酸化膜形成直前に行えるため、従来の CMOS 製造プロセスへの導入が比較的容易である と考えられる。すなわち、Xe/H。プラズマ平 坦化技術は、デバイス性能の面だけでなく、 製造プロセスの面でも有効であるといえる。

図 8 従来平坦面を有する MOS キャパシタ (上図)と  $Xe/H_2$ プラズマ平坦化を行った MOS キャパシタ(下図)の C-V 特性

図 9 従来平坦面を有する MOS キャパシタ (上図)と  $Xe/H_2$ プラズマ平坦化を行った MOS キャパシタ(下図)におけるゲート酸化膜の絶縁破壊電界強度のばらつき

# (4) (551)シリコン表面 Accumulation Mode CMOS

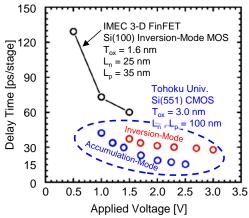

図 10 は、(551)シリコン表面上に Accumulation Mode CMOS を用いて 51 段の Ring Oscillator を試作し、ゲート遅延の動作電 圧依存性を評価した結果を示している。黒丸 は 2004 年に IMEC が発表した(100)シリコン 表面に試作した nMOS のゲート長 25 nm、 pMOS のゲート長 35 nm、ゲート絶縁膜厚 1.6 nm の超微細 3 次元構造 FinFET のゲート遅延 の結果であり、青丸は本研究において(551) シリコン表面上試作した nMOS および pMOS のゲート長 100 nm、ゲート絶縁膜厚 3.0 nm の Accumulation Mode CMOS のゲート遅延の 結果である。ゲート長、ゲート絶縁膜厚とも に IMEC の 3 次元構造 FinFET よりも大きい にもかかわらず、ゲート遅延時間は半分以下 に低減されており、微細化に依らない動作速 度の向上を実証した。

図 10 CMOS リングオシレータ回路を用いたゲート遅延評価

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

[雑誌論文] (計 30 件)

- ① <u>Tetsuya Goto (1 番目)</u>, <u>Tomoyuki Suwa (4 番目)</u>, <u>Tadahiro Ohmi (10 番目)</u>, 全 13 名, "Effect of Composition Ratio on Erbium Silicide Work Function on Different Morphology of Si(100) Surface Changed by Alkaline Etching," *Japanese Journal of Applied Physics*, **54**, pp.04DA04-1 ~ 04DA04-7 (2015), 查読有, DOI: 10.7567/JJAP.54.04DA04

- ② Hiroaki Tanaka, <u>Tomoyuki Suwa</u>, Akinobu Teramoto, Tsukasa Motoya, Shigetoshi Sugawa, and <u>Tadahiro Ohmi</u>, "Effect of Composition Ratio on Erbium Silicide Work Function on Different Morphology of Si(100) Surface Changed by Alkaline Etching," *ECS Transactions*, **61**, pp.47-53 (2014), 查読有,

DOI: 10.1149/06103.0047ecst

③ <u>Tomoyuki Suwa</u>, Akinobu Teramoto, Shigetoshi Sugawa, and <u>Tadahiro Ohmi</u>, "Flattening Technique of (551) Silicon Surface Using Xe/H<sub>2</sub> Plasma," *ECS Transactions*, **61**, pp.401-407 (2014), 查読有.

DOI: 10.1149/06102.0401ecst

- 4 Rihito Kuroda, Yukihisa Nakao, Akinobu Teramoto, Shigetoshi Sugawa, and <u>Tadahiro Ohmi</u>, "Carrier Mobility Characteristics of (100), (110), and (551) Oriented Atomically Flattened Si Surfaces for Fin Structure Design of Multi-gate Metal-Insulator-Silicon Field-Effect Transistors," *Japanese Journal of Applied Physics*, **53**, pp. 04EC04-1~04EC04-7 (2014), 查読有, DOI: 10.7567/JJAP.53.04EC04

- ⑤ Tomoyuki Suwa (1番目), Tadahiro Ohmi (9番目), 全 10名, "Angle-resolved photoelectron spectroscopy study on interfacial transition layer and oxidation-induced residual stress in Si(100) substrate near the interface," *Microelectronic Engineering*, **109**, pp.197-199 (2013), 查読有,

DOI: 10.1016/j.mee.2013.03.004

⑥ Tomoyuki Suwa (1 番目), Tadahiro Ohmi (12 番目), 全 13 名, "Chemical Structure of Interfacial Transition Layer Formed on Si(100) and Its Dependence on Oxidation Temperature, Annealing in Forming Gas, and Difference in Oxidizing Species," Japanese Journal of Applied Physics, 52, pp.031302-1~031302-14 (2013), 查読

有.

DOI: 10.7567/JJAP.52.031302

① H. Tanaka, A. Teramoto, S. Sugawa, and <u>T. Ohmi</u>, "Effect of Erbium Silicide Crystallinity for Low Barrier Contact between Erbium Silicide and n-type Silicon," *ECS Transactions*, **50**, pp. 343-348 (2012), 查読有,

DOI: 10.1149/05004.0343ecst

图 Yukihisa Nakao, <u>Tomoyuki Suwa (5番目)</u>, <u>Tadahiro Ohmi (7番目)</u>, 全7名, "Electrical Properties of Silicon Nitride Using High Density and Low Plasma Damage PECVD Formed at 400°C," *ECS Transactions*, **45**, pp. 421-428 (2012), 查読有.

DOI: 10.1149/1.3700907

- Wiang Li, Rihito Kuroda, <u>Tomoyuki Suwa</u>, Akinobu Teramoto, Shigetoshi Sugawa, <u>Tadahiro Ohmi</u>, "Highly Reliable Radical SiO<sub>2</sub> Films on Atomically Flat Silicon Surface Formed by Low Temperature Pure Ar Annealing," *Journal of Applied Physics*, **50**, pp.10PB05-1~10PB05-7 (2011), 查読有,

DOI: 10.1143/JJAP.50.10PB05

① Tadahiro Ohmi, Hiroaki Tanaka, Tomoyuki Suwa, Xiang Li and Rihito Kuroda, "Science-based New Silicon Technologies Exhibiting Super High Performance due to Radical-reaction-based Semiconductor Manufacturing," Journal of the Korean Physical Society, 59, pp.391-401 (2011), 查読有,

DOI: 10.3938/jkps.59.391

Tadahiro Ohmi, Hidetoshi Wakamatsu, and Akinobu Teramoto, "Pr<sub>3</sub>Si<sub>6</sub>N<sub>11</sub>/Si<sub>3</sub>N<sub>4</sub> Stacked High-k Gate Dielectrics with High Quality Ultrathin Si<sub>3</sub>N<sub>4</sub> Interfacial Layers," ECS Transactions, 35, pp. 275-284 (2011), 查読有,

DOI: 10.1149/1.3568870

[3] Tomoyuki Suwa (1番目), Tadahiro Ohmi (11番目), 全 12名, "Crystallographic orientation dependence of compositional transition and valence band offset at SiO<sub>2</sub>/Si interface formed using oxygen radicals," *Journal of Applied Physics Letters*, 96,

pp.173103-173104 (2010), 査読有, DOI: 10.1063/1.3407515

〔学会発表〕(計33件)

- ① <u>諏訪智之</u>, 応用物理学会優秀論文賞受賞記念講演"Chemical Structure of Interfacial Transition Layer Formed on Si(100) and Its Dependence on Oxidation Temperature, Annealing in Forming Gas, and Difference in Oxidizing Species," 第75回応用物理学会秋季学術講演会, 2014年9月19日, 北海道大学(札幌市)

- ② <u>T. Goto</u>, "Atomically Flattening of Si Surface of SOI and Isolation- patterned Wafers," The 2014 International Conference on Solid State Devices and Materials, 2014 年9月9日, Tsukuba International Congress Center (つくば市)

- ③ <u>T. Suwa</u>, "Flattening Technique of (551) Silicon Surface Using Xe/H<sub>2</sub> Plasma," 225th Meeting of The Electrochemical Society, 2014 年 5 月 14 日, Orlando, USA

- ④ <u>T. Suwa</u>, "Detection of oxidation-induced compressive stress in Si(100) substrate near the SiO<sub>2</sub>/Si interface with atomic-scale resolution," The 2013 International Conference on Solid State Devices and Materials, 2013 年 9 月 26 日, Hilton Fukuoka Sea Hawk (福岡市)

- ⑤ R. Kuroda, "Carrier Mobility on (100), (110), and (551) Oriented Atomically Flattened Si Surfaces for Multi-gate MOSFETs Device Design," The 2013 International Conference on Solid State Devices and Materials, 2013 年 9 月 25 日, Hilton Fukuoka Sea Hawk (福岡市)

- ⑥ <u>T. Suwa</u>, "Angle-Resolved Photoelectron Spectroscopy Study on Interfacial Transition Layer and Oxidation-Induced Residual Stress in Si(100) Substrate Near the Interface," 18th Conference of "Insulating Films on Semiconductors", 2013 年 6 月 26 日, Cracow, Poland

- ① <u>T. Suwa</u>, "Comprehensive Study on Chemical Structures of Compositional Transition Layer at SiO<sub>2</sub>/Si(100) Interface," 222th Meeting of The Electrochemical Society, 2012 年 10 月 9 日, Honolulu, USA

- 图 T. Ohmi, "招待講演: Radical Oxidation and Radical Nitridation for High Integrity Gate Insulator Films on Any Crystal Orientation Silicon Surface for Super High Performance 3D MOS Transistors," 2012 IEEE International Conference on Microelectronic Test Structures, 2012年3月18日, Shanghai, China

- 9 R. Kuroda, "On the Si Surface Flattening

- Effect and Gate Insulator Breakdown Characteristic of Radical Reaction Based Insulator Formation Technology," 2011 International Conference on SOLID STATE DEVICES AND MATERIALS, 2011年9月29日, Aichi Industry & Labor Center (名古屋市)

- ⑩ <u>T. Ohmi</u>, "招待講演: Science Based New Silicon Technologies Exhibiting Super High Speed Performance Over 100GHz Clock Rate," 30th Electronic Materials Symposium, 2011 年 6 月 29 日, (ラフォーレ琵琶湖(滋賀県守山市)

- ① H. Tanaka, "Low Work Function between Erbium Silicide and n-type Silicon Controlled by Cap Film Stress," 221th Meeting of The Electrochemical Society, 2011年5月8日, Seattle, USA

- ② <u>T. Ohmi</u>, "招待講演: Science Based New Silicon Technologies Exhibiting Super High Performance due to Radical Reaction Based Semiconductor Manufacturing", The 18th Korean Conference on Semiconductors, 2011 年 2 月 17 日, Jeju, Korea

[その他]

ホームページ等

http://www.fff.niche.tohoku.ac.jp/

#### 6. 研究組織

(1) 研究代表者

大見 忠弘 (OHMI, Tadahiro)

東北大学・未来科学技術共同研究センター・名誉教授

研究者番号: 20016463

(2) 研究分担者

平山 昌樹 (HIRAYAMA, Masaki)

東北大学・未来科学技術共同研究センタ

一・准教授

研究者番号:70250701

後藤 哲也 (GOTO, Tetsuya)

東北大学・未来科学技術共同研究センタ

ー・准教授

研究者番号:00359556

諏訪 智之(SUWA, Tomoyuki)

東北大学・未来科学技術共同研究センタ

ー・助教

研究者番号:70431541