# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成24年5月8日現在

機関番号:11301

研究種目:研究活動スタート支援

研究期間:2010~2011 課題番号:22860004

研究課題名(和文) MOSトランジスタの低ノイズ化へ向けたデバイス構造最適化

研究課題名(英文) Device Structure Optimization of MOS Transistors for Reduction of

Low Frequency Noise

研究代表者

黒田 理人 (KURODA RIHITO)

東北大学・大学院工学研究科・助教

研究者番号: 40581294

研究成果の概要(和文):100万個を超えるMOSトランジスタのノイズを統計的に評価可能な計測手法を用いて、構造パラメータを振ったトランジスタのノイズを評価した。その結果、埋め込み層厚さが60nmの埋め込みチャネル構造では、通常の表面チャネル構造と比べRandom Telegraph Noiseの発生頻度が約1/60に低減することを見出した。また本構造の導入によるノイズ低減メカニズムを明らかにし、高感度CMOSイメージセンサへの適用に向けた低ノイズMOSトランジスタ構造の最適化指針を創出した。

研究成果の概要(英文): The noise characteristics of MOS transistors with various device parameters were evaluated using the measurement method that can statistically analyze noise of more than one million transistors. It was confirmed that the appearance probability of random telegraph noise in buried channel structure with buried layer width of 60 nm is reduced to 1/60 compared to the standard surface channel structure. The noise reduction mechanism by an introduction of the buried channel structure was clarified. The device structure optimization methodology for low noise MOS transistor was proposed for the realization of very high sensitivity CMOS image sensors.

### 交付決定額

(金額単位:円)

|         | 直接経費        | 間接経費     | 合 計         |

|---------|-------------|----------|-------------|

| 2010年度  | 1, 260, 000 | 378, 000 | 1, 638, 000 |

| 2011 年度 | 1, 160, 000 | 348, 000 | 1, 508, 000 |

| 年度      |             |          |             |

| 年度      |             |          |             |

| 年度      |             |          |             |

| 総計      | 2, 420, 000 | 726, 000 | 3, 146, 000 |

研究分野:工学

科研費の分科・細目:電子デバイス・電子機器

キーワード: MOS トランジスタ、1/f ノイズ、Random Telegraph Noise、CMOS イメージセンサ

#### 1. 研究開始当初の背景

近年、拡大が目覚しいイメージセンサ市場の中でも、車載用やセキュリティのための監視用といった、暗い場所を鮮明に撮像する性能、つまり高感度性能が求められる用途において、イメージセンサの性能向上が求められ

ている。低照度撮像においては、Signal to Noise 比(S/N 比)が低くなるため、鮮明な撮像を可能にするには、イメージセンサの低ノイズ化が必須である。ここで、撮像素子における究極の感度とは、撮像素子に入った光子1個を1デジタルナンバーとして出力できる

ことである。低消費電力性能などで他の撮像 素子を凌駕する Complementary Metal-Oxide-Semiconductor(CMOS)イメージセンサ におけるノイズ成分としては、暗電流ショッ トノイズ、電荷転送ノイズ、Floating Diffusion(FD) リセットノイズ、読み出し回 路系ランダムノイズ、及びソースフォロワア ンプを構成するトランジスタから発生する 1/f ノイズ、Random Telegraph Noise (RTN) などの低周波ノイズが挙げられる。この中で、 ソースフォロワアンプのノイズ以外は、相関 二重サンプリング技術や読み出し回路の低 ノイズ化などの回路技術を用いることで、ノ イズの影響を大きく低減することが可能で ある。しかし、ソースフォロワアンプを構成 するトランジスタから出現する 1/f ノイズや RTN は、回路技術を用いても取り除くことが 出来ない。よって、これらのノイズを低減す るには、トランジスタの低ノイズ化が必須で ある。

### 2. 研究の目的

常温において光子1個の検出が可能であ る究極の感度を有するイメージセンサの創 出のために、RTN の発生・低減メカニズムを 明らかにして、極低ノイズデバイス構造とそ の製造方法を見出すことを目的とする。CMOS イメージセンサの画素内ソースフォロワア ンプに相当するトランジスタについて、キャ リアが走行するチャネルのゲート絶縁膜/シ リコン界面からの距離、キャリア密度の均一 性等のデバイスパラメータを広範囲かつ詳 細に変更した複数のデバイスを作製する。大 規模トランジスタの統計的評価ツールを用 いてRTNのノイズ強度、発生確率などの統計 的ノイズ特性を測定し、デバイスパラメータ との相関を明らかにする。これにより、RTS ノイズ発生・低減のメカニズムを詳細に解明 するとともに RTN の低減が可能なデバイス構 造とその製造方法を見出す。

# 3. 研究の方法

- (1) 初年度は、ノイズの低減に効果があると 考えられるデバイスパラメータを振ったト ランジスタを作成し、ノイズレベルの評価を 行った。具体的には、

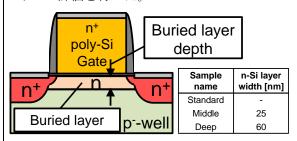

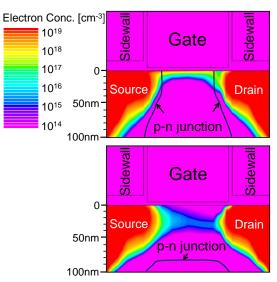

- ① MOS トランジスタの電荷の通り道であるチャネルからトラップサイトが存在するゲート絶縁膜/シリコン界面付近の距離とノイズレベルとの相間を明らかにするため、図1に模式図を示す、埋め込み n 層厚さを振ったn チャネルの埋め込みチャネル構造 MOS トランジスタを作成した。

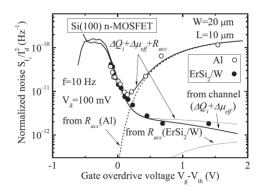

- ②ソース・ドレイン電極の直列抵抗が 1/f ノイズに与える影響を評価するため、コンタクト抵抗率が  $8x10^{-10}$  cm² と極低抵抗な  $ErSi_2$  シリサイドコンタクトを有する n チャネル MOS

- トランジスタを作成した。

- ③作成したトランジスタについて、低周波ノイズの評価を行った。ここで、RTN の評価には、既に開発済みである CMOS イメージセンサの画素内ソースフォロワアンプを模擬した大規模トランジスタアレイを用いた統計的ノイズ評価ツールを適用した。

- (2) 次年度は、初年度にノイズ低減効果が大きいことを示した埋め込みチャネル構造 MOSトランジスタ構造のノイズ低減のメカニズムを明らかにするために、

- ①100 万個を超えるトランジスタの統計的な ノイズ特性計測を用いて計測された RTN の発 生頻度、振幅、時定数の詳細な評価を従来 MOS トランジスタ構造と比較して行った。

- ②デバイスシミュレーションを用いて作製したデバイス構造でキャリアが流れるチャネルの深さ、幅を計算し、埋め込みチャネル構造の導入によるRTNの低減メカニズムを示した。また、

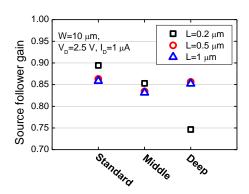

- ③CMOS イメージセンサのソースフォロワアンプへの適用可能性を検証するために、しきい値ばらつきやソースフォロワ動作時のゲインの評価を行った。

図 1. 作製した埋め込みチャネル構造 MOS トランジスタの構造図。埋め込み n 層厚さは 60nm まで条件振りを行った。

# 4. 研究成果

(1) 埋め込みチャネル構造の導入による RTN 低減の効果とメカニズム

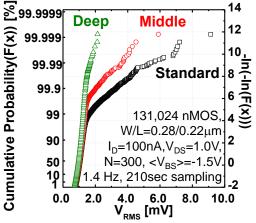

図2は、測定した各水準131,072個のトラ ンジスタのノイズ強度の累積確率分布を示 す。グラフの横軸は一定ドレイン電流印加時 に時間軸方向に複数回測定した各トランジ スタのゲート-ソース間電圧の二乗平均平方 根(V<sub>RMS</sub>)でありノイズ強度を示す。測定は 0.7 s のサンプリングレートで 300 回測定し た。被測定トランジスタのゲート寸法は、幅、 長さがそれぞれ 0.24、 $0.22~\mu\,\mathrm{m}$  である。累 積確率が 99%程度までの領域 (V<sub>RMS</sub> < 1.5 mV) は測定系のノイズを含むノイズの主分布で ある。主分布から傾きが変化した以降の分布 には RTN が観測された。ここで、通常の表面 チャネル構造と比べ、埋め込みチャネル構造 では、同じ出現確率における RTN の強度が小 さいことが示された。また、埋め込みn層が

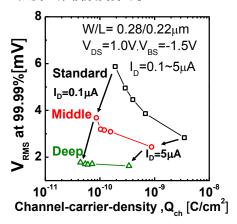

厚くなる程、ノイズ強度の減少はより顕著で あることが明らかになった。RTS ノイズの振 幅が 1mV を超えるトランジスタの発生頻度は、 表面チャネル構造において 0.73%(測定サン プル母数:131,072個)だったのに対し、埋め 込みチャネル構造で埋め込み n 層幅が 25 nm のものは 0.28%(同:131,072 個)、埋め込み n 層幅が 60nm のものは 0.013%(同:1,048,576 個)であり、表面チャネル構造と比較して約 1/60に低減された。また、図3は、累積確率 が99.99%におけるV<sub>RMS</sub>の測定値をチャネル中 のキャリア密度に対してプロットした結果 である。ここで、チャネル中のキャリア密度 が低い程、チャネルがあたかも水の少ない川 の流れのように細分化し偏って形成され、 RTN を引き起こすトラップの影響が相対的に 増大してノイズ強度が大きくなることが分 かっていた。一方、埋め込みチャネル構造の デバイスでは、同じ電流を駆動する際のキャ リア密度が表面チャネル構造と比べて低い にも関わらず、埋め込み層が厚くなるほどノ イズ強度が小さく、埋め込み層厚さは RTN 強 度に与える影響が大きいデバイスパラメー タであることが明らかになった。

図 2. 埋め込みチャネル構造 MOS トランジスタと表面チャネル構造 MOS トランジスタのノイズ強度の累積頻度分布。

図 3. チャネル中のキャリア密度に対する累積確率が99.99%のトランジスタのV<sub>RMS</sub>の関係。

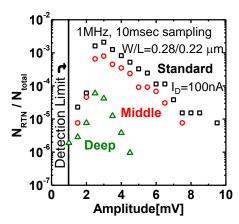

また、RTN の強度を示す振幅と、電荷とトラップの相互作用の頻度を示す時定数を抽出した結果、図 4 が示す通り、従来構造と比べ、埋め込み n 層幅が 60nm である構造では、振幅が大きい程、発生頻度の減少傾向がより大きいことが示された。また、 $1\sim20\,\mu$  sec の比較的短い時定数の発生割合が従来構造と比べて減少することが明らかになった。

図5は、100nAのドレイン電流を印加時のMOSトランジスタのキャリア密度のデバイスシミュレーション結果を示す。通常の表面チャネル構造と比較し、埋め込みチャネル構造では電荷の通り道であるチャネルとトラップが存在する絶縁膜/Si界面との距離が大きい。さらに、チャネルが深さ方向により幅広く形成されていることが分かる。また、結果から、RTNの統計的評価をしたバイアス領域では、チャネルには、電子を遠ざける方向に電界が印加されることが分かった。

図 4. 抽出した RTN を示す全トランジスタに対する RTN の振幅の相対度数分布。

図 5. MOS トランジスタ断面図におけるキャリア密度の等高線図。(a)は表面チャネル構造、(b)は埋め込み層が 60 nm の埋め込みチャネル構造を示す。

これらの結果から、埋め込みチャネル型 MOS トランジスタでは、チャネルの位置が界面から遠いと共に、チャネルが深さ方向により広がって形成されることで、チャネルの細分化が抑制され、その結果、RTS ノイズの振幅が減少することが分かった。さらに、チャネルの位置が界面から遠ざける側に働くため、キャリアを界面から遠ざける側に働くため、絶縁膜中のトラップとの相互作用が弱まり、短い時定数の RTN の発生頻度が減少することが分かった。以上、埋め込みチャネル構造 MOS トランジスタの導入による RTN 低減のメカニズムを示した。

(2) CMOS イメージセンサ用ソースフォロワアンプへの適用に向けた埋め込みチャネル構造 MOS トランジスタの特性評価

一方、チャネル界面距離を離した際の短チャネル効果の増大が懸念していたが、パンチスルーストップ層としてウェル濃度の約2倍程度の p 層を埋め込み層下に形成した場合、チャネル長が  $0.5\mu$  m 程度であれば、CMOS イメージセンサのソースフォロワアンプに求められるしきい値ばらつき、増幅率(図 6)、及び増幅率の線形性の確保できる動作範囲等の性能を満たすことが実データによって示された。

図 6. ソースフォロワアンプのゲイン特性の デバイス構造依存性。評価したゲート長はそ れぞれ 0.2, 0.5,  $1.0~\mu$  m である。

# (3) ソース・ドレイン電極の直列抵抗低減による 1/f ノイズ低減

図7に測定結果を示す通り、ソース・ドレイン電極の直列抵抗がドレイン電流値の比較的大きいバイアス条件下で1/fノイズ強度に影響を及ぼすことを発見し、ErSi<sub>2</sub>シリサイドを用いた極低抵抗コンタクト電極をnチャネル MOSトランジスタに導入することでシリサイドコンタクトが無い場合と比べて、1/fノイズ強度を大幅に低減出来ることをテナレスが強度を大幅に低減出来ることをテナレた。これは、比較的電流を大きく流すアナログ回路や高周波回路用トランジスタの低ノイズ化にとって重要な知見である。

図 7. 低抵抗  $ErSi_2$  コンタクト、及び A1 電極 コンタクトを有する n チャネル MOS トランジ スタの 1/f ノイズ強度のゲートオーバードライブ電圧依存性。

### (4) まとめ

本研究では埋め込みチャネル構造 MOS トランジスタの導入による RTN の低減の効果とそのメカニズムを明らかにした。本構造は、通常の表面チャネル型構造 MOS トランジスタの製造工程中のチャネルイオン注入工程を変更するだけで製造可能である。また、パンチスルーストップ層の作りこみによって CMOSイメージセンサのソースフォロワアンプに求められる緒特性を満たす。以上、本構造は、常温において光子1個の検出が可能である究極の感度を有する CMOS イメージセンサの創出に貢献できるものとして期待される。

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

〔雑誌論文〕(計13件)

- ① K. Abe, T. Fujisawa, H. Suzuki, S. Watabe, <u>R. Kuroda</u>, S. Sugawa, A. Teramoto and T. Ohmi, "A Test Circuit for Statistical Evaluation of p-n Junction Leakage Current and Its Noise," IEEE Trans. Semicond. Manuf., 印刷中, 2012, 查読有.

- ② T. Inatsuka, Y. Kumagai, R. Kuroda, A. Teramoto, S. Sugawa and T. Ohmi, "Recovery Characteristics of Anomalous Stress-Induced Leakage Current of 5.6 nm Oxide Films," Jpn. J. Appl. Phys., 51, pp. 04DC02-1-6, 2012, 査読有.

- ③ R. Kuroda, A. Teramoto, X. Li, T. Suwa, S. Sugawa, and T. Ohmi, "On the Interface Flattening Effect and Gate Insulator Breakdown Characteristic of Radical Reaction Based Insulator Formation Technology," Jpn. J. Appl. Phys., 51, pp. 02BA01-1-6, 2012, 査読

有.

- ④ H. Tanaka, A. Teramoto, <u>R. Kuroda</u>, Y. Nakao, T. Suwa, K. Kawase, S. Sugawa and T. Ohmi, "Different Properties of Erbium Silicides on Si(100) and Si(551) Orientation Surfaces," ECS Trans., 41, pp. 365-373, 2011, 查読有.

- ⑤ A. Teramoto, X. Li, <u>R. Kuroda</u>, T. Suwa, S. Sugawa and T. Ohmi, "Gate SiO<sub>2</sub> Film Integrity on Ultra-Pure Argon Anneal (100) Silicon Surface," ECS Trans., 41, pp. 147-156, 2011, 查読有.

- ⑥ Y. Kumagai, K. Abe, T. Fujisawa, S. Watabe, R. Kuroda, N. Miyamoto, T. Suwa, A. Teramoto, S. Sugawa and T. Ohmi, "Large-Scale Test Circuits for High-Speed and Highly Accurate Evaluation of Variability and Noise in Metal-Oxide-Semiconductor Field-Effect Transistor Electrical Characteristics," Jpn. J. Appl. Phys., 50, pp. 106701-1-11, 2011, 查読有.

- ⑦ Y. Kumagai, A. Teramoto, T. Inatsuka, R. Kuroda, T. Suwa, S. Sugawa and T. Ohmi, "Evaluation for Anomalous Stress-Induced Leakage Current of Gate SiO<sub>2</sub> Films Using Array Test Pattern," IEEE Trans. Electron Dev., 58, pp. 3307-3313, 2011, 查読有.

- 8 X. Li, R. Kuroda, T. Suwa, A. Teramoto,

S. Sugawa and T. Ohmi, "Highly

Reliable Radical SiO<sub>2</sub> Films on

Atomically Flat Silicon Surface Formed

by Low Temperature Pure Ar

Annealing," Jpn. J. Appl. Phys., 50,

pp. 10PB05-1-7, 2011, 查読有.

- ⑨ X. Li, A. Teramoto, T. Suwa, R. Kuroda, S. Sugawa, and T. Ohmi, "Formation speed of atomically flat surface on Si (100) in ultra-pure argon," Microelec. Eng. 88, pp. 3133-3139, 2011, 査読有.

- ⑩ P. Gaubert, A. Teramoto, <u>R. Kuroda</u>, Y. Nakao, H. Tanaka, S. Sugawa, and T. Ohmi, "Analysis of the Low-Frequency Noise Reduction in Si(100) Metal-Oxide-Semiconductor Field-Effect Transistors," J. Appl. Phys., 50, pp.04DC01-1-6, 2011. 查読有.

- ① R. Kuroda, A. Teramoto, S. Sugawa, and T. Ohmi, "Impact of Channel Direction Dependent Low Field Hole Mobility on (100) Orientation Silicon Surface," Jpn. J. Appl. Phys., 50, pp. 04DC03-1-6, 2011, 查読有.

- Y. Yukihisa, <u>R. Kuroda</u>, H. Tanaka,

T. Isogai, A. Teramoto, S. Sugawa, and

- T. Ohmi, "Impact of Work Function Optimized S/D Silicide Contact for High Current Drivability CMOS," ECS Trans., 28, pp. 315-324, 2010, 查読有.

- ③ X. Li, T. Suwa, A. Teramoto, <u>R. Kuroda</u>, S. Sugawa, and T. Ohmi, "Atomically Flattening Technology at 850° C for Si(100) Surface," ECS Trans., 28, pp. 299-309, 2010, 查読有.

# 〔学会発表〕(計16件)

- ① A. Yonezawa, A. Teramoto, <u>R. Kuroda</u>, H. Suzuki, S. Sugawa and T. Ohmi, "Statistical Analysis of Random Telegraph Noise Reduction Effect by Separating Channel From the Interface," IEEE Intl. Reliability Rhys. Symp., 2012年4月18日, Anaheim, U.S.A.

- ② Y. Kumagai, T. Inatsuka, R. Kuroda, A. Teramoto, T. Suwa, S. Sugawa and T. Ohmi, "A Test Circuit for Extremely Low Gate Leakage Current Measurement of 10 aA for 80,000 MOSFETs in 80 s," IEEE Intl. Conf. on Microelectronic Test Structures, 2012年3月21日, San Diego, U.S.A.

- ③ <u>黒田理人</u>, 寺本章伸, 李翔, 諏訪智之, 須川成利, 大見忠弘, "ラジカル反応ベース絶縁膜形成プロセスにおける界面平 坦化効果と絶縁膜破壊特性との関係," 電子情報通信学会 シリコン材料・デバイス研究会, 2011年10月20日, 仙台.

- ④ 稲塚卓也,熊谷勇喜,<u>黒田理人</u>,寺本章伸,須川成利,大見忠弘,"異常 Stress Induced Leakage Current の発生・回復特性の統計的評価,"電子情報通信学会シリコン材料・デバイス研究会,2011年10月20日,仙台.

- ⑤ 鈴木裕彌, <u>黒田理人</u>, 寺本章伸, 米澤秋 彰浩, 松岡弘章, 中澤泰希, 阿部健一, 須川成利, 大見忠弘, "埋め込み構造に よる MOSFET におけるランダム・テレグラ フ・ノイズの低減," 電子情報通信学会 シリコン材料・デバイス研究会," 2011 年10月20日, 仙台.

- ⑥ H. Tanaka, A. Teramoto, <u>R. Kuroda</u>, Y. Nakao, T. Suwa, S. Sugawa, and T. Ohmi, "Different properties of erbium silicides on Si(100) and Si(551) orientation surfaces," 220th Meeting of The Electrochemical Society, 2011年10月13日, Boston, U.S.A.

- 7 A. Teramoto, X. Li, <u>R. Kuroda</u>, T. Suwa, S. Sugawa, and T. Ohmi "Gate SiO<sub>2</sub> Film Integrity on Ultra-Pure Argon Anneal (100) Silicon Surface," 220th Meeting

- of The Electrochemical Society, 2011 年10月10日, Boston, U.S.A.

- 图 H. Suzuki, <u>R. Kuroda</u>, A. Teramoto, A. Yonezawa, S. Sugawa and T. Ohmi "Impact of Random Telegraph Noise Reduction with Buried Channel MOSFET," 2011 Intl. Conf. on SOLID STATE DEVICES AND MATERIALS, 2011年9 月 29日,名古屋.

- ① T. Inatsuka, Y. Kumagai, R. Kuroda, A. Teramoto, S. Sugawa, and T. Ohmi, "Recovery Characteristic of Anomalous Stress Induced Leakage Current of 5.6nm Oxide Films," 2011 Intl. Conf. on SOLID STATE DEVICES AND MATERIALS, 2011年9月28日,名古屋.

- ① 招待講演: 黒田理人, 田中宏明, 中尾幸久, 寺本章伸, 宮本直人, 須川成利, 大見忠弘, "デュアルシリサイドを用いた低直列抵抗 CMOS ソース/ドレイン電極形成技術," 電気学会 電子デバイス研究会, 2011年3月1日, 水上町.

- ② X. Li, R. Kuroda, T. Suwa, A. Teramoto, S. Sugawa, and T. Ohmi, "High reliable SiO<sub>2</sub> Films on Atomically Flat Silicon Surface Formed by Low Temperature Pure Ar Annealing," Intl. Workshop on Dielectric Thin Films For Future Electron Devices: Science and Technology, 2011年1月20日,東京.

- (13) R. Kuroda, H. Tanaka, Y. Nakao, A. Teramoto, N. Miyamoto, S. Sugawa and T. Ohmi, "Ultra-low Series Resistance W/ErSi<sub>2</sub>/n<sup>+</sup>-Si and W/Pd<sub>2</sub>Si/p<sup>+</sup>-Si S/D Electrodes for Advanced CMOS Platform," 2010 IEEE IEEE Intl. Electron Devices Meeting, 2010 年 12 月 8 日, San Francisco, U.S.A.

- ④ Y. Kumagai, K. Abe, T. Fujisawa, S. Watabe, R. Kuroda, N. Miyamoto, T. Suwa, A. Teramoto, S. Sugawa and T. Ohmi "Large Scale Test Circuits for Systematic Evaluation of Variability and Noise of MOSFETs' Electrical Characteristics," 2010 Intl. Conf. on SOLID STATE DEVICES AND MATERIALS, 2010 年 9 月 23 日,東京.

- ① R. Kuroda, A. Teamoto, S. Sugawa and

- T. Ohmi, "Impact of Channel Direction Dependent Low Field Hole Mobility on Si(100)," 2010 Intl. Conf. on SOLID STATE DEVICES AND MATERIALS, 2010年9 月 23日,東京.

- (16) P. Gaubert, A. Teramoto, <u>R. Kuroda</u>, Y. Nakao, H. Tanaka and T. Ohmi "Drastic reduction of the low frequency noise in Si(100) p-MOSFETs," 2010 Intl. Conf. on SOLID STATE DEVICES AND MATERIALS, 2010 年 9 月 23 日,東京.

### 6. 研究組織

(1)研究代表者

黒田 理人 (KURODA RIHITO) 東北大学・大学院工学研究科・助教 研究者番号: 40581294

- (2)研究分担者 なし

- (3)連携研究者なし