# [Grant-in-Aid for Scientific Research (S)]

### Integration of 2 dimensional tunnel FET for ultra-low power consumption system

| Principal<br>Investigator | , , , ,                                                      | e School of Engineering, Professor  Researcher Number:20373441            |

|---------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------|

| Project<br>Information    | Project Number : 22H04957<br>Keywords : 2 dimensional semico | Project Period (FY) : 2022-2026 anductors, Heterointerface, Tunnel effect |

## Purpose and Background of the Research

#### Outline of the Research

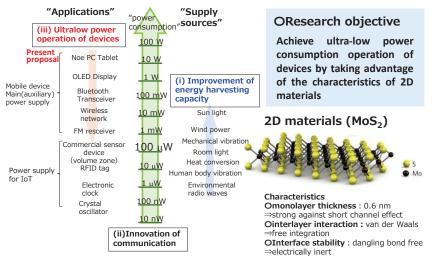

Due to the influence of the new coronavirus infection, not only the digital transformation of the social infrastructure but also the lifestyle of individuals is changing. Although the number of IoT devices is expected to increase explosively, low power consumption is an essential bottleneck (Fig. 1). In this study, we demonstrate ultra-low power consumption operation by using two-dimensional materials based on "integrable" realistic device structures. In this way, we would like to contribute to the realization of ultra-low power consumption devices, which have not been achieved despite their importance.

Figure 1. (Left) Three types of methods that contribute to power consumption are shown. (Right) Atomic model and features of 2D material.

### Proposal based on 2D materials

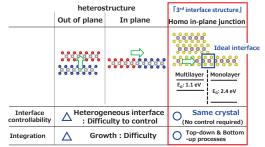

In this study, we propose for the first time a two-dimensional-tunnel field effect transistor (FET) based on an "integrable" realistic device structure. The points are (1) a simple device structure that does not use a complicated two-dimensional heterostructure, and (2) the use of Si integration process. As a result of the studies so far, as shown in Fig. 2, we found the validity of the device structure using the same in-plane junction instead of the two-dimensional heterostructures. In this study, we integrate two-dimensional-tunnel FETs using the same in-plane junction and demonstrate ultra-low power consumption operation.

#### Proposal of "integrable" device structure

#### 2D-Tunnel FET inverter

Basic parts are manufactured by Si process.

TFET with a novel third interface structure!

Figure 2. (Left) Three types of interface structures. (Right) Inverter based on 2D-tunnel FET.

### Expected Research Achievements

#### Members

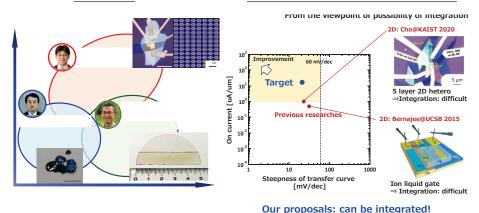

As shown in Fig. 3, we collaborate with Ueno G @ Saitama University and Miyata G @ Tokyo Metropolitan University, who are leading the substitutional doping research in bulk crystal growth and large area growth.

#### Achievements

The ultra-low power consumption devices require steepness of the transfer curve and high on-current in electronic devices. The following items were set to achieve the target values shown in Fig. 3. (i) Fabrication of the same crystal in-plane junction by atomic layer etching, (ii) Large area/position-controlled growth of highly doped 2D crystal, (iii) Formation of new high concentration n<sup>+</sup> doped 2D crystal source, (iv) Ohmic electrode formation, (v) Fabrication and evaluation of tunnel FETs. We achieve the target value and contribute to ultra-low power consumption devices.

Figure 2. (Left) Members. (Right) Target & world research trends.

Homepage Address, etc. http://webpark1753.sakura.ne.jp/nagashio\_lab\_E/