#### 研究成果報告書 科学研究費助成事業

今和 6 年 6 月 8 日現在

機関番号: 12608 研究種目: 若手研究 研究期間: 2022 ~ 2023

課題番号: 22K17879

研究課題名(和文)超小型バッテリーレスセンシングプラットフォームための機械学習チップ

研究課題名(英文)Machine Learning Chip for Ultra Small Battery-less Sensing Platform

#### 研究代表者

横式 康史(Yokoshiki, Yasufumi)

東京工業大学・科学技術創成研究院・助教

研究者番号:70893189

交付決定額(研究期間全体):(直接経費) 3.500.000円

研究成果の概要(和文):本研究では入力数の少ないセンサに特化した機械学習モデルを作るための環境整備を行った。及び目標とするエナジーハーベスティング向けの機械学習回路の重みを保存するための不揮発性メモリの検討も行った。Binarized Neural Network (BNN)を用いた回路をFPGA上だけではなく、実際に、 $0.18\,\mu\,m$  1-poly 6-metal 標準CMOSプロセスを用いて試作し、その低消費電力性に関して有用性を示すことができた。更に、ニューロン数を変更できる独自の回路により、ハードウェアで実装した機械学習回路に柔軟な特性を持たせることができるようになった。

研究成果の学術的意義や社会的意義 AIや機械学習などの分野は、回路の研究分野にも有用である。画像処理やアクセラレータなどの分野の取り組みが多かったが、本研究はこれまで研究例が少なかった。特にあまり取り組まれていなかった入力数の少ない機械学習モデルからなる分野に着目し、より小型で低消費電力性に優れているBNNの回路をチップ化した。その計測 結果からBNNからなる回路の低消費電力性を示すことができた。その他にも新しいモデルも提案することができ、回路分野におけるBNNによる機械学習モデルの有用性を示すことができた。

研究成果の概要(英文): In this study, I prepared an environment to create a machine-learning model specialized for sensors with a small number of inputs. I also examined non-volatile memory for storing weights in machine-learning circuits targeted energy harvesting. I developed a Binarized Neural Network (BNN) circuit not only on an FPGA but also on a 0.18-µm 1-poly 6-metal standard CMOS process and demonstrated its usefulness in terms of low power consumption. Furthermore, a unique circuit that allows the number of neurons to be changed has made it possible to provide flexible characteristics to machine learning circuits implemented in hardware.

研究分野: デジタル回路、アナログ回路

キーワード: 機械学習 Machine Learning Binarized Neural Network Digital Circuit 二値化回路 デジタル回路 信号処理 信号処理

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

# 1.研究開始当初の背景

近年、Society 5.0, SDGs と言った長期的な目標実現において、環境問題に注目が集まっている。その環境問題への対策としてエナジーハーベスティング技術が挙げられる。筆者らは太陽電池を間欠駆動させることで、環境エネルギーのみで駆動する小型化が可能なエッジデバイスの研究に取り組んでいる(図1)。このデバイスにおいて課題となるのは、個々のモジュールを制御するための回路をどのように設計するか、という点にある。筆者は現在、太陽電池から得られる微小な電力のみで駆動する間欠駆動が可能な CPU の研究を行っている。この CPU では各モジュールの制御は可能だが、間欠駆動のための処理のオーバーヘッドや、低い駆動周波数を見込んでいるため負荷の高い計算やセンサ情報を使った高度な処理は難しい。近年、機械学習モデルはその高速性、効率性の高さから CPU を補佐する目的で用いられている。入力に対して任意の関数を出力させることができるので、汎用的な信号処理モデルとして用いることができる。

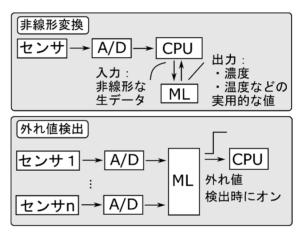

しかし、入力数の少ないセンサに特化した機械学習チップの研究例は少なく、機械学習モデルを用いるための基礎的な研究が不足しているという課題がある。図2のようなセンサの情報処理にはどのような機械学習アルゴリズムが適しているのか、どのようなパラメータにすべきか、どのような実装方法を検討すべきか、などが未だ明らかになっておらず、エナジーハーベスティング向けエッジデバイスに機械学習を用いるための障壁となっている。

図 1 複数のチップを組み合わせたデバ イスのイメージ図

図 2 機械学習チップの主な用途

## 2.研究の目的

本研究では、エナジーハーベスティング向けの機械学習チップとして、低消費電力性に優れた機械学習チップを製作する。更に、本研究の成果として製作する機械学習チップを別研究の CPU と組み合わせることで、超小型のバッテリーレスセンシングプラットフォームの創出を目指す。

#### 3.研究の方法

本研究では、実装の容易さと学習のしやすさを考慮し、デジタル回路で実装できる機械学習について取り扱う。信号処理用のモデルとしては、デジタル回路での実装が比較的容易であるDeep Neural Network (DNN) を 2 値化した Binarized Neural Network (BNN)を用いる。Verilogと FPGA を用いて回路を実装し、動作検証の後、0.18 μ m 1-poly 6-metal 標準 CMOS プロセスでチップ化する。

## 4. 研究成果

本研究でははじめに BNN に適した学習環境を検討した。ツールとしては Tensorflow 及び pytorch を比較し、その結果として Tensorflow 及び BNN 向けのライブラリである Larq を用いるのが最適であることが分かった。これにより、BNN モデルをパソコン上で直接高速に学習させることができ、重みはそのまま FPGA やチップに移行することができるようになった。

更に本研究では、図1のように間欠駆動で機械学習回路を用いるために、BNN モデルの重みを保存するための不揮発性メモリの検討を行った。不揮発性メモリはチップ製造プロセスによってはCMOSチップ上に集積することができるが、現在用いているプロセスでは利用できないた

め、何らかの方法が必要となる。一度書き込んで消去できないタイプのメモリである OTP メモリが使用可能であるほか、小型の不揮発性メモリ IC を外部メモリとして用いることも可能であることが分かった。

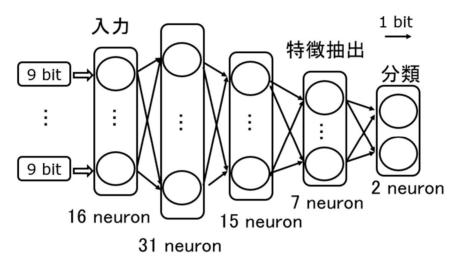

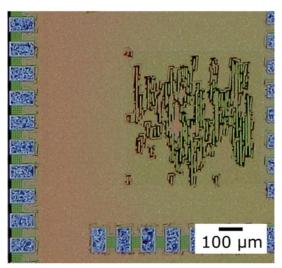

その次に、FPGA での BNN 実装例について検討した。その結果として Yang ら[1]の回路が FPGA での実装に適していることがわかり、それを参考にして実装を行った。この回路は入力値信号とその重みから決まる正負の値をカウンタに入れ、その最終値が正か負であるかによってニューロンの出力を決める仕組みであり、Verilog での実装に向いている。コードなどは公開されていなかったので、独自に BNN モデルを Verilog で実装し、FPGA で動作検証した後チップ化した。試作した機械学習モデルの構造を図3に、チップを図4に示す。チップ動作中の平均電力は82.2 μ W であった。処理時間のみの消費電力は0.21 μ W であると計算され、CPU などと比較して大幅に低消費電力化できることが分かった。

当初の予定より順調に機械学習回路の実装が進んだため、独自の回路についても検討した。機械学習においては図2のように目標とする課題によって、適切な各層のニューロン数が存在するため、ある程度の範囲でニューロンの数などを調整できると望ましい。FPGAでは容易に再構成可能であるが、CMOSチップ化してしまうと特定のニューロン数のものに固定されてしまう。本研究ではそのような従来の回路より柔軟に動作する、新しいモデルの機械学習回路を製作した。それを図5に示す。

[1] M. Yang, et al., ISSCC, 2018, pp. 346-348

図 3 試作した機械学習回路の構成図

図 4 図3の構造を元に製作した機械学習回路チップ

図 5 ニューロン数を変更できる機械学習回路チップ

| 5 . 主な発表論文 |

|------------|

|------------|

〔雑誌論文〕 計0件

| 〔学会発表〕 | 計1件     | (うち招待講演  | 0件/うち国際学会   | 0件`   |

|--------|---------|----------|-------------|-------|

| しナム元収! | י וויום | しつい山い冊/宍 | りし / フロ田原ナム | VII . |

1.発表者名

横式 康史, 高松 洸祐, 德田 崇

2 . 発表標題

Binary Neural Networkによる センサ向け低消費電力機械学習回路

3 . 学会等名

知覚情報/次世代産業システム合同研究会

4.発表年

2023年

〔図書〕 計0件

〔産業財産権〕

〔その他〕

\_

6.研究組織

|                           |                       | 1  |

|---------------------------|-----------------------|----|

| 氏名<br>(ローマ字氏名)<br>(四字書番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

| (別九百亩5)                   |                       |    |

# 7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国相手方研究機関 |  |

|----------------|--|

|----------------|--|