# 科学研究費助成事業 研究成果報告書

平成 26 年 6 月 10 日現在

機関番号: 14301 研究種目: 基盤研究(B) 研究期間: 2011~2013 課題番号: 23300006

研究課題名(和文)時空間タイリングによる高性能シミュレーションコードの生成

研究課題名(英文) Composing High-Performance Simulation Codes by Temporal-Spatial Tiling

#### 研究代表者

中島 浩 (Nakashima, Hiroshi)

京都大学・学術情報メディアセンター・教授

研究者番号:10243057

交付決定額(研究期間全体):(直接経費) 14,700,000円、(間接経費) 4,410,000円

研究成果の概要(和文):本研究で提案した時空間タイリングは、シミュレーションコードの基本構造である時間・空間の多重ループに対し、広大な空間の走査ループをキャッシュメモリに適合可能な小空間(タイル)単位の走査に分割し、かつ空間タイルの時間的更新過程を複数ステップにわたって繰り返すことで、メモリ参照局所性を改善して高速化する技術である。本研究では、局所視点に基づくコード断片記述による時空間タイリング適用を自動化する枠組の開発と、FDTD法電磁場解析、PIC法プラズマシミュレーション、マルチグリッド法ポアソン求解の各応用に対する時空間タイリングの適用実験を行い、各々について目標とした2倍程度の高速化を達成した。

研究成果の概要(英文): Temporal-Spatial (TS) tiling proposed in this research is an optimization technique to improve the memory access locality in a TS-nested loop, adopted in most of simulation codes as their fundamental structure, by splitting the spatial loop into a set of those for smaller spaces (tiles) fitting to cache memory and by iterating updates on each tile for multiple time steps. In this research, we developed a framework of automatic application of TS tiling based on local-view fragmental coding, and then a pplied TS tiling to applications including FDTD electromagnetic field analysis, PIC plasma simulation, and multi-grid Poisson solver, to confirm each application is accelerated by factor two as we aimed at.

研究分野: 総合領域

科研費の分科・細目: 情報学

キーワード: ハイパフォーマンスコンピューティング タイリング コード生成 コード変換

#### 1. 研究開始当初の背景

実用的なシミュレーションコードの多くは、対象とする系の時間的な状態変化を追跡するものであり、一般的には時刻tにおける系の状態S(t)から微小時刻 $\Delta t$ 後の状態 $S(t+\Delta t)$ を求める計算の繰り返し、すなわち;

# for t=0 to $t_{\text{end}}$ step $\Delta t$ do $S(t+\Delta t) \leftarrow F(S(t))$ ;

のような形で実現される。またほとんどの場合、状態 *S(t)*は多数の状態変数の集合、たとえば空間的な系を離散化した格子点・節点に対して定義される変数の集合であり、上記の擬似コードは;

# for t=0 to $t_{\text{end}}$ step $\Delta t$ do for $\forall s \in S$ do $s(t+\Delta t) \leftarrow f_s(S(t))$ ;

というように、時間に関するループ(時間ループ)がその内側に全ての状態変数を走査するループ(空間ループ)を持つ二重ループ(あるいは多重ループ)構造となる。このような時空間ループを、より一般的に運搬依存性を持つ外側ループと多数の変数・配列要素を直する内側ループからなる構造ととらえると、偏微分方程式の陽的な解法や連立一方程式・固有値などの反復解法などにも見られるなど、高性能計算の分野では頻出するプログラム構造であると言える。

この時空間ループの重大な律速要因は、空 間ループが走査するメモリ領域が広大であ るため、メモリアクセスの時間的局所性が著 しく小さく、高速計算の鍵であるキャッシュ の有効利用がほとんど成されないことにあ る。特に、ある状態変数を更新するために参 照すべき状態変数の集合が小さくかつ空間 的に局在する問題、すなわち空間分割による 並列計算が容易な問題ほど、時間的局所性の 欠如が顕著となる。たとえば7点差分解析の ように、3次元格子空間の各格子点上の状態 変数を隣接6格子点の状態変数により更新 する場合、全格子空間(たとえば 1000<sup>3</sup>)の 走査中に各状態変数はわずか7回しか参照 されず、時間的局所性をほとんど見出すこと ができない。

一方、近年のスカラー並列型スーパーコンピュータやそれを支えるマルチコアプロセッサでは、演算性能とメモリ性能の乖離が確実に進行しており、ほとんどの時空間ループの性能はメモリバンド幅によってのみ定まる状況にある。また GPGPU やメニーコアプロセッサにおいても演算性能とメモリ性能の比はマルチコアプロセッサと大差なく、時空間ループの律速要因がメモリバンド幅であることに変わりはない。

#### 2. 研究の目的

本研究では、時空間ループ実行の律速要因である、メモリ参照の時間的局所性の欠如を解決することを目的として行った。具体的には時空間ループを、空間ループを断片化した空間タイルと時間方向の一定回数反復である時間タイルを組み合わせた時空間タイル

を単位として分割し、時空間タイル内ではメモリアクセスの時間的局所性が著しく向上することを利用して高速化する、時空間タイリング技法の確立が目的である。また我々の従来研究成果である並列化技法ライブラリループ内に多数の関数・手続呼出や複雑な依存関係を持つ一般的なアプリケーションを対象に、時空間タイリングを施したコードの自動変換・自動生成を行うことを目指した。

## 3. 研究の方法

# (1) 時空間タイリングの概要

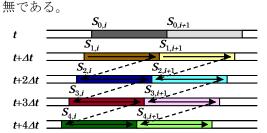

時空間タイリングは、時間方向のタイルサイズをm、基準時刻tからの時間差 $k\Delta t$ に応じて状態変数集合 $S(t+k\Delta t)$ をn分割した空間タイルを $S_{k,i}$ ( $1 \le i \le n$ )とすると;

for t=0 to  $t_{\text{end}}$  step  $m\Delta t$  do for i=1 to n do for k=1 to m do for  $\forall s$ = $S_{k,i}$  do  $s(t+k\Delta t) \leftarrow f_s(S(t+(k-1)\Delta t))$ ;

のように元の時空間二重ループを、外側から順に時間タイル間、空間タイル間、時間タイル間、時間タイルである。 $S_{k,i}$ は図 1 に模式的に示するきに、空間ループの走査順序(左から右)と状態変数間の依存関係(左右の隣接点に依存)により定まり、ほとんどの場合は同じi により定まり、ほとんどの場合は同じi にこて大きな共通部分を持つ。この共通とができ、かつkのループ中でm回連続更新される、更新時に参照される他の変数も含分ができ、かの変数を元々の変数集合に一致される、良好な時間的局所性を持つ。また共通部分ともの変数を元々の変数集合に一致といいまたは皆による空間的オーバヘッドは微小または皆

図 1: 時空間タイリングの実行過程

# (2) 複雑なループのタイリング

上記の模式図のように空間ループが規則的なステンシル計算であって時間ループ内に直接含まれているごく単純な場合であっても、配列で表現される状態変数 S(t)の要素間依存関係を完全に把握し、それに基づく自動的な変換によって時空間タイリングを適用することは容易ではない。また、たとえばプラズマシミュレーションなどで用いられる PIC (Particle-In-Cell) 法では、時空間ループが;

for t=0 to  $t_{\text{end}}$  step  $\Delta t$  do

#### begin

粒子加速(); 粒子移動(); 電流計算(); 電磁場計算();

#### end

のように複数の関数・手続呼出からなり、かつ状態変数である各粒子の位置・速度が別の種類の状態変数である周囲の格子点の電磁場ベクトルと相互作用する複雑な依存関係を持つため、コード解析による自動的な時空間タイリングの適用は実質的に不可能である

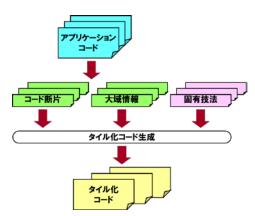

そこで本研究では、空間ループを構成する 状態変数更新に関するコード断片と、ア構造 ケーション固有の知識、すなわちデータ構造、 制御の流れ、依存関係などの大域情報と、 プリケーションに適合したタイリングを施した。 に基づき、時空間タイリングを施した。 を自動生成することを目指した(図 2)。こだを自動生成、空間ループの構造(たとえばたの子集合や3次元格子空間の走査)や意味(がら大きに がいるため、困難な解析を経ずに様々な高速 化・最適化技術を適用することができる。

たとえば PIC 法のプラズマシミュレーションの場合、前述の「*粒子加速*0」などのコード断片は概念的には以下のように表現される。

```

粒子加速(){

p.v[]+=

lf(e[se(p.x)],b[sb(p.x)])*

p.q/p.m; }

粒子位置(){ p.x[]+=p.v[]; }

電流計算(){

j[sj(p.x)]+=cd(p.v)*p.q; }

電磁場計算(){

e[]+=(rb(b[])/mu-j[])/eps;

```

b[]-=re(e[]); } このような局所視点に基づくコード断片と 大域情報からなるプログラミングを行うた めのフレームワークとして、丸山らによる Physis (Maruyama, et al., SC11)をベース言 語として採用し、これに必要な拡張を施すこ ととした。

一方時空間タイリング技法は一種のライブラリの形で表現され、タイリングを適用した時空間ループのスケルトンなどのアプリケーションに依存しない(擬似)コードと、アプリケーション固有のコード、たとえばPIC法では粒子を空間タイルごとに管理するためのコードなどから構成される。この技法ライブラリと、アプリケーション固有のコード断片・大域情報を融合・結合することにより、タイル化コード生成が行われる。

# (3) 自動チューニング

時空間タイリングの有効性は、空間タイル $S_{k,i}$ の大きさ・形状と時間方向のタイルサイズmに強く依存する。空間タイルの大きさは、基本的にプロセッサのキャッシュサイズに

図 2: タイル化コードの生成方式

より定まるが、たとえば3次元問題でのx,y, z 方向それぞれの最適な大きさは配列データのメモリ上でのレイアウト、多重ループの制御コスト、タイル内の計算を分担するスレッド数、キャッシュの構造・性能やメモリバンド幅など、アプリケーションやプロセッサアーキテクチャの性質に強く依存する。また時間方向のタイルサイズも、プロセス並列実行の際のプロセス間通信のバンド幅や遅延に左右される。

したがって、最適なタイリングパラメータを解析的に求めることは極めて困難であり、何らかのチューニングが必要となる。そこで我々が開発した並列スクリプト言語 Xcrypt (Hiraishi, et al., WHIST2012)を用いて、広大なパラメータ空間を効率的に並列探索する枠組みを構築することとした。

## 4. 研究成果

本研究で対象とした主なアプリケーションである、FDTD 法による3次元電磁場解析、PIC 法によるプラズマシミュレーション、およびマルチグリッド法によるポアソン方程式ソルバについて、以下の成果を得た。

## (1) FDTD 法

本研究に先行して行った FDTD 法の時空間タイリングでは、時間方向の依存性を解決するためにタイル周辺部分の計算を冗長に実施していた(南ほか、情処論 ACS, 4(2))。本研究ではまず、図 1 に模式的に示したように、時間方向の計算の進行とともにタイルを空間的にずらす手法を見出し、冗長計算を完全に排除することに成功した。その結果、4 コアプロセッサを用いたスレッド並列実行では、タイリング適用による性能向上を、従来の 1.2 倍を大きく上回る 2.1 倍とすることができた(雑誌論文[2])。

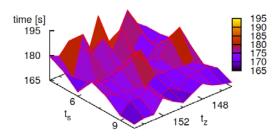

また上記の研究では空間タイルの形状を 立方体に限定してタイルサイズと性能の関 係を調べたが、メモリアクセスが連続する空 間軸やスレッド分割の対象となる空間軸が 存在することから、空間的に非対称の直方体 形状が優れていることも示唆された。また直 方体の形状を様々に変化させて性能との関

図 3: タイルサイズと性能の関係

係を調査した結果、図 3 に示すように非常に不規則な関係性を有していることが確認された。そこで前述のように X で関していることが確認でいた。そこで前述のように X で関いて、事前知識に基づくパラメータ空間の制限、モンテカルロ法による粗い探索、および準最合わせた、オフライン自動チューニングの枠組を開発して、最適パラメータの並列探索を行った。その結果、8 コアプロセッサを用いたスレッド並列実行では、立方体タイルでは  $40^3$  の空間タイルと m=17 の時間タイルが最適で 2.0 倍の加速効果となるのに対し、 $320 \times 10 \times 24$  の直方体タイルと m=15 が最適解として得られ、加速効果を 2.3 倍に向上させることができた(学会発表[3,5])。

また成果の発表には至っていないが、タイル内の計算のスレッド並列化のための2次元あるいは3次元分割、タイルを単位としたスレッド並列化、プロセス並列化の際のプロセス間通信の遅延隠蔽法などについても検討を行った。

## (2) PIC 法

まず、PIC 法の空間ループに対する局所視 点に基づくコード断片の記述方法について、 その要件と有効性を明らかにした(学会発表 [10,11])。続いて、空間全体を走査する複数 のループを1個のループに統合するループ融 合によって、宇宙プラズマコードでは 1.2 倍、 また核融合プラズマコードでは 2.0 倍の性能 向上が得られることを明らかにした。しかし 宇宙プラズマコードを詳細に解析した結果、 ループ融合によって反復あたりの演算・操作 の数が増加し、かつ条件分岐などコンパイラ による最適化を阻害する要因も増加するた め、これらが参照局所性の改善による性能向 上を抑えることが明らかになった。そこで単 純にループ融合を行うのではなく、個々の操 作に対してタイリングを施した上でタイル への操作を連結する変換が必要であること と、ローレンツ力や粒子移動に伴う電流成分 の計算など元々のコードでも反復あたりの 演算・操作の数が多いものに対しては、ルー プ分割を施した結果にタイリングを適用す る必要があることが明らかになった。

また本研究に先行する研究成果であるPIC 法の動的負荷分散ライブラリ OhHelp (Nakashima, et al., ICS2009)を用いたプロセス並列化では、プロセス単位で時間方向のタイリングを行い、プロセス間の粒子移送や 負荷均衡操作の起動頻度を減らすことが効果的であることが明らかになった。この時間的タイリングの結果、1.8 倍の性能向上が得られることを明らかにした(雑誌論文[1,3]、学会発表[2])。

# (3) マルチグリッド法ポアソンソルバ

マルチグリッド法によるポアソン方程式の求解操作は、一種の時間方向ループであるVサイクルの反復に大域的な逐次過程が含まれているため、空間タイルに局所的な時間発展操作を施すことはできない。しかしPIC法のタイリングと同じように、空間的な状態変数に対する一連の操作を時空間タイリングすることを援用してタイリングすることとを見効であり、これにより4個の4コアプロセッサを有するSMPノードでのスレッド並列実行で、1.2 倍の加速効果が得られることを見出した。

さらに、空間タイルに対して局所的な反復 スムージングを行う乗法シュワルツスムー ジングを行うことで、ソルバの収束性を向上 させつつ、本来的な時空間タイリングを適用 可能な問題とできることを見出した。この新 たなスムージング方式により、前述の SMP ノードでは操作間のタイリングとの組み合 わせで1.6倍の加速効果を、また2個の8コ アプロセッサからなるノードを 14 個用いた 216 プロセス並列実行では 1.5 倍の加速効果 を、それぞれ得ることができた(雑誌論文[4]、 学会発表[7,9])。また、これも PIC 法のタイ リングで述べたループ分割とタイリングの 組み合わせが、本質的に逐次過程であるガウ スザイデル法スムージングに対する SIMD 演算の部分的活用に有効であり、メニーコア プロセッサ Xeon Phi での 240 スレッド並列 実行で 1.3 倍の加速効果が得られることも見 出した(学会発表[1,4])。

# 5. 主な発表論文等

〔雑誌論文〕(計6件)

- [1] Yohei Miyake, Chris M. Cully, Hideyuki Usui, <u>Hiroshi Nakashima</u>. Plasma Particle Simulations of Wake Formation behind a Spacecraft with Thin Wire Booms. J. Geophys. Res., 查 読有, Vol. 118, No. 9, 2013, pp. 5681-5694, doi: 10.1002/jgra.50543.

- [2] 南武志, <u>岩下武史</u>, 中島浩. 冗長な計算を伴わない 3 次元 FDTD 法の時空間タイリング. 情報処理学会論文誌:コンピューティングシステム,査読有, Vol. 6, No. 1, 2013, pp. 56-65, http://id.nii.ac.jp/1001/00089920/.

- [3] Yohei Miyake, Hideyuki Usui, Hirotsugu Kojima, and <u>Hiroshi Nakashima</u>. Plasma Particle Simulations on Stray Photoelectron Current Flows Around a Spacecraft. J. Geophys. Res., 查読有, Vol. 117, No. A09210, 2012, pp. 1-13,

- doi: 10.1029/2012JA017673.

- [4] 河合直聡, 岩下武史, 中島浩. ブロック 化赤-黒順序付け法による並列マルチ グリッドポアソンソルバ. 情報処理学会 論文誌: コンピューティングシステム, 査読有, Vol. 5, No. 3, 2012, pp. 1-10, http://id.nii.ac.jp/1001/00082469/.

- [5] Yasuhito Takahashi, <u>Takeshi Iwashita</u>, <u>Hiroshi Nakashima</u>, Tadashi Tokumasu, Masafumi Fujita, Shinj Wakao, Koji Fujiwara, Yoshiyuki Ishihara. Parallel Time-Periodic Finite-Element Method for Steady-State Analysis of Rotating Machines. IEEE Trans. Magn., 查読有, Vol. 48, No. 2, 2012, pp. 1019-1022,

- [6] Yasuhito Takahashi, <u>Takeshi Iwashita</u>, <u>Hiroshi Nakashima</u>, Shinj Wakao, Koji Fujiwara, Yoshiyuki Ishihara. Micromagnetic Simulations of Perpendicular Recording Head Using the Parallel Fast Multipole Method Specialized for Uniform Brick Elements. IEEE Trans. Magn., 查読有, Vol. 47, No. 10, 2011, pp. 3805-3808, doi: 10.1109/TMAG.2011.2154305.

doi: 10.1109/TMAG.2011.2171923.

〔学会発表〕(計11件)

- [1] Masatoshi Kawai, <u>Takeshi Iwashita</u>, <u>Hiroshi Nakashima</u>. SIMD Implementation of a Multiplicative Schwarz Smoother for a Multigrid Poisson Solver on an Intel Xeon Phi Coprocessor. Intl. Mtng. High-Performance Computing for Computational Science, 2014年7月2日, Eugene, OR, USA.

- [2] Yohei Miyake, <u>Hiroshi Nakashima</u>. Low-Cost Load Balancing for Parallel Particle-in-Cell Simulations with Thick Overlapping Layers, Intl. Symp. Parallel and Distributed Processing with Applications, 2013 年 7 月 18 日, Melbourne, Australia.

- [3] Takeshi Minami, Motoharu Hibino, <u>Tasuku Hiraishi</u>, <u>Takeshi Iwashita</u>, <u>Hiroshi Nakashima</u>, Performance Improvement of Three-Dimensional Tiled FDTD Kernel Based on Automatic Parameter Tuning, Intl. Conf. Computation on Electromagnetic Fields, 2013 年 7 月 3 日, Budapest, Hungary.

- [4] <u>Takeshi Iwashita</u>, Akihiro Ida, Masatoshi Kawai, <u>Hiroshi Nakashima</u>. Performance Evaluation of Multithreaded Iterative Solver on Recent Processors. 2013 SIAM Conf. Computational Science and Engineering, 2013 年 2 月 18 日, Boston, MA, USA.

- [5] 日比野元春, 南武志, 平石拓, 岩下武史,

- <u>中島浩</u>. Xcrypt を用いた 3 次元 FDTD 法 プログラムの自動チューニング. 日本応 用数理学会 2012 年度年会, 2012 年 8 月 31 日, 稚内市.

- [6] Yohei Miyake, <u>Hiroshi Nakashima</u>, Hideyuki Usui. Development of a Scalable PIC Simulator for Spacecraft-Plasma Interaction Problems. Intl. Mtng. High-Performance Computing for Computational Science, 2012 年 7 月 19 日, Kobe, Japan.

- [7] Masatoshi Kawai, <u>Takeshi Iwashita</u>, <u>Hiroshi Nakashima</u>, Osni Marques. Parallel Smoother Based on Block Red-Black Ordering for Multigrid Poisson Solver. Intl. Mtng. High-Performance Computing for Computational Science, 2012年7月17日, Kobe, Japan.

- [8] Takeshi Iwashita, Yasuhito Takahashi, Hiroshi Nakashima. Algebraic Block Multi-Color Ordering Method for Parallel Multi-Threaded Sparse Triangular Solver in ICCG Method. Intl. Parallel and Distributed Processing Symp., 2012 年 5 月 22 日, Shanghai, China.

- [9] 河合直聡, <u>岩下武史</u>, <u>中島浩</u>. ブロック 化赤ー黒順序付け法による並列マルチ グリッドポアソンソルバ. ハイパフォー マンスコンピューティングと計算科学 シンポジウム, 2012 年1月 26 日, 名古 屋市.

- [10] <u>Hiroshi Nakashima</u>. Local View Kernels: A New Programming Scheme for Plasma Simulation. Plasma Conf., 2011 年 11 月 23 日, Kanazawa, Japan.

- [11] <u>Hiroshi Nakashima</u>. Generator for Library and Application; Splitting What & How by Domain-Specific Local-View Programming. Intl. Cong. Industrial and Applied Mathematics, 2011 年 7 月 22 日, Vancouver, Canada.

[その他]

ホームページ等

- [1] OhHelp ライブラリ公開ページ, http://www.para.media.kyoto-u.ac.jp/ ohhelp/

- 6. 研究組織

- (1)研究代表者

中島 浩(NAKASHIMA HIROSHI) 京都大学・学術情報メディアセンター・教 授

研究者番号: 10243057

(2)研究分担者

岩下 武史(IWASHITA TAKESHI) 京都大学・学術情報メディアセンター・准 教授

研究者番号: 30324685

# (3)連携研究者

平石 拓 (HIRAISHI TASUKU)

京都大学・学術情報メディアセンター・助

数

研究者番号:60528222

大村 善治 (OMUA YOSHIHARU)

京都大学・生存圏研究所・教授

研究者番号:50177002

村田 澄彦(MURATA SUMIHIKO)

京都大学・大学院工学研究科・准教授

研究者番号:30273478