#### 研究成果報告書 科学研究費助成事業

平成 26 年 6 月 1 3 日現在

機関番号: 17401 研究種目: 基盤研究(B) 研究期間: 2011~2013

課題番号: 23300017

研究課題名(和文)ディペンダビリティを備えた高性能FPGAアーキテクチャに関する研究

研究課題名(英文) A Study of High Dependability Reconfigurable Logic Architecture

#### 研究代表者

飯田 全広(IIDA, Masahiro)

熊本大学・自然科学研究科・准教授

研究者番号:70363512

交付決定額(研究期間全体):(直接経費) 12,300,000円、(間接経費) 3.690.000円

研究成果の概要(和文): SoC市場は、高集積化の進展とともに多様化しており、設計はより複雑になってきている FPGAの搭載はこの問題を解決策として有望である。しかし、FPGAは大量のメモリからできているため、ソフトエラ・

。FPGAの搭載はこの問題を解决束として有宝でのる。しかし、「FONIA八宝の人」という。ことでは、が発生したときに回路故障につながる。 本研究は、信頼性の高いリコンフィギャラブル・ロジックのアーキテクチャとして、SoC用フォールトトレラントFPG A (FT-FPGA) アーキテクチャと、その設計ツール (CAD) を提案している。また、FT-FPGAの試作チップを開発し、このチップの一連の評価によって、FT-FPGAは、ハードエラーおよびソフトエラーの回避と自動修復の能力を有することを確認した。

研究成果の概要(英文): System on a chip(SoC) market has become diversified, with the development of high integration density, VLSI designs are becoming more complex and longer design cycles are required. Reconf igurable logic devices such as field-programmable gate arrays (FPGAs) are used widely as a solution to the above problems. However, FPGA which has the large quantity of configuration memory bits used for user log ic becomes undependable circuits when soft error such as single event upset (SEU) occurs. In order to solve the above problems, high dependable reconfigurable logic technology is researched in the

is research. We proposed fault-tolerant FPGA(FT-FPGA) architectures and their computer-aid design (CAD) for intellectual property (IP) cores for SoC. In addition, we developed prototype chip of FT-FPGA. We confir med that by a series of evaluation of this chip, FT-FPGA has the capability of avoidance of hard and soft errors, automatic repair of user circuit.

研究分野: 総合領域

科研費の分科・細目: 情報学・計算機システム・ネットワーク

キーワード: リコンフィギャラブルシステム FPGA ディペンダブルシステム ソフトエラー SEU LSI試作

#### 1.研究開始当初の背景

半導体製造技術の微細化に伴う NRE 高騰により、高付加価値の製品を低コストで開発する LSI 設計の仕組みが必須となっている.その解決策として、システム LSI 上にプログラマブルロジックを搭載するアイデアが産まれて久しいが未だ製品レベルでは実現していない.日本メーカとしての独自性を保ち収益を確保するためには、豊富な応用技術を生かせるシステム LSI 分野にプログラマブルロジックを一刻も早く投入し、利益を得るための仕組みを早急に確立する必要がある.

### 2.研究の目的

本研究の目的は, SoC(System on a Chip)上 に搭載可能なリコンフィギャラルブロジッ クの実現である、本研究で解決するリコンフ ィギャラルブロジックの課題は 第一にASIC と比較して消費電力が高いこと,第二に LSI テストが困難なこと,第三にソフトエラー対 策が不十分であることである、本研究は、 LUT(Look Up Table)より少ないメモリ数で同 等の機能が実現できる論理セルを用い,ハザ ードレスの誤り訂正回路でソフトエラーを 隠蔽・検出し,動的な書換えにてデータの修 復(スクラビング)を行うことで,自動的に ソフトエラーより復旧する機構を備えるデ バイスアーキテクチャを構築する.また,デ バイスレベルでテスタビリティを考慮する ことで,高いテスト網羅率を効率良く達成可 能である.また,上記の機能を実現した LSI を試作し,実機にて効果を確認する.

## 3.研究の方法

研究期間は3年とし,研究項目は以下の4つの小研究項目に分割して実施する.小研究項目は以下の通り.

- (1) 基本論理セルアーキテクチャの研究・開発(使用メモリおよび構成トランジスタ数を削減した論理セルおよび配線アーキテクチャの評価・試作)

- (2) 高信頼化手法の研究(ソフトエラーに対する高信頼化支援機構の検討・評価)

- (3) テスト容易化設計の研究(故障検出手法の検討・評価およびテスタビリティを確保したタイル構造の検討)

- (4) EDA ツール開発(低消費電力化指向設計ツールおよびプログラマブルコア搭載支援ツールの開発)

また,最初の2年間でデバイスアーキテクチャ,高信頼化手法,テスト設計手法の確立を目指す.それらを基に最終年度でチップ試作を行い,評価および研究成果のまとめを行う.EDAツール開発は3年間を通して行い,最終年度の試作チップの評価時までに完成させる.

#### 4. 研究成果

(1) 基本論理セルアーキテクチャの研究 本研究項目では,シャノン展開された部分

関数の特徴に基づく少構成メモリ論理セル を提案した .

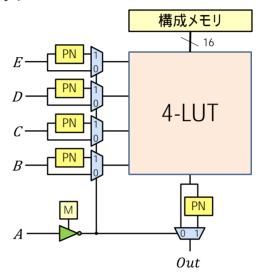

FPGA の論理セルは、アプリケーションの種類に依らず高い論理カバー率を持っていることが望ましい、そのような論理セルを考案するために、まずベンチマークセットの頻出論理を調査する、その結果、頻出論理の多くが、シャノン展開して得られた2つの部分関数のうち一方にある操作を加えると、もう一方の部分関数に変換できるという特徴を持っていることがわかった。本研究ではその特徴を生かしたSLM(Scalable Logic Module)を提案している、SLM の構造(例)を図1に示す、

図1 5-SLM(4,1111) の構造

部分関数間の変換に必要な入出力操作は,LUT 部の入出力部に付加された PN (Programmable NAND)回路によって行う.この例では4入力 LUT のメモリビットで5入力相当の論理が構築できる。単純に半減とはならないが実装できる論理に対するメモリ量が高効率であるといえる.さらに,SLMを階層化することでより実装効率を向上できることを評価した.

## (2) 高信頼化手法の研究

本研究における FPGA のハードエラー耐性 手法は ,1 )CAD ツールによる回避 ,2 )FPGA アーキテクチャによる回避の 2 種類である . CAD による回避は ,まず LSI テストによっ て故障箇所を特定する . このとき , テストが 短期間で終了するように FPGA 側にテスト支 援回路を追加する . これによって少ないテスト数で高精度に故障を検出する方法を開発 した . また , 故障箇所の特定の後 , CAD ツー ルはそれを避けるように配置配線を行う .

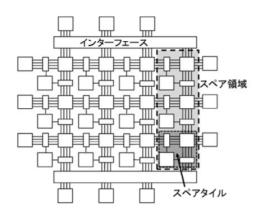

FPGA アーキテクチャによる回避は,先のテストで故障箇所を特定するところまでは共通で,故障情報を FPGA に入力することでFPGA 自体が自動的に故障回避する機構を持つ.具体的には,論理セルアレイにスペアタイル(図 2)を持ち,故障情報に基づきスペアタイルに切り替える方式を開発した.

図2 スペア領域を保持したホモジニアスFPGA 構造

#### (3) テスト容易化設計の研究

故障回避のためにテストによって故障箇所を特定しなければならない。本研究では、テストパタン生成器: Test Pattern Generator (TPG)とテスト結果解析器: Output Response Analyzer (ORA) を FPGA の IOB 内に持つ.すなわち, IOB 内に組み込んだ TPG からテスト用のトグル信号を伝搬させ, IOB 内のORA で伝搬してきた信号を解析する. さらに,コンフィギュレーションデータの最小化を図り,検出時間の節約と故障検出精度の両立を達成した.

## (4) EDA ツール開発

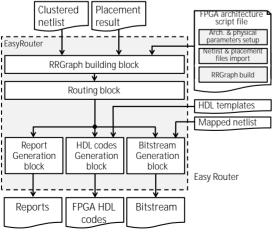

これまでの FPGA 開発ツールは , FPGA 単独で設計が完結するため ,商用 LSI CAD ツールとの連携は必要なかった . しかし , 本研究テーマである SoC に FPGA IPを組み込もうとすると , SoC 全体の設計検証が必要になり ,既存の LSI CAD ツールとの連携は不可欠である . 本研究では ,商用 VLSI CAD ツールとの連携可能な高精度かつ高速な FPGA 設計フレームワーク"EasyRouter"(図3)を開発した .

EasyRouter の特徴は以下の通り

・FPGA の高速プロトタイピング・アカデミックな FPGA 設計フローと商用 VLSI CAD ツール間のリンクである

EasyRouter は C# を用いて開発されている。オブジェクト指向で開発されているため, ソースコードが少なく,管理しやすい.従っ

図3 Easy Routerのブロック図

て、開発期間が短くて済む.また、EasyRouter はスクリプトベースのアーキテクチャ定義 により高い柔軟性を実現している.それによ って EasyRouter は様々な配線構造に容易に 対応可能である.

また,EasyRouter はアーキテクチャ定義と配線結果から自動的にチップ全体の HDL コードおよびコンフィグレーションビットを生成することが出来る.生成されたファイルを用いることで,FPGA IP は商用の VLSI CAD ツールによって高精度および高い信頼性で評価される。複数のアーキテクチャを評価する際,VLSI 設計フローはそれぞれのアーキテクチャに対して1回のみ実行される.各ベンチマークを評価する際には,レイアウトから得られた寄生抵抗,容量を用いれば良い.

## (5) チップ試作

これまでの研究成果を評価するためにTSMC65nmプロセスを用いたFT-FPGAチップの試作を行った.具体的には,主に論理セル,ハードエラー・ソフトエラー回避機構を試作チップに搭載し,新規CADツールを用いて評価する.試作チップが完成後,システムレベルでハードエラー・ソフトエラー対策など信頼性関連の動作の検証を行った.商用LSICADツールと連携して,PrimeTimeでSTA情報を用いた計算方法とEasyRouterのモジュール毎にサンプル遅延を用いた計算方法の比較し,各タイミング解析手法の計算精度を試作したチップで実際に検証を行った

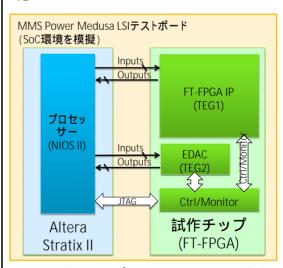

図4 試作チップとシステム環境の構造

図4に試作チップと評価システム環境を示す.試作チップは FT-FPGA の IP であるTEG1,ソフトエラー対策とした EDAC 回路を検証するTEG2,そしてTEG1とTEG2を制御および観測するための Ctrl/Monitor モジュールから構成される.TEG1には論理セル、テスト容易化したホモジニアス配線構造,ハードエラー検出と回避などの研究成果を搭載している.評価環境として,MMS Power Medusa LSI テストボードを使用し,SoC 環

境のシミュレーションを行っている.

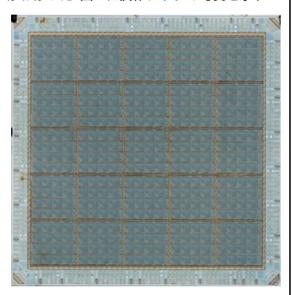

チップ評価の結果、FPGA部においてMAC回路の動作から故障の注入、検出、回避の一連の動作が確認でき、ハードエラー耐性の有効性を確認できた、また、EDAC部においてAND回路の実装から故障の注入、スクラビングによる故障の隠ぺいが確認できたことがら、ソフトエラー耐性の有効性を確認できた。以上のことよりシステムレベルでハードエラー・ソフトエラー対策の有効性を示するとができた。また、EasyRouterで算出する遅延は精度もSTAと比較し約10%の誤差であることがわかり、アーキテクチャの評価や動作周波数を見積もるうえで有効であることがわかった図5に試作チップの写真を示す・

図5 試作チップのダイ写真

# 5.主な発表論文等 (研究代表者、研究分担者及び連携研究者に は下線)

#### [雑誌論文](計5件)

尼崎太樹, 西谷祐樹, 井上万輝, 飯田全 広,久我守弘,末吉敏則,"システム LSI 搭 載 FPGA-IP コア向け物理故障検出及び 回避手法,"信学論 D, Vol. J96-D, No. 12, pp.3019-3029, Dec. 2013. 查読有 Q.Zhao, K.Inoue, M.Amagasaki, M.Iida, M.Kuga, T.Sueyoshi, "FPGA Design Framework Combined with Commercial VLSI CAD", IEICE Transactions on Information and Systems, Vol.E96-D, No.8, pp.1602-1612, Aug. 2013. 查読有 M.Iida, M.Amagasaki, Y.Okamoto, Q.Zhao and T.Sueyoshi, "COGRE: A Novel Compact Logic Cell Architecture for Area Minimization", IEICE Transactions on Information and Systems, Vol.E95-D, No.2, pp.294-302, Feb. 2012. 查読有 K.Inoue, M.Koga, M.Amagasaki, M.Iida, Y.Ichida, M.Saji, J.Iida and T.Sueyoshi, "An Easily Testable Routing Architecture and Prototype Chip", IEICE Transactions on Information and Systems, Vol.E95-D, No.2, pp.303-313, Feb. 2012. 查読有

Q.Zhao, Y.Ichinomiya, <u>M.Amagasaki,</u> <u>M.Iida</u> and <u>T.Sueyoshi,</u> "A Novel Soft Error Detection and Correction Circuit for Embedded Reconfigurable Systems", IEEE Embedded Systems Letters, Vol.3, Issue3, pp.89-92, Sep. 2011. 查読有

# [学会発表](計10件)

Q.Zhao, <u>M.Amagasaki</u>, <u>M.Iida</u>, M.Kuga and <u>T.Sueyoshi</u>, "An Automatic Design and Implementation Framework for Reconfigurable Logic IP Core," Proc. of 23th International Conference on Field Programmable Logic and Applications (FPL2013), Porto, Portugal, Sep. 2013. (2013/9/4 発表)

M.Amagasaki, Kazuki Inoue, Qian Zhao, M.Iida, M.Kuga and <u>T.Sueyoshi,</u> "DEFECT-ROBUST FPGA ARCHITECTURES FOR INTELLECTUAL PROPERTY CORES IN SYSTEM LSI," Proc. of 23th International Conference on Field Programmable Logic and Applications (FPL2013), Porto, Portugal, Sep. 2013. (2013/9/2 発表)

Qian Zhao, <u>M.Amagasaki</u>, <u>M.Iida</u>, M.Kuga and <u>T.Sueyoshi</u>, "An Automatic Design and Implementation Framework for Reconfigurable Logic IP Core," Proc. International Conference on ENGINEERING OF RECONFIGURABLE SYSTEMS AND ALGORITHMS (ERSA2013), Las Vegas, Nevada, USA, pp.36-42, July 2013. (2013/7/22 発表)

Qian Zhao, <u>M.Amagasaki</u>, <u>M.Iida</u>, M.Kuga and <u>T.Sueyoshi</u>, "AN FPGA DESIGN AND IMPLEMENTATION FRAMEWORK COMBINED WITH COMMERCIAL VLSI CADS," Proc. 8th International Workshop on Reconfigurable Communication-centric Systems-on-Chip (ReCoSoC2013), Darmstadt, Germany, July 2013. (2013/7/11 発表)

Q.Zhao, K.Inoue, <u>M.Amagasaki</u>, <u>M.Iida</u>, M.Kuga and <u>T.Sueyoshi</u> "A Novel FPGA Design Framework with VLSI Post-routing erformance Analysis," Proc. 21st ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA2013), pp.271, Monterey, California, USA, Feb. 2013. (2013/2/12 発表)

Y.Nishitani, K.Inoue, <u>M.Amagasaki, M.Iida,</u> M.Kuga and <u>T.Sueyoshi</u>, "A Novel Physical Defects Recovery Technique for FPGA-IP cores," Proc. International Conference on Reconfigurable Computing and FPGAs (ReConFig2012), pp.1-7, Cancun, Mexico,

Dec. 2012. (2012/12/6 発表)

Y.Nishitani, K.Inoue, <u>M.Amagasaki</u>, <u>M.Iida</u>, M.Kuga and <u>T.Sueyoshi</u>, "Evaluation of fault tolerant technique based on homogeneous FPGA architecture," Proc. the 20th IFIP International Conference on Very Large Scale Integration (VLSI-SoC2012), pp.225-230, Santa Cruz, CA, USA, Oct. 2012. (2012/10/10 発表)

K.Inoue, Y.Nishitani, M.Amagasaki, M.Iida and T.Sueyoshi, "Fault Detection and **FPGA** in Various Avoidance of Granularities," Proc. 22th International Conference on Field Programmable Logic and Applications (FPL2012), pp.539-542, Oslo, Norway, Aug. 2012. (2012/8/29 発表) M.Iida. K.Inoue. M.Amagasaki T.Sueyoshi, "An Easily Testable Routing Architecture of FPGA," Proc. the 19th IFIP International Conference on Very Large Integration (VLSI-SoC2011), pp.106-109, Hong Cong, China, Oct. 2011. (2011/10/3 発表)

K.Inoue, H.Yosho, <u>M.Amagasaki</u>, <u>M.Iida</u> and <u>T.Sueyoshi</u>, "AN EASILY TESTABLE ROUTING ARCHITECTURE AND EFFICIENT TEST TECHNIQUE," Proc. 21th International Conference on Field Programmable Logic and Applications (FPL2011), pp.291-294, Chania, Greece, Aug. 2011. (2011/9/6 発表)

[図書](計0件)

#### [ 産業財産権]

- ○出願状況(計0件)

- ○取得状況(計0件)

〔その他〕 ホームページ等

## 6. 研究組織

(1)研究代表者

飯田 全広 (IIDA, Masahiro) 熊本大学・自然科学研究科・准教授 研究者番号: 70363512

## (2)研究分担者

末吉 敏則 (SUEYOSHI, Toshinori) 熊本大学・自然科学研究科・教授 研究者番号: 00117136

### (3)連携研究者

尼崎 太樹 (AMAGASAKI, Motoki) 熊本大学・自然科学研究科・助教 研究者番号: 50467974