# 科学研究費助成事業 研究成果報告書

平成 26 年 6月11日現在

機関番号: 1 2 6 1 2 研究種目: 基盤研究(C) 研究期間: 2011~2013

課題番号: 23560389

研究課題名(和文)単電子トランジスタのマイクロ波モデリング

研究課題名(英文)Microwave Modeling of Single Electron Transistor

研究代表者

本城 和彦(Honjo, Kazuhiko)

電気通信大学・情報理工学(系)研究科・教授

研究者番号:90334573

交付決定額(研究期間全体):(直接経費) 3,900,000円、(間接経費) 1,170,000円

研究成果の概要(和文): 単電子トランジスタ(SET)の電力利得向上は、回路応用時の動作速度向上に重要な改善要素となる。このためSETの電力利得向上のメカニズムを検討し、ソース接合厚が電力利得向上のためのキーファクタであることを見出した。この接合厚を1.25nmまで薄くすると、従来の標準的SET構造に比べて39dBの電力利得改善が、直流からTHz帯に亘って実現できる見通しとなった。

研究成果の概要(英文): A novel approach for investigating the single-electron transistors (SETs) power gain functionality which is one of the most important features of active devices related with operation speed performance is proposed. Moreover, an evaluating method is also introduced to improve the SET power gain due to the influence of junction thickness. It is found that source junction thickness is the key factor affecting the power gain. This important finding is illustrated by taking into account the physical parame ters of sample fabricated SET. According to proposed model, power gain can be improved by ramarkable amount of 39dB at frequencies up to THz regime by reducing 1.25nm in source junction thickness.

研究分野: 複合新領域

科研費の分科・細目: ナノ・マイクロ科学・マイクロ・ナノデバイス

キーワード: ナノ電子デバイス マイクロ波 電力利得 単電子トランジスタ テラヘルツ

## 1. 研究開始当初の背景

ナノスケール電子デバイスとして代表的 な単電子トランジスタ(SET)は、超低消費 電力で高密度実装が可能な電子デバイスと して期待されており、これまでにデバイス 構造の最適化や回路応用に関して数々の研 究報告がなされている。回路応用の大部分 はデジタル論理回路応用を目指したもので あるが、一部には SET の高周波反射特性の 変化を利用したアナログ応用もある。しか しながら、いずれも電子一個を操作するこ とによって得られる超低消費電力性という SET の最大の利点は、負荷駆動能力が極端 に小さいという最大の欠点を併せもってい る。この欠点を克服するために SET と MOSFET を一対にした複合デバイス構成で、 互いの弱点を補い合うという工夫もなされ ているが、SET のそのものの負荷駆動能力 を改善するという試みはこれまでなかった。 このため、SET は超低消費電力ではあるが、 信号の読み込みや読み出しの速度が既存デ バイスに比べて極端に遅いという欠点があ った。

## 2. 研究の目的

- (1) HBT や HEMT などの従来型デバイスにおいて動作速度に強く影響する負荷駆動能力の源泉である電力利得に関して、最適構造、最適回路構造の検討を行い、電子デバイスにおける設計基本原則を見出す。

- (2) SET の電力利得がどのレベルにあるの か把握するマイクロ波等価回路モデルの構 築手法を開発する。

- (3) SET の構造パラメータと回路パラメータの関係を明らかにし、電力利得を向上させる手法を開発する。

#### 3. 研究の方法

(1) 従来型トランジスタとして代表的な HBTとHEMTの電力利得簡易表現式を導出し、 電力利得発現の原理を確認する。また複数 トランジスタを用いて従来型トランジスタにおける電力利得を改善する手法である CASCODE 構成 HBT チップを用いて、各トランジスタのバイアス条件と、バイアス固定方法による電力利得への影響を調べ、電子デバイスの電力利得を上昇させる一般的手法を確認する。

- (2) SET の構造パラメータをベースにして、 3次元デバイスシミュレータ(T-CAD), SET 回路シミュレータ(SIMON2) および Inokawa Model を用いて、SET の電圧電流特性を確認し、これを微分することにより出力コンダクタンスを導出する。この出力コンダクタンス、ならびに2つのトンネル接合の回路モデル化を実行し、SET のマイクロ波帯等価回路を導く。これにより電力利得の計算式を導出する。

- (3) SET のソース側トンネル接合に関して、Gibsonによる絶対零度MIM接合トンネル電流式と Oda 等による電流依存温度モデル式を用いて、トンネル接合電流式を用いてモデル化し、電力利得を最大にするトンネル接合厚さを求める。これにより動作速度や信号読み出し速度が向上される具体的なSET 構造を提案する。

#### 4. 研究成果

(1)複数デバイスによる電力利得向上

HBTとHEMTに対する電力利得の簡易表現式を導き、両者ともトランジスタの語源であるTransfer Resistor機能(すなわち低抵抗の入力側から注入された電流が、高抵抗領域に遷移して入出力間の有能電力差を大きくする)ことが電子デバイスにおける電力利得発生の源泉であることが確認された。また複数デバイスを用いてこのTransfer Resistor機能を加速する代表例であるカスコード増幅器において、二つのトランジスタを独立バイアス型とすることにより、電力利得を大きく保った状態で、低ひ

ずみ化や高電力効率化が達成できることを 提案した。これにより従来型デバイスである HBT、HEMT を用いたマイクロ波回路応用 を一層進展させることができる見通しとな った。またこのような考え方を SET にも適 用できることが明らかにした。

## (2) SET のマイクロ波モデリング

通常の SET の解析で注目するクーロンブ ロッケイドによるクーロンオシレーション やスッテプ特性ではなく、信号の読出しに 重要な役割を果す SET の飽和電流領域に着 目して回路モデルを導き出すことに成功し た。マイクロ波帯出力コンダクタンスは、 SET の電流静特性を精度良く表現できる Inokawa の式を電圧で微分することにより 導出した。加えて SET を構成するドレーン 側およびソース側における二つのトンネル 接合の寸法から規定される容量、ならびに ゲートとアイランド間の微小キャパシタン スを用いて、SET の等価回路モデルを構築 した。このような等価回路により出力有能 電力と信号源有能電力を計算できるように なり、これらの有能電力の比である有能電 力利得が SET においても計算できるように なった。

## (3) 電力利得に関する SET 構造最適化

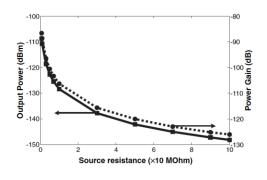

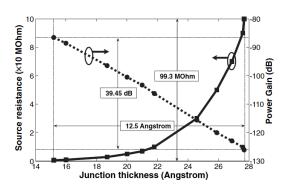

SET の各デバイスパラメータの可変設計 範囲内における電力利得への影響を調べた 結果を表 1、表 2 に示す。R<sub>TS</sub>を下げること による電力利得改善が最も大きく、39.45dB の大幅な利得改善が見込めることが明らか となった。これはショックレーが提唱した Transfer Resistor が SET においても有効 であることを示している。SET の電力利得 の絶対値そのものは単電子を扱うためー 88dB 程度と非常に小さいが、周波数特性は THz 領域までフラットであることが明らか となった。図1はソース抵抗を変えた場合 の電力利得と出力電力の関係である。ソー ス抵抗を小さくすると電力利得、出力電力 は伴に上昇することが分かる。図2にはソーストンネル接合厚さと電力利得および出力電力の関係を示している。単電子による電流を取り扱うため電力そのものおよび電力利得はHBTやHEMTのような従来デバイスよりかなり小さいが、トンネル接合の最適化により40dB程度の改善が見込めることが分かった。このような最適化を行うことによりSET回路の読出し速度をこれまでより大幅に改善できる。

表 1 SET の電力利得感度特性

| Variation of parameters                                     | $G_{\mathbf{P}}$ (dB) |

|-------------------------------------------------------------|-----------------------|

| $R_{\rm TS}~({\rm M}\Omega)~\downarrow 99.3$                | ↑39.45                |

| $R_{\mathrm{TD}}\left(\mathrm{M}\Omega\right)\downarrow0.3$ | ↑1.55                 |

| $C_{\rm G}$ (F) $\uparrow 15 \times 10^{-20}$               | ↑0.48                 |

| $C_{\rm TD}$ (F) $\downarrow 4.99 \times 10^{-20}$          | ↑0.98                 |

| $C_{\rm TS}$ (F) $\downarrow 8.99 \times 10^{-20}$          | ↑1.26                 |

表 2 SET の電力利得計算に用いた接合パラメータ

| Junction material                       | Ti                  |

|-----------------------------------------|---------------------|

| Junction dielectric                     | $TiO_x$ (amorphous) |

| Junction area (nm <sup>2</sup> )        | $10 \times 2^2$     |

| Ti/TiO <sub>x</sub> barrier height (eV) | 0.35                |

| Effective electron mass in $TiO_x$ (m)  | 0.4                 |

| TiO <sub>x</sub> dielectric constant    | 3.5                 |

図1 ソース抵抗が SET 電力利得に与える影響

図2 ソーストンネル接合が SET 電力利得に与える影響

## 5. 主な発表論文等

〔雜誌論文〕(計 6 件)

- (1) D.H.Manh, <u>K. Honjo</u>, "Power Gain Inprovement of Single Electron Transistor," *Japanese Journal of Applied Physics*, vol. 53, No. 04EJ03, pp. 04EJ031-04EJ035, April 2014 (査読有)

- (2) Yuki Takagi, Yoichiro Takayama, <u>Ryo</u> <u>Ishikawa</u>, <u>Kazuhiko Honjo</u>, "A High Efficieny Low Distortion Cascode Power Amplifier Consisting of Independently Biased InGaP/GaAs HBT," *IEICE Trans. Electron*, vol. E97-C, No.1.,pp.58-64, Jan.2014(查読有)

- (3) Ryo Ishikawa, Junichi Kimura, Kazuhiko Honjo, "Low-Distortion Micro wave InGaP/GaAs HBT Amplifier Based on Transient Thermal Behavior in a GaAs Substrate," IEEE Transactions on Components, Packaging and Manufacturing Technology 3/10, 1705-1712 2013/10 (查読有)

- (4) Osamu Miura, Ryo Ishikawa, Kazuhiko Honjo, "Parasitic-Element Compensation Based on Factorization Method for Microwave Inverse Class-F/Class-F Amplifiers," IEEE Microwave and Wireless Components Letters, vol.22/10, pp.1-3, Oct.2012 (查読有) (5) Masahiro Kamiyama, Ryo Ishikawa, Kazuhiko Honjo," 5.65-GHz High -Efficiency GaN HEMT Power Amplifier with Harmonics Treatment up to Fourth Order," IEEE Microwave and Wireless Components Letters, 22/6, 315-317, June 2012 (查読有)

- (6) Satoshi Kawai, Yoichiro Takayama, Ryo Ishikawa, <u>Kazuhiko Honjo</u>," A High-Efficiency, Low-Distortion GaN HEMT Doherty Power Amplifier with a

Series Connected Load," *IEEE Trans*-actions on Microwave Theory and Tech

-niques, 60/2, 352-360, Feb. 2012 (査読有)

#### [学会発表] (計 7 件)

- (1), Luong Duy Manh, Yoichiro Takayama, Ryo Ishikawa, Kazuhiko Honjo, "Power Gain Characteristic of Independently Biased HBT Cascode Chip," 2014 年電子情報通信学会総合全国大会 C-2-24、新潟大学 2014 年 3 月 (查読無)

- (2) Luong Duy Manh, <u>Kazuhiko Honjo</u>,

"Power Gain Characteristic of Single

Electron Transistors (SETs) *International*Conference on Solid State Devices and

Materials (SSDM2013), PS-9-4, pp.

302-303, Fukuoka City, Sept 2013(查読有)

- (3) Satoshi Tasaki, Yoichiro Takayama, Ryo Ishikawa, and Kazuhiko Honjo, "A 1.2-2.0 GHz-band GaAs pHEMT Cascode Power Amplifier MMIC Consisting of Independently Biased Transistors," **Proceedings** of2013 Asia **Pacific** Microwave Conference, Proceedings, Seoul Korea, P1-21, 722-724 Nov. 2013 (査読有)

- (4) Tomohiro Yao, Ryo Ishikawa, Yoichiro Takayama, Kazuhiko Honjo, Hiroyoshi Kikuchi, Takashi Okazaki, Kazuhiro Ueda, Eiichiro Otobe,"Frequency Characteristic of Power Efficiency for 10 W/30W-Class 2 GHz Band GaN HEMT Amplifiers with Harmonic Reactive Terminations," Proceedings of 2013 Asia Pacific Microwave Conference, Soeul Korea, P1-21, 745-747, Nov. 2013 (查読有)

- (5) <u>Kazuhiko Honjo</u>, <u>Ryo Ishikawa</u>, Yoichiro Takayama, "Ultra High Efficiency Microwave Power Amplifier

for Wireless Power Transmission (Invited Paper), Proceedings of the 42nd European Microwave Conference (Amsterdam, The Nether lands), pp. 1339-1342, Oct.2012. (査読有)

(6) Ryo Ishikawa, Junichi Kimura, Kazuhiko Honjo," Analytical Design Method for Thermal Memory Effect Compensation Circuit in Microwave Power Amplifiers," Proceedings of Asia Pacific Microwave Conference (Sydney, Australia), pp.315-318,Dec.2011(査読有) (7) Ryo Ishikawa, Kazuhiko Honjo, "Distributed Class-F/Inverse Class-F Circuit Considering up to Arbitary Harmonics with **Parasitics** 2011 IEEE MTT-S Compensation," Workshop Internatinal Microwave Series on Innovative Wireless Power Transmission, (Kyoto Japan) IWPT2-1, pp.29-32, May 2011. (査読有)

## 5. 研究組織

# (1) 研究代表者

本城和彦 (HONJO Kazuhiko) 電気通信大学・情報理工学研究科・教授 研究者番号 90334573

## (2)研究分担者

石川 亮 (ISHIKAWA Ryo) 電気通信大学・情報理工学研究科・助教 研究者番号 30223892