# 科学研究費助成事業 研究成果報告書

平成 26 年 6 月 6 日現在

機関番号: 17401 研究種目: 挑戦的萌芽研究 研究期間: 2011~2013

課題番号: 23650018

研究課題名(和文)リコンフィギャラブルシステム向けプログラミングモデルに関する研究

研究課題名(英文) Research on programming model for Reconfigurable Systems

研究代表者

飯田 全広(IIDA, Masahiro)

熊本大学・自然科学研究科・准教授

研究者番号:70363512

交付決定額(研究期間全体):(直接経費) 1,900,000円、(間接経費) 570,000円

研究成果の概要(和文):設計資産の再利用が組み込みシステム開発において重要である.本研究では,ソフトウェアの再利用性を維持したままFPGA等のハードウェアを用いたアクセラレーション技術を提案する.提案方式は,ソフトウェアの実行コードから動的にデータパスを生成し,実行時にFPGA上に展開することにより,ソフトウェアの処理速度をアクセラレーションする.評価により,ほとんどの内部ループの実行時間が38.0%,平均42.3%の最大減少することが分かった.この結果は,ソフトウェアの処理速度を増加させながら提案アクセラレーション技術は,ソフトウェアの再利用を促進する可能性があることを示している.

研究成果の概要(英文): In embedded systems, the need for rapid low-cost development has been increasing r ecently. Reuse of design assets is thus an important technique in embedded systems. However, reusability is generally low in software that has been specialized for a particular execution environment. This study p roposes a software acceleration technique that is able to maintain software reusability. The proposed technique accelerates the software processing speed by employing dynamic data path generation from the software execution code. In the results of our work, the execution time of most internal loops was decreased by a n average of 38.0% and a maximum of 42.3%. This result indicates the possibility that our proposed acceler ation technique may promote software reusability while increasing software processing speed.

研究分野: 総合領域

科研費の分科・細目: 情報学・ソフトウェア・プログラミングパラダイム

キーワード: リコンフィギャラブルシステム Java CGRA アクセラレータ プログラミングモデル

これまで計算機システムは,常に小型化と

#### 1.研究開始当初の背景

高性能化が求められてきた、しかし、近年、 グリーンITに代表されるように,環境負荷 を考慮する必要が高まっている.とりわけ, 低消費電力であることのみならず高エネル ギー効率が求められている.現在の計算機シ ステムは、GPP(General Purpose Processor)主体 であり、そこに GPU(Graphics Processing Unit) や専用 LSI で性能を補完するのが一般的であ る.GPP は電力的な問題から動作周波数の向 上競争は終了し,搭載コア数の競争に移行し ている.しかし,ここにきて並列プログラム の記述性の問題が大きな障害になっている. 一方, リコンフィギャラブルコンピューテ ィングシステム(以下, Reconfigurable Computing System: RCS)という FPGA(Field Programmable Gate Array)に代表されるプログ ラマブルロジックを主体とする計算機シス テムが出てきた.並列度の高い連続的なデー タ処理において, RCS は本質的に並列化した GPP や GPU よりも高いコストパフォーマン スおよび電力パフォーマンスを示す,エネル ギー効率が良いシステムである.その理由は, GPP や GPU が処理をする毎に命令フェッチ を必要とし,そこにデータ処理とは無関係な エネルギーを消費している(ノイマンオーバ ーヘッド)のに対し, RCS は回路の再構成時 だけデータ処理と無関係なエネルギー消費 があるだけなので,データ量が多ければデー タ処理にかけるエネルギー比率が相対的に 高くなる .また ,並列化は H/W ゆえにナチュ ラルに行われるため,処理効率が高い.しか し, RCS は, アプリケーション毎に LSI 設計 と同等な回路作成作業を必要とするため, GPP に対して 50 倍, GPU に対しても 6~7 倍もアプリケーションの設計コストかかる. すなわち,設計生産性が低いことが利用・普 及の最大の障害になっている.

### 2.研究の目的

本研究は,並列ソフトウェアを用いるマルチコア/メニーコアや,処理を回路としてマッピングして実行するリコンフィギャラブルシステムのような,性質の異なる並列システムを統合的に扱う並列モデルと,その実現手段である並列プログラミング環境の構築を目的とする.また,計算機システムのエネルギー効率を向上させる手法として,演算精度の制御をプログラミング言語レベルでサポートする.

本研究は,ハードウェアとソフトウェアの既存並列モデルの問題点を抽出・解決した上で,統合した並列処理モデルを構築し,実現したい処理をハードウェアとソフトウェアの区別がないオブジェクトの集合として扱う点に特徴がある.また,本研究ではアプリケーションの設計生産性とシステムのエネルギー効率を重視した評価を行う.

#### 3.研究の方法

研究期間は3年とし,本研究ではRCS向けのプログラミング環境を構築することを目的とし,次の項目をマイルストーンとする.既存の並列モデルの精査と問題点の抽出,プログラミングモデル(並列計算モデル)とプログラミング言語のプロトタイプ実装,

マフロケノミノケ言語のプロトダイノ美表, ユーザビリティを考慮した開発環境の構築, アプリケーション作成および評価の実証実験, プログラミングモデルおよびプログラミング言語のリファインである.

並列処理のモデルを考える場合,これまでの手法,特にソフトウェアによるものハードウェアによるものの両方について精築し,それらを統一的に扱うモデルを構築する.また,ハードウェア(回路)やソロッカンでは、スニーコア等),また,その中間がなアのに述が容易なプログラミング言語が必要である.と記の検討を受けて,部研究項目では,そのプロトタイプを実現を可が必要では,そのプロトタイプを実現を引が必要では,そのプロトタイプを実現を引着す.そして,プログラムの生産性およびエネルギー効率の向上効果の検証に用いるアプリケーションを選定し,GPP,GPU,RCSの3者で評価する.

#### 4. 研究成果

本研究は,上記の通り,当初,並列モデルの構築から新規のプログラミング言語の試作,それらを用いた評価を計画していたが,中間評価において計画を修正した.修正後の研究計画は,第一に既存プログラミング言語からハードウェアを生成し,それらを FPGA上で実行する環境を構築することを目標とした.これにより RCS の問題点の第一(設計生産性の向上)の解決策となり,GPP,GPU,RCS の統一的な設計環境の構築の礎石になる.したがって,本章では既存プログラミング言語からハードウェアを生成する方式に関する研究成果を報告する.

(1) 組込みシステムを対象としたリコンフィギャラブル Java アクセラレータの構

本研究では、ソフトウェアの再利用性を維持したまま高速化を行うことを目的とし、Java のバイトコードを複数段の ALU アレイ上に展開し実行するリコンフィギャラブルアクセラレータを提案する。Java の実行ファイル記述であるバイトコードはスタックベースの処理では、オペランドが全てスタックという単一の空間上に、スタックのという単一の空間上に、は較的容易にハードウェアとして実装可能である。

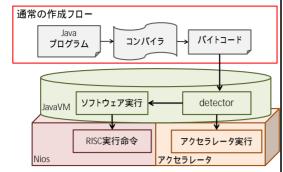

図1 に本研究で提案する Java の実行環境を示す. JavaVM 内にアクセラレータ上で実行可能な部分を検出する機能を追加し,検出した部分のバイトコードをアクセラレータに送信することで,アクセラレータ上での処理を可能とする.

図1 提案アクセラレータの実行環境

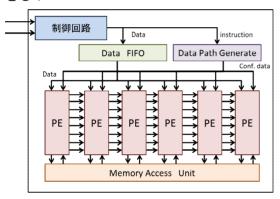

提案するアクセラレータの構成を図 2 に示す.アクセラレータは,全体の制御を行う制御回路,実現されるデータパスへの入力を保持しておくレジスタ,メインメモリへのアクセスポート,演算などの処理を行うプロセッシングエレメントへ処理を割り、当てるデータパス生成回路から構成される. ピロセッシングエレメントはメインメモリへのアクセスユニットを利用することができる.

図2 提案アクセラレータの構成

各プロセッシングエレメント(PE)は2個の32bitのALUと,メモリアクセスを扱うために拡張した32bitのALU,16個の32bitレジスタ,メモリアクセス等を制御や割り当てられた命令からデータパスを制御する制御回路から構成される.

スタックベースの処理記述の特徴として (1)命令のオペランドが必ずスタックの先 頭から 2 もしくは 3 個である ((2) ある処 理を行う際に,値がロードされてからストア されるまでに依存関係のある値がロードさ れない,の二つが挙げられる.したがって, スタックを介したデータの入出力は,そのま ま配線によるデータ転送に置き換えること ができる.このことから,PEアレイの接続に 直接変換可能である.また,バイトコード上 の演算はPEのALUの演算に対応しているた め,バイトコードは PE アレイに対する配線 と演算を指定するコンフィギュレーション データに他ならない.この PE アレイは, Coarse-Grained Reconfigurable Array (CGRA) として構築する.

本研究では,ソフトウェアの再利用性を維

持したまま高速化を行うことを目的とし、Java のバイトコードを直接アクセラレーションするリコンフィギャラブルアクセラレータを提案した、検証の結果、ソフトウェアに変更を加えることなく、最内ループ処理の実行サイクル数を平均して 24%削減可能なことが分かった.このことから、Java のバイトコードを直接アクセラレーションすることで、ソフトウェアの再利用性を保ったまま処理の高速化が達成可能である.

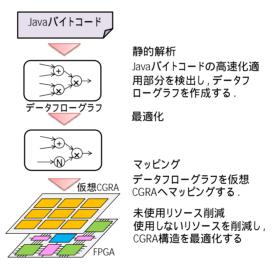

# (2) 仮想 CGRA への Java ソフトウェアのマッピングと FPGA 実装

先の研究では専用の CGRA を構築する必要があった.しかし,これでは汎用的な構造を提供できない.そこで,本研究では,ソフトウェアの再利用性を維持したまま高速化を行うことを目的とし,Java のバイトコードを FPGA 上に展開された仮想的な CGRA でアクセラレーションする方法を提案する.

基本的な実行環境は図1と同じだが,図3のマッピングフローに示すように,FPGAの再構成機構を利用することでアプリケーションに適したCGRA構造をFPGA上に構築する.

図2 マッピングフローの概要

本研究は,CIP 法を用いた電磁波伝播のシミュレーションソフトウェアを適用して性能を評価した.その結果,Nios II によるソフトウェア実行に対して約960倍の高速化が得られた.専用の言語などを使用せずJava記述スタイルの制約のみで高速化させることにより,過去のJavaソフトウェア開発資産を再利用した高速化が期待できる.

#### 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# [雑誌論文](計0件) [学会発表](計3件)

小川裕喜, 尼崎太樹, <u>飯田全広</u>, 久我守弘, 末吉敏則, "仮想 CGRA への Java ソフトウェアのマッピングと FPGA 実装,''信学技報 RECONF2013-47, vol.113,

no.325, pp.45-50, 鹿児島, Nov. 2013. (2013/11/28 発表)

Y.Ogawa, M.Iida, M.Amagasaki, M.Kuga and T.Sueyoshi, "A reconfigurable Java accelerator with software compatibility for embedded systems," Proc. International Workshop on Highly-Efficient Accelerators and Reconfigurable Technologies (HEART2013), pp.39-44, Edinburgh, Scotland UK, June 2013. (2013/6/13 発表)

高田誠也, 尼崎太樹, <u>飯田全広</u>, 久我守弘, 末吉敏則, "組込みシステムを対象としたリコンフィギャラブル Java アクセラレータの一検討," 信学技報 RECONF2012-48, vol.112, no.325, pp.9-14, 福岡, Nov. 2012. (2012/11/27 発表)

[図書](計0件)

〔産業財産権〕

- ○出願状況(計0件)

- ○取得状況(計0件)

〔その他〕

ホームページ等

## 6. 研究組織

(1)研究代表者

飯田 全広 (IIDA, Masahiro)

熊本大学・自然科学研究科・准教授

研究者番号:70363512