# 科学研究費助成事業 研究成果報告書

平成 26 年 5 月 22 日現在

機関番号: 11301 研究種目:挑戦的萌芽研究 研究期間: 2011~2013 課題番号: 23650021

研究課題名(和文)HPC向けアクセラレータアーキテクチャ自動生成・最適化フレームワークの研究

研究課題名 (英文) Study on a framework for auto generation and optimization of HPC accelerator archite ctures

## 研究代表者

佐野 健太郎 (Sano, Kentaro)

東北大学・情報科学研究科・准教授

研究者番号:00323048

交付決定額(研究期間全体):(直接経費) 2,600,000円、(間接経費) 780,000円

研究成果の概要(和文):代表的な高性能計算の一つであるステンシル計算およびセルオートマトン型の計算アルゴリズムドメインに着目し、その専用ハードウェアアクセラレータを自動生成するフレームワークについて研究を実施した。本研究の成果として、シストリックアレイのためのステンシルコンパイラ、およびストリーム計算アクセラレータの高位合成コンパイラを開発した。これらは、FPGAによるリコンフィギャラブル高性能計算の生産性を向上させる重要な基盤技術である。

研究成果の概要(英文): We have focused on an algorithm domain of the stencil computation and cellular aut omata computation that is one of the representative high-performance computations, and then studied a fram ework to automatically generate their acceleration hardware for reconfigurable computation with FPGAs. In this project, we have developed a stencil compiler for an FPGA-based systolic array and a high-level synth esis compiler for FPGA-based stream-computing accelerators. They are significant and fundamental technolog ies for highly productive reconfigurable high-performance computation with FPGAs.

研究分野: 総合領域

科研費の分科・細目: 情報学・計算機システム・ネットワーク

キーワード: アクセラレータ HPC リコンフィギャラブル計算 高位合成 FPGA ステンシル計算 ストリーム計算

#### 1.研究開始当初の背景

近年、高性能計算(HPC)を実現するには電力あたりの実効性能を高めることが必須条件となっているものの、マルチコアプロセカラを相互接続網により接続した巨大スカラ並列機という現在のスーパーコンピュカラが長線上ではブレークスルーは期待では外の延長線上ではブレークスルーは期待の大半では外の実力性能が制約されており、計算コアや計算の大学を増やして並列計算の規模を増加させる。この結果、システムが大規模化する程真のピーク性能の大部分が失われ、電力あたりの実効性能は悪化する。

これに対して、個々の計算問題に対しハー ドウェア自体を最適な形に変えるリコンフ ィギャラブル計算 (RC)が低電力高性能 HPC を実現する方式として有望視されてい る。近年特に大規模化・高性能化・低電力化 が著しい回路再構成可能デバイス FPGA を 用いた RC は、浮動小数点演算のみならず、 ビット・整数・固定小数点演算からゲノム配 列マッチングに渡る幅広いアプリケーショ ンに対して、現在のマルチコアプロセッサの 延長とは別次元の計算性能が期待されてい る。世界的にもアルゴリズムを直接ハードウ ェア化する RC の分野が注目を集めており研 究開発が活発化している他、研究代表者らも、 従来は FPGA が苦手とされてきた浮動小数 点数値計算に対して高い電力あたり性能を 実現するなど、RC によるグリーン HPC の可 能性を示している。

しかしながら、RC を実用化する上では、個々の計算アルゴリズムに対して最適な専用ハードウェアを設計し実装する開発コストが大きな障害となっている。このため、計算アルゴリズムの直接ハードウェア化における生産性の向上が強く求められている。

#### 2.研究の目的

本研究の目的は、リコンフィギャラブルスーパーコンピュータにおいて、最適な専用アクセラレータハードウェア(HW)を個々の計算アルゴリズムに対して容易に開発可能とするためのフレームワーク及び基盤技術の構築である。このために、代表的な HPC 問題から選んだアルゴリズムドメインに対し、計算アルゴリズムのアクセラレータ HW を自動化する。これにより、抽象度の高いアルゴリズム記述から、回路の最適化を経て、FPGA 上で実行可能なアクセラレータHW を自動生成する RC システムを構築する。本システムを実際の数値計算問題に適用し、その有効性を実用レベルで評価する。

# 3.研究の方法

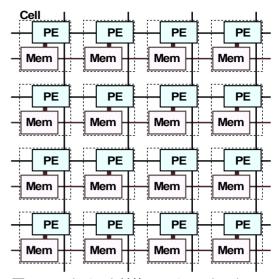

図 1 シストリック計算メモリアーキテクチャ

代表的な HPC 問題であるステンシル計算およびセルオートマトン型の計算アルゴリズムドメインに着目し、その専用ハードウェアアクセラレータについて研究を行った。まず、このアルゴリズムドメインに対しシストリックアーキテクチャ(SA)による専用 HW を提案し、その HW 上で数値計算を実現するための制御マイクロプログラムを自動生成するコンパイラの開発を行った。

ステンシル計算では、2次元または3次元 の計算格子の各点において、近傍の格子点デ ータを参照して更新値を計算する。SA による HW は計算セルの 2 次元配列として構成され、 各計算セルは上下左右の隣接セルと直接デ -タの交換ができる(図1)。計算セルは、計 算格子を2次元配列状に分割した部分格子の それぞれを担当し、その上でのステンシル計 算を並列に実行する。計算セル内部には積和 演算器とローカルメモリを設けてあり、計算 のみならず部分格子データおよび計算の途 中結果を記憶することができる。すなわち、 SA に基づく本 HW は計算格子のデータ自身を 保持すると同時にそのステンシル計算を実 行する「計算メモリ」である。各セルの計算 は、マイクロプログラムにより与えられる。

本研究では、ステンシル計算の簡易記述から各計算セルのマイクロプログラムを自動生成するステンシルコンパイラを開発した。これにより、様々なステンシル計算アルゴリズムを SA 上で容易に実行することが可能となった。しかしながら、SA ハードウェアそのものを自動生成する機能は持たないためりません。また、オンチップメモリである間が困難である。これらの制約を考慮し、ポリン方程式のソルバーや簡易的な流体計算の幾つかの計算が SA 上で実行可能ではあったものの、FPGA を用いたより汎用な RC を目指し、次に、ストリーム計算アーキテクチ

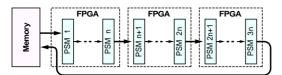

FPGA-based Scalable Streaming Array

## 図2 ストリーム計算アクセラレータ

ャによる専用アクセラレータ HW の研究開発 を行った。

まず、ステンシル計算と、セルオートマトン型アルゴリズムである格子ボルツマン法による流体計算について、それぞれストリーム計算アクセラレータを提案し、試作実計算アクセラレータでは、図2のように計算モンロールが数珠繋ぎとなっており、そこに上野・コールが数珠繋ぎとなっており、そこに上野・シールがら読み出したデータストリームを対すことにより計算を行う。外部外大きの大計算が利用可能となるため比較的大きいまりがある。また、計算モジュールを身数並べることにより、メモリ帯域一定のまま計算性能を向上可能であるとの特長を持つ。

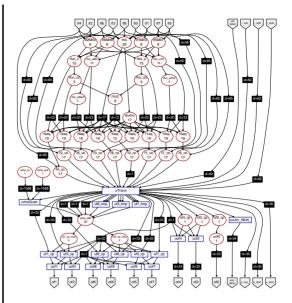

次に、ストリーム型の数値計算を記述する 言語 SPD(Stream Processing Description) と、その高位合成コンパイラである SPGen(Stream Processor Generator)を開発 した。SPD は一連の数式および利用するハー ドウェア関数呼び出しを記述するものであ リ、SPGen は SPD のコードから数式または八 ードウェア関数をノードとするデータフロ ーグラフ(DFG)を生成する。図3に DFG の例 を示す。SPGen は、オープンソースである FloPoCo ツールを使用して数式のパイプライ ンモジュールを生成し、その後に、DFG にデ ータストリームの同期のための遅延モジュ ールを挿入する。この際、遅延素子がなるべ く少ないような最適なストリーム HW を生成 する。最後に、ストリーム計算プロセッサの Verilog-HDL ファイルと、システムオンチッ プ開発ツールである ALTERA 社の Qsys に直接 組み込み可能とするためのインターフェー ス設定ファイルを生成する。これらのファイ ルを FPGA 上に実装した Qsys アクセラレータ フレームワークに組込み、FPGA コンパイラに より合成と配置配線を実行することにより、 実際の FPGA ボードを用いて数値計算のスト リーム処理が可能となる。この他、 PCI-Express により PC に接続した FPGA ボー ドを駆動するための Linux ドライバとライブ ラリを開発した。格子ボルツマン法による流 体計算の SPD 記述を SPGen によりコンパイル し、FPGA 上で実際に計算が可能であることを 確認した。また、その数値計算性能を評価し た。

# 4. 研究成果

本研究の成果は、

(1) FPGA で動作するシストリックアーキテ

図 3 SPGen により生成された DFG の例

クチャのためのステンシルコンパイラ (2) FPGA によるストリーム計算アクセラレ ータの提案とその有効性の確認

(3) ストリーム計算アクセラレータの高位 合成コンパイラである SPGen

である。これらは、ステンシル計算およびセルオートマトン型計算のアルゴリズムドメインに対しリコンフィギャラブル計算の生産性を向上させるものであり、個々の計算アルゴリズムに対して専用アクセラレータ HWを容易に開発可能とするための基盤技術を構築することが出来た。

(1)は、FPGA 上に実装したシストリック計 算メモリ HW を用いて様々なステンシル計算 を容易に実行可能とするもので、最適なシス トリック計算を設計する上で有効である。 (2)は、より汎用な RC を FPGA 上で実現する 方式として、ストリーム計算アクセラレータ の有効性を示すものであり、試作実装により その実証を行っている。(3)は、(2)のストリ - ム計算アクセラレータの設計と実装を容 易とするものであり、抽象度の高い数値計算 の記述から実機上で動作可能なハードウェ アを自動生成可能である。様々なストリーム アクセラレータハードウェアの設計空間探 索が容易に行えることから、FPGA によるリコ ンフィギャラブル高性能計算を実用化する 上で大変重要なものである。実際の計算問題 である流体計算を例題として、SPGen による ストリーム計算アクセラレータの開発を行 い、実機によりその有効性を実証している。

これらの成果について、複数の論文および学会により国内外において発表を行っている。(3)に関しては、採録通知が間に合わず発表論文リストには含めていないものの、その成果を RC 分野で最大規模の国際会議に論文を投稿しており、発表の予定である。

#### 5 . 主な発表論文等

### [雑誌論文](計33件)

Kentaro Sano, Rvotaro Chiba, Tomova Ueno, Hayato Suzuki, Ryo Ito and Satoru "FPGA-based Yamamoto. Custom Computing Architecture for Large-Scale Fluid Simulation with Building Cube Method," Computer Architecture News Special Issue for the proceedings of the International Symposium on Highly-Efficient Accelerators Reconfigurable and Technologies (HEART), 查読有, 印刷中, 2014.

Kentaro Sano, "FPGA-based Custom Computing Accelerator for Computational Fluid Dynamics based on Lattice Boltzmann Method," Proceedings of the 18th Workshop on Sustained Simulation Performance, 查読無, 印刷中, 2014.

Kentaro Sano, Yoshiaki Hatsuda and Yamamoto, "Multi-FPGA Satoru Accelerator for Scalable Stencil Computation with Constant Memory-Bandwidth," IEEE Transactions on Parallel and Distributed Systems (TPDS), 查 読 有 , vol.25, no.3, pp.695-705. 2014. DOI: 10.1109/TPDS.2013.51

伊藤 涼, 鈴木 隼人, 千葉 諒太郎, <u>佐野 健太郎</u>, 山本 悟, "ストリーム計算のための高位合成コンパイラの設計と実装," 電子情報通信学会リコンフィギャラブルシステム研究会 信学技法, 査読無, vol.113, no.418, pp.1-6, 2014. URL:

http://ci.nii.ac.jp/ncid/AA12046591 伊藤 涼, 鈴木 隼人, 千葉 諒太郎, 佐 野 健太郎, 山本 悟, "密結合 FPGA クラ スタによる格子ボルツマン法専用流体計 算機の性能評価, 第27回数値流体力学 シンポジウム講演論文集,査読無, Paper#D06-4. 2013. URL: http://www2.nagare.or.jp/cfd/cfd27/ 千葉 諒太郎, 鈴木 隼人, 伊藤 涼, 佐 野 健太郎, 山本 悟, "フラクショナル ステップ法に基づく非圧縮性流体計算専 用ストリームプロセッサの設計と評価、" 電子情報通信学会リコンフィギャラブル システム研究会 信学技法,査読無, vol.113, no.221, pp.13-18, 2013. URL: http://ci.nii.ac.jp/ncid/AA12046591 Kentaro Sano, Ryo Ito, Hayato Suzuki and Yoshiaki Kono, "Parallel and Scalable Custom Computing for Real-Time Fluid Simulation on a Cluster Node with Four Tightly-Coupled FPGAs," Proceedings of the 23rd International Conference

Field-Programmable Logic and Applications (FPL2013), 查読有, Paper#DS\_7, 2013. DOI: 10.1109/FPL.2013.6645625

千葉 諒太郎, 高野 芳彰, 佐野 健太郎, 山本 悟, 佐々木 大輔, 中橋 和博, "ビ ルディングキュープ法に基づく非圧縮性 流体専用計算機の性能見積もり", なが れ (特集 注目研究 in CFD26), 査読無 (招待論文), vol.32, no.2, pp.117-121, 2013. URL:

http://www.nagare.or.jp/publication/

nagare.html

高野 芳彰, 鈴木 隼人, 千葉 諒太郎, 佐野 健太郎, 山本 悟, "FPGA クラスタ による格子ボルツマン法専用計算機の実 装と性能評価". 電子情報通信学会リコ ンフィギャラブルシステム研究会 信学 技法, 查読無, vol.112, no.377, pp.165-170, 2013. URL: http://ci.nii.ac.jp/ncid/AA12046591 Yoshiaki Kono, Kentaro Sano, and Yamamoto, "Scalability Satoru Analysis of Tightly-Coupled FPGA-Cluster for Lattice Boltzmann Computation," Proceedings of the 22nd International Conference Field-Programmable Logic and Applications, 查読有, pp.120-127, 2012. DOI: 10.1109/FPL.2012.6339275 鈴木 隼人, 高野 芳彰, 千葉 諒太郎, 佐野 健太郎, 山本 悟, "格子ボルツマ ン法専用計算機の設計と FPGA による実 装", 第26回数値流体力学シンポジウム 講演論文集, 查読無, Paper#A09-3, 2012. URL:

http://www2.nagare.or.jp/cfd/cfd26/ 高野 芳彰, 千葉 諒太郎, 鈴木 隼人, <u>佐野健太郎</u>, 山本 悟, "格子ボルツマン 法専用計算機のためのストリーム計算手 法," 第 26 回数値流体力学シンポジウム 講演論文集, 査読無, Paper#A09-2, 2012. URL:

http://www2.nagare.or.jp/cfd/cfd26/ 佐野 健太郎, 高野 芳彰, 鈴木 隼人, 千葉 諒太郎, 山本 悟, "密結合 FPGA ク ラスタの試作と格子ボルツマン計算の実 装", 電子情報通信学会リコンフィギャ ラブルシステム研究会 信学技法, 査読 無, vol.112, no.203, pp.5-10, 2012. URL:

http://ci.nii.ac.jp/ncid/AA12046591 高野 芳彰, <u>佐野 健太郎</u>, 千葉 諒太郎, 山本 悟, "格子ボルツマン法による流体 計算に対する密結合 FPGA クラスタのス ケーラビリティ評価," 電子情報通信学 会リコンフィギャラブルシステム研究会 信学技法, 査読無, vol.112, no.70, pp.55-60, 2012. URL: http://ci.nii.ac.jp/ncid/AA12046591 佐野健 太郎, 初田 義明, 高野 芳彰, 山本悟、"低メモリ帯域で高性能ステン シル計算を実現するスケーラブルストリ ーミングアレイの試作と評価"、電子情 報通信学会リコンフィギャラブルシステ ム研究会信学技法, 査読無, vol.111, no.31. pp.79-84, 2011. http://ci.nii.ac.jp/ncid/AA12046591 Wang Luzhou, Kentaro Sano and Satoru Yamamoto. "Domain-Specific Language and Compiler for Stencil Computation FPGA-based Systolic on Computational-Memory Array, Lecture Notes Computer Science. in Reconfigurable Computing: Architectures, Tools and Applications, 查読有, vol.7199, no.2012, pp.26-39, DOI: 10.1007/978-3-642-28365-9 3 Kentaro Sano, Yoshiaki Hatsuda and Yamamoto. "Performance Evaluation of FPGA-based Custom Accelerators for Iterative Linear-Equation Solvers, Proceedings of the 20th AIAA Computational Fluid Conference. Dvnamics 査 読 有 , Paper#3233 (CDROM), 2011. URL: http://arc.aiaa.org/doi/pdf/10.2514/ 6.2011-3223 Kentaro Sano, Yoshiaki Hatsuda and Satoru Yamamoto, "Domain-Specific Programmable Design of Scalable Streaming-Array for Power-Efficient Computation," Stencil Computer Architecture News Special Issue for the proceedings of the International Workshop Highly-Efficient on Accelerators Reconfigurable and Technologies, 査読有, vol.39, no.4, pp.44-49. 2011. DOI:

10.1145/2082156.2082168 Kentaro Sano, Yoshiaki Hatsuda and Yamamoto, "Scalable Satoru Simple Streaming-Array of Soft-Processors Stencil for Computations with Constant Memory-Bandwidth, "Proceedings of the 19th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, 查読有, pp.234-241, 2011. DOI: 10.1109/FCCM.2011.12

#### [学会発表](計29件)

伊藤 涼、"密結合 FPGA クラスタによる格子ボルツマン法専用流体計算機の性能評価、" 第 27 回数値流体力学シンポジウム、2013 年 12 月 18 日、名古屋大学 Kentaro Sano、 "FPGA-based Custom Computing Accelerator for Computational Fluid Dynamics based on Lattice Boltzmann Method," The 18th Workshop on Sustained Simulation Performance, 2013 年 10 月 29 日, High-Performance Computing Center Stuttgart (HLRS), Universitat Stuttgart, Germany

千葉 諒太郎, "フラクショナルステップ 法に基づく非圧縮性流体計算専用ストリームプロセッサの設計と評価," 電子情報通信学会リコンフィギャラブルシステム研究会, 2013 年 09 月 18 日, 北陸先端科学技術大学院大学

Kentaro Sano, "Efficient Custom Computing of Fully-Streamed Lattice Boltzmann Method on Tightly-Coupled FPGA Cluster," The 4th International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies, 2013 年 6 月 13 日, The University of Edinburgh, United Kingdom

Kentaro Sano, "Parameterized Design and Evaluation of Bandwidth Compressor for Floating-Point Data Streams in FPGA-based Custom Computing," The 9th International Symposium on Applied Reconfigurable Computing, 2013 年 03 月 25 日,米国・カリフォルニア州ロサンゼルス

鈴木 隼人, "密結合 FPGA クラスタによる 格子ボルツマン専用計算機の設計と実装 ", 情報処理学会全国大会, 2013 年 03 月 7日, 仙台市東北大学川内キャンパス 千葉 諒太郎, "ビルディングキューブ法 に基づく非圧縮性流体計算の専用計算機 アーキテクチャに関する一考察", 情報 処理学会全国大会, 2013 年 03 月 07 日, 仙台市東北大学川内キャンパス 田藤 涼 "ストリーム計算のための享位

伊藤 涼, "ストリーム計算のための高位合成コンパイラの設計と実装," 電子情報通信学会リコンフィギャラブルシステム研究会, 2013 年 1 月 28 日, 慶応義塾大学日吉キャンパス

高野 芳彰, "格子ボルツマン法専用計算機のためのストリーム計算手法", 第 26 回数値流体力学シンポジウム, 2012 年 12 月 20 日, 東京都オリンピック記念会館佐野 健太郎, "リコンフィギャラブルHPC のための密結合 FPGA クラスタの開発~並列格子ボルツマン計算による試作クラスタの評価~", 電子情報通信学会第6回再生可能集積システム時限研究会(招待講演), 2012 年 10 月 13 日, 山形大学工学部米沢キャンパス

佐野 健太郎, "密結合 FPGA クラスタの 試作と格子ボルツマン計算の実装",密 結合 FPGA クラスタの試作と格子ボルツ マン計算の実装,2012年09月19日,滋 賀県草津市立命館大学 Kentaro Sano, "Overview of our Tightly-Coupled FPGA-Cluster Toward Custom HPC", Meeting for Joint Research Proposal, 2012年09月03日, The University of Edinburgh, United Kingdom

Yoshiaki Kono, "Scalability Analysis of Tightly-Coupled FPGA-Cluster for Lattice Boltzmann Computation," The 22nd International Conference on Field-Programmable Logic and Applications (FPL2012), 2012 年 08 月 29 日, ノルウェイ・オスロ市

高野 芳彰、"格子ボルツマン法による流体計算に対する密結合 FPGA クラスタのスケーラビリティ評価"、電子情報通信学会リコンフィギャラブルシステム研究会、2012 年 05 月 29 日、沖縄那覇市男女共同参画センター

<u>佐野</u>健太郎, "HPC 分野と Reconfigurable Technology", 次世代リコンフィギュラブルハードウェア創造研究会 JACORN2011(招待講演), 2011 年 10月 14日,福岡市・ホテル一楽

Kentaro Sano, "Performance Evaluation of FPGA-based Custom Accelerators for Iterative Linear-Equation Solvers," the 20th AIAA Computational Fluid Dynamics Conference, 2011年6月27日, 米国・ハワイ州シェラトンホテル

Kentaro Sano, "Domain-Specific Programmable Design of Scalable Streaming-Array for Power-Efficient Stencil Computation," the International Workshop on Highly-Efficient Accelerators and Reconfigurable Technologies, 2011年6月2日,英国・ロンドンインペリアル大学

高野 芳彰, "高性能格子ボルツマン計算のためのマルチ FPGA アクセラレータの性能見積もり", 先進的計算基盤システムシンポジウム SACSIS, 2011 年 5 月 25日, 東京都・秋葉原コンベンションホール

佐野 健太郎, "低メモリ帯域で高性能ステンシル計算を実現するスケーラブルストリーミングアレイの試作と評価", 電子情報通信学会リコンフィギャラブルシステム研究会, 2011 年 5 月 13 日, 札幌市・北海道大学

Kentaro Sano, "Scalable Streaming-Array Simple of Soft-Processors for Stencil Computations Constant with Memory-Bandwidth," the 19th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, 2011 年 5 月3日、米国・ソルトレイク市ユタ大学

# [図書](計2件)

Kentaro Sano and others. "High-Performance Computing using FPGAs (Chapter of FPGA-based Systolic Computational-Memory Array Scalable Stencil Computations), " Springer, pp.279-303, 2013. DOI: 10.1007/978-1-4614-1791-0 佐野 健太郎. 高野 芳彰 . "第3章 ソフ トウェアとハードウェアを適切に使い分 ける - ソフト・コア・プロセッサとアク セラレータ回路の適材適所設計、"CQ出版 ディジタル・デザイン・テクノロジ, no.15, pp.46-64, Nov 1, 2012.

#### 6.研究組織

#### (1)研究代表者

佐野 健太郎 (SANO, KENTARO)

東北大学・大学院情報科学研究科・准教授 研究者番号:00323048

# (2)研究分担者 なし

#### (3)連携研究者

滝沢 寛之 (TAKIZAWA, HIROYUKI)

東北大学・大学院情報科学研究科・准教授 研究者番号:70323996