# 科学研究費助成事業 研究成果報告書

平成 26 年 5 月 29 日現在

機関番号: 1 2 1 0 2 研究種目: 若手研究(B) 研究期間: 2011 ~ 2013

課題番号: 23760283

研究課題名(和文)異種原子導入によるSiС/絶縁膜界面欠陥の消滅とパワーMOSFETの革新

研究課題名(英文)Elimination of interface defects at SiC/insulator by introducing phosphorus and othe r atoms toward innovation of power MOSFETs

#### 研究代表者

矢野 裕司 (Yano, Hiroshi)

筑波大学・数理物質系・准教授

研究者番号:40335485

交付決定額(研究期間全体):(直接経費) 3,400,000円、(間接経費) 1,020,000円

研究成果の概要(和文):高性能SiCパワーMOSFETを実現するためには、SiC/絶縁膜界面欠陥を徹底的に低減する必要がある。本研究では、申請者らが見出した界面へのリン導入を追及することに加え、窒素や水素を含むガスで複合処理することで界面欠陥の徹底的な低減を試み、MOSデバイスのチャネル移動度やしきい値電圧の変動および絶縁膜の信頼性などに与える影響を調査した。その結果、リンと水素の複合処理によりチャネル移動度は大きく向上し、リンと窒素の複合処理やリンを界面に局在させることにより、酸化膜への電子注入耐性の向上に成功した。また、種々のバイアス条件や温度におけるしきい値電圧変動の特性から、界面のトラップモデルを構築した。

研究成果の概要(英文): In order to realize high-performance SiC power MOSFETs, defects at the SiC/insulat or interface should be reduced greatly. In this study, effects of phosphorus introduction into the interface on the reduction of interface defects and improvement in MOSFET performance were investigated. In addit ion combination effects of phosphorus with hydrogen or nitrogen were also investigated. The channel mobility was improved by combination of phosphorus and hydrogen. The flatband and threshold voltage shifts were successfully minimized by both methods of combination of phosphorus and nitrogen and localization of phosphorus near the interface. The model of trap distribution in the SiC MOS structure was built from the threshold voltage instability experiments using various bias conditions and temperatures.

研究分野: 工学

科研費の分科・細目:電気電子工学 電子・電気材料工学

キーワード: 炭化ケイ素 MOSFET 界面準位 しきい値変動 リン

## 1.研究開始当初の背景

人類の持続的発展には、エネルギーの有効 利用が欠かせない。電力変換における損失を 低減するため、電力変換器の重要性が高まっ ており、とりわけそこで使用されるパワー半 導体の高性能化が求められている。現在用い られているSiパワー半導体では、物性値の 制限から飛躍的な発展は望めない。そこで、 Siの限界を大きく超えるSiCが注目さ れている。すでにショットキーダイオードが 国内外のメーカーから市販されているが、ス イッチング素子のパワーMOSFETは実 用化されていない。高性能SiC-MOSF ET実現のための課題のひとつに、「MOS チャネル移動度の改善」がある。従来、Si C / 絶縁膜界面に窒素(N)を導入すること で界面欠陥の低減が進められてきたが、チャ ネル移動度は40cm<sup>2</sup>/Vsで頭打ちの状 況である。この値では、最も用途の多い1k V級デバイスにおいてMOSチャネル抵抗 の占める割合が大きくなり、SiCのポテン シャルを十分に活かせない。また、残留する 界面欠陥のためにしきい値電圧の安定性に 難がある。このため、徹底的な界面欠陥の低 減と100cm<sup>2</sup>/Vs以上の高チャネル移 動度を実現する新技術が熱望されており、こ れを実現するには従来法とは異なったアプ ローチが必要である。

## 2. 研究の目的

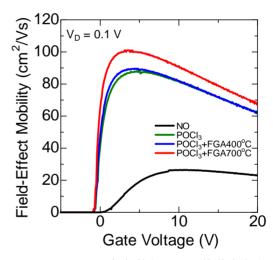

- (1)申請者は、窒素以外の異種原子による界面欠陥の低減を模索し、リン(P)が有望であることを見出している。リンを界面に導入することにより、チャネル移動度は90cm<sup>2</sup>/Vsと、従来法に比べて3倍以上の大幅な改善が見られた。リンに導入による界面欠陥低減をさらに進めるとともに、窒化や水素化を加えることで、リンでは低減できない欠陥をなくして徹底的に界面欠陥を低減させることを第一の目的とする。

- (2)チャネル移動度を改善するだけでなく、 絶縁膜や界面特性の信頼性やしきい値電圧 の制御も重要課題である。そこで、リン導入 したMOSデバイスの信頼性を多角的に評価し、しきい値電圧の不安定性やストレスに 対する特性変動メカニズムを明らかにする ことを第二の目的とする。

- (3) これらを通じて、本プロセスがSiCのMOSデバイスの行き詰まり状態を打破し、革新的性能をもたらすことを示すことを最終目的とする。

### 3.研究の方法

(1)これまでに開発してきたリン導入プロセス(POC1 $_3$ アニール)を最適化するとともに、NOアニールによる界面窒化や水素アニールによる欠陥終端を組み合わせた複合処理を行う。MOSキャパシタやMOSFETを試作し、各種電気特性を詳細に評価する。(2)経時絶縁破壊特性(TDDB)特性を行

- い、絶縁膜の信頼性を評価するとともに、絶縁破壊メカニズムを明らかにする。またゲートバイアスに依存したしきい値電圧の変動を調査する。これを室温だけでなく 200 度の高温においても行う。

- (3) D M O S F E T を設計し、1 k V 級のパワーM O S F E T を作製する。

#### 4. 研究成果

図1:リンと水素導入による移動度向上

次に、リンと窒素を同時に界面に導入する ため、熱酸化膜を形成後に、先にNOアニー ルを1250 で行ってからPOCl<sub>3</sub>アニ ールを1000 で行った。SIMS測定に より、窒素とリンがそれぞれ酸化膜/SiC 界面に導入されていることを確認した。この プロセスでゲート酸化膜を作製したMOS FETのチャネル移動度はPOCl3アニー ル単独処理のものに比べて小さく、47cm ²/Vsであった。NOアニール単独処理の もの(24cm<sup>2</sup>/Vs)と比較するとチャ ネル移動度は改善されているが、NO/PO Cl<sub>3</sub>複合処理ではPOCl<sub>3</sub>単独処理を超 える移動度の改善は見られなかった。これは、 欠陥低減メカニズムにおける窒素とリンの 役割が異なることに起因していると考えら れる。NOアニールでは界面に導入された窒

素は強固なSi・N結合を形成するのに対し、POC1₃アニールで導入されたリンはネットワークに対して3配位の結合となることでひずみを緩和する効果がある。したがって、NOアニールより形成された強固なSi・N結合によってリン導入によるひがノロよるの効果が小さくなったために、NOノPOC1₃複合処理ではPOC1₃単独処理ほどチャネル移動度が向上しなかったと考えられる。しかし、後述するように電子注入耐性が向上するメリットが見られた。

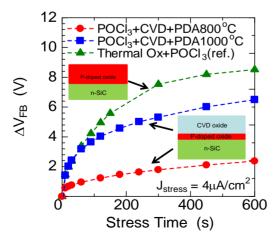

(2) MOS界面欠陥の低減と同様に、信頼性 も重要な課題である。定電流TDDB特性や ストレス印加後のフラットバンドシフトを 調査した。定電流TDDBでは、POCl<sub>3</sub> アニールした試料では定電流を維持するた めの印加電圧が時間とともに大きく上昇す るという、特異な特性を示した。電流注入後 の容量 - 電圧特性を調べると、POC 1 3ア ニールした試料ではフラットバンドシフト が大きくなっており、酸化膜トラップがドラ イ酸化膜やNOアニール酸化膜より多くな ることがわかった。SIMS測定により、酸 化膜中のリンの分布は2 x 1 0 <sup>2 1</sup> c m <sup>- 3</sup> で -様であることがわかっている。通常の動作 条件である低電界(<4MV/cm)であれ ば酸化膜中への電子注入は起こらずにフラ ットバンドシフトは発生しない。しかし、5 MV/cm以上の高電界になりFNトンネ ル現象により電子が酸化膜中に注入される と、電子が酸化膜トラップに捕獲されて大き なフラットバンドシフトを引き起こしてし まう。このことから、リンは酸化膜 / SiC 界面付近にのみ局在させるほうが良いとの 指針を得た。

その指針を基に、界面にのみリンを局在化させる構造を作製した。具体的には、SiC表面に対して $POCl_3$ 処理を行い、その後CVD法により酸化膜を堆積させ、絶縁性を確保するために窒素中で熱処理を行った。1000の熱処理では、リンが界面から酸化膜表面側に拡散する様子がSIMS測定よ

図2:リンの界面局在化による電子注入 耐性の向上

り得られ、界面準位密度は悪化した。熱処理温度を800 に抑えることでリンの拡散を抑制し、界面準位密度は $2\times10^{11}$  c m  $^2$  e V  $^1$  と良好であった。本構造では、定電流ストレス印加に対するフラットバンドシフトを1/4 に低減させることに成功した。このように、酸化膜中のリンのプロファイルを制御することで高品質界面と高電子注入耐性の両立が可能であることを示すことが出来た(図2)

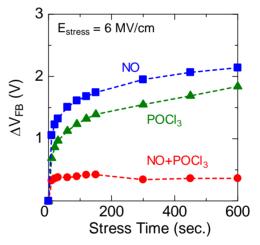

また、もう一つの電子注入耐性向上策とし て、NO/POC13の複合処理も有効であ ることを見出した。6 M V / c m程度の酸化 膜電界までは、界面(近傍)準位や酸化膜中 への電子捕獲はほとんど見られない。6 M V / c mの定電界ストレスの印加時間に対し て、フラットバンド電圧は非常に安定してい た。ストレス前と比較した600秒後のフラ ットバンドシフトは、NOまたはPOCla 単独処理膜では、ともに2 V 程度のシフトが 起こってしまうが、NO/РОС13複合処 理膜では0.4 Vとなり、大幅なフラットバ ンド電圧の安定化に成功した(図3)。また、 その変化は極初期に起こっており、初期の変 化後はストレス印加時間に対する変化は非 常に小さく、0.1 V以下に抑えることに成 功した。

図3:リンと窒素導入によるフラット バンド電圧の安定化

酸化膜の信頼性と同様に、しきい値電圧の不安定性も重要な課題である。SiC-MOSFETに関してしきい値電圧の制御や不安定性に関する報告はまだ少なく、知見が不十分である。そこで、リン及び窒素を界面に導入したMOSFETのしきい値電圧の表達で測定し、評価した。オフからオンになるようにゲート電圧を掃引した場合と、オした場合のしきい値電圧シフト(Vth)を割合のしきい値電圧は、ドレイン電流が10nA(オン時の電流の約1/1000)流れたときのゲート電圧と定義した。

室温における測定では、両試料ともに大き

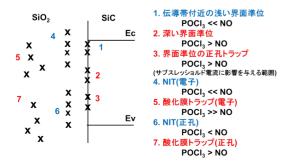

なしきい値電圧のシフトは見られなかった。 (測定開始電圧が - 5 Vのときに Vth は0.1V(POCl<sub>3</sub>)および0.3V(N O))。100 まで昇温すると、NOアニー ル試料では測定開始電圧が - 5 Vのときに 1.2 Vと、大きな Vthが発生した。 方、POC13アニール試料ではサブスレシ ョルド電流がやや増加したものの、150 まで昇温しても Vthは0.3 Vと小さい。 一般的に、温度が上昇するとフェルミ準位が ミッドギャップに近づくこと、および界面準 位に捕獲された電子が放出されやすくなる ことでしきい値電圧は負方向へシフトする。 しかしNOアニール試料では、温度上昇とと もに主にオンからオフ方向への I a - V 。特 性が正方向にシフトする現象が見られた。こ れは、温度上昇に伴ってトンネル効果によっ て界面近傍酸化膜トラップ(NIT)に捕獲 される電子数が増大したためと考えられる。 高温にあると反転層中にエネルギーの高い 電子数が増え、その結果より多くの電子がト ンネル減少でNITにトラップされ、正方向 への Vthが発生したと考えられる。NO 試料にはNITが、POC13試料には酸化 膜中に多くのトラップが存在していること から、NITが多いNO試料にのみオンから オフ方向の掃引における大きな正方向の Vthが表われたと考えられる。また、PO C13試料を200 で測定したときには、 150 以下で測定した時の結果と異なり、 オンからオフ方向の掃引時のしきい値電圧 が負方向の測定開始電圧を大きくするにつ れてしきい値電圧が負方向にシフトした。こ れは、200 の高温では大きな負のゲート 電圧が印加されることで捕獲される正孔数 が増加し、+10Vのオン電圧を印加しても 捕獲された正孔が放出や電子との再結合を 十分に起こさずに捕獲されたままとなった ため、オンからオフへの掃引時のしきい値電 圧の負方向シフトとして表われたと考えら れる。この現象から、POC13アニール試 料では高温で大きな負のゲート電圧を印加 すると、界面準位だけでなく酸化膜中にも正 孔が捕獲される可能性が高い。これらの結果 から、POC13アニール試料では酸化膜ト ラップに、NOアニール試料ではNITに大 きく影響を受けたしきい値電圧の不安定性

図4:界面近傍におけるトラップ分布 モデルとその密度の大小関係

を示すことが明らかとなった。その他にも様々な特性から、図4に示すような界面近傍におけるトラップの分布モデルを提案した。しきい値電圧の不安定性をなくすには、これらの欠陥の除去が必要である。

(3)パワーMOSFETのチャネル部のラフネスが特性に与える影響を調べるため、界面ラフネスの異なるMOSFETを作製し、ごでした。ラフネスにより界面準位密度はほとんど変わらないものの、ドレイン電流値でと方性が観測された。マクロステップ端部に厚く形成され、チャネル内の反転層電子密度が小さくなり局所的に厚く形成されるためと考えられる。パワーMOSFETの作製を行うことがが、本研究で開発したプロセスがSiCパワーMOSFETに革新をもたらすことを示す基礎的かつ重要なデータを取得できた。

### 5 . 主な発表論文等

#### 〔雑誌論文〕(計8件)

- 5年 大野裕司,畑山智亮,冬木隆,「ゲート酸化膜へのリン導入によるSiC-MOS界面欠陥の低減と MOSFET の高性能化」,表面科学, Vol.35, No.2, pp.90-95 (2014).

DOI: 10.1380/jsssj.35.90,査読有.

- H. Yano, T. Araoka, T. Hatayama, and T. Fuyuki, "Improved Stability of 4H-SiC MOS Device Properties by Combination of NO and POCI<sub>3</sub> annealing", Mater. Sci. Forum, Vols.740-742, pp.727-732 (2013). DOI: 10.4028/www.scientific.net/MSF.740-742.727, 査読有.

- H. Yano, T. Hatayama, and T. Fuyuki, "POCI<sub>3</sub> Annealing as a New Method for Improving 4H-SiC MOS Device Performance", ECS Trans., Vol.50, No.3, pp.257-265 (2012). DOI: 10.1149/05003.0257ecst, 查読有.

### [学会発表](計28件)

- H. Yano, A. Osawa, T. Hatayama, and T. Fuyuki, "Comparative Study of Threshold Voltage Instability in 4H-SiC MOSFETs with POCl<sub>3</sub>- and NO-Annealed Gate Oxides", The International Conference on Silicon Carbide and Related Materials 2013 (ICSCRM2013), Miyazaki (Japan), 2013/10/2.

- H. Yano, T. Hatayama, and T. Fuyuki (Invited), "POCI<sub>3</sub> Annealing as a New Method for Improving 4H-SiC MOS Device Performance", PRiME 2012 (Pacific Rim Meeting on Electrochemical and Solid-State Science), Honolulu (HI, USA), 2012/10/10.

3. <u>H. Yano,</u> T. Araoka, T. Hatayama, and T. Fuyuki (Invited), "Improved Stability of 4H-SiC MOS Device Properties by Combination of NO and POCl<sub>3</sub> Annealing", The 9th European Conference on Silicon Carbide and Related Materials (ECSCRM2012), Saint-Petersburg (Russia), 2012/9/5.

## [図書](計2件)

- 1. <u>矢野裕司</u>、エヌ・ティー・エス、「ポストシリコン半導体 ナノ成膜ダイナミクスと基板・界面効果 」、(2013). (分担:第2編、第1章、第4節 SiCデバイスプロセスにおける新規表面・界面改質技術 pp.94-104).

- 2. <u>矢野裕司</u>、S&T 出版、「SiC パワーデバイスの開発と最新動向 普及に向けたデバイスプロセスと実装技術 」 岩室 憲幸 監修 (2012). (分担:第2章 第4節 MOS 界面欠陥の低減技術と高品質化pp.42-52).

# 〔産業財産権〕

出願状況(計0件) 取得状況(計0件)

## 6.研究組織

(1)研究代表者

矢野 裕司 (YANO, Hiroshi)筑波大学・数理物質系・准教授研究者番号: 40335485