# 科学研究費助成事業 研究成果報告書

平成 27 年 4 月 13 日現在

機関番号: 1 1 1 0 1 研究種目: 基盤研究(C) 研究期間: 2012~2014

課題番号: 24500052

研究課題名(和文)次世代型ユビキタスプロセッサのためのクロックスキームの最適融合とVLSI実装

研究課題名(英文)Optimum merging and VLSI implementation of clocking schemes for a next generation ubiquitous processor

### 研究代表者

深瀬 政秋 (FUKASE, Masaaki)

弘前大学・理工学研究科・教授

研究者番号:10125643

交付決定額(研究期間全体):(直接経費) 4,100,000円

研究成果の概要(和文):次世代型ユビキタスプロセッサの開発に重要なウェーブ化MFU、スキャンテスト、ゲーテッドクロックの最適融合手法を確立した。この手法で、 $0.18~\mu\,m$  CMOS  $7.5\times5~mm$ 角チップのHCgorillaを試作した。チップ仕様は200 MHz、0.13~GIPS、0.1~0.2~GOPS、200 mW である。試作チップをLSI評価ボードに組み込んだプロトタイプ送受信システムで、標準画像データベースのPepper.bmpから切り取った1149byteの画像に対して、浮動小数点演算のスペクトラム拡散ルーチンと暗号、復号ルーチンの並列実行を行わせた。これにより、HCgorillaの適性を示した。

研究成果の概要(英文): We have developed the optimum merging technique of clocking schemes composed of a waved MFU, regular pipeline, scan test, and gated clocking. By using this method, we have improvement a ubiquitous processor, HCgorilla. The improved HCgorilla has been implemented in a 0.18  $\mu$ m standard cell CMOS 7.5 mm × 5 mm chip. The chip specification is as follows. The clock speed is 200 MHz. The arithmetic throughput is 0.13 GIPS. The cipher throughput is between 0.1 and 0.2 GOPS. The power dissipation is 200 mW

We have made a PC communication system by using two LSI evaluation boards, each of which mounted an HCgorilla chip. The transmitting HCgorilla chip runs a spread spectrum routine and a cipher routine in parallel for a 1,149-byte image derived from a standard image, Pepper.bmp. Similarly, the recipient chip runs a inverse spread spectrum routine and encryption routine. The experimental result of this system has shown the practical aptitude of the HCgorilla chip for ubiquitous environments.

研究分野: 総合領域

キーワード: クロックスキーム ウェーブパイプライン SoC ユビキタスプロセッサ HCgorilla チップ メディアパイプライン サイファーパイプライン

### 1.研究開始当初の背景

- (1) VLSI の研究開発傾向は、ユビキタスと組込みとSoCである。ユビキタス化の多くはSoCの組込みで支えられ、ユビキタス化の特質である分散性や遍在性の実現にはSoCの省電力高性能化が必要である。従って、次世代型のユビキタス用プロセッサの開発では、ユビキタス化とSoC 化の統一的な推進が重要である。申請者は SoC 型のユビキタスプロセッサHCgorilla を独自に開発したが、そのハードウェア仕様は市場のモバイルプロセッサと同等レベルに止まっていた。

- (2) HCgorilla のハードウェア仕様の抜本的 改良には、以下の観点からクロック供給の最適化が重要である。即ち、スループットの主要因子は並列度とクロックスピードで、クロックスピードは CMOS セルのダイナミック電力に比例する。クロックスピードを律速するのはパイプラインで、クロック供給先のパイプラインレジスタはスキャン方式のテストやゲーテッドクロックに併用される。

#### 2.研究の目的

- (1) クロックはユビキタス化の特質である分散性や遍在性の実現に必要な高スループットと省エネの両立の主要因子である。ハードウェア設計の要であるクロックスキームの最適融合手法を開発して、次世代型ユビキタスプロセッサを飛躍的に改良する。

- (2) VLSI プロセッサのクロックスキームとして開発設計の RTL から配線の全工程をカバーし、通常方式のパイプラインとウェーブパイプライン、スキャンテスト、ゲーテッドクロックなどを最適に融合する。

- (3) 開発したクロックスキーム融合技術をユビキタスプロセッサ HCgorilla の大面積チップに実装する。使用プロセスは 0.18 μm CMOS スタンダードセル方式である。最先端のnm プロセスを用いた場合のハードウェア仕様も検討する。試作チップの基本性能を評価し、ユビキタスアプリケーションの基本ルーチンを走らせて総合的な評価を行う。

#### 3.研究の方法

- (1) 通常の CAD には備わっていないウェーブパイプラインの設計手法を確立し、ウェーブ化 MFU を設計する。実行段のウェーブ化 MFUと通常パイプライン、スキャンテスト、ゲーテッドクロッキングからなる多重のクロックスキームを RTL 設計で最適融合し、ローカルクロックを発生させる手法を確立する。

- (2) クロックスキーム融合技術を HCgorilla に実装するが、サイファーパイプはサイド攻撃に晒さないためにスキャンテストを適用しない。GIPS 値を上げるため、メディアパイプの演算実行段は並列化する。

(3) HCgorilla を  $0.18~\mu m$  CMOS  $7.5\times5~mm$  角チップで試作する。チップの評価検証には LSI 評価ボード PowerMedusa を用いる。 Synopsys 社の VCS を実行する PC を含めて必要な測定環境を整える。画像処理などで頻出する浮動小数点演算ルーチンと暗号復号ルーチンを作成し、実行条件としてクロックスピード、コア電圧、演算データを変えながら、評価検証を行う。

#### 4.研究成果

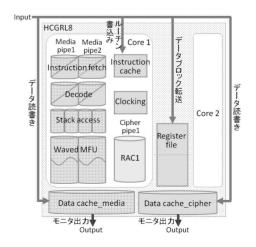

(1) ウェーブパイプラインの設計手法は通常の CAD には備わっていないので、専用のチューニングバッファを開発し、ライブラリへの取り込み、ウェーブ化 MFU を設計した。開発したクロックスキームを図1に示す。実行段のウェーブ化 MFU と通常パイプライン、スキャンテスト、ゲーテッドクロッキングからなる多重のクロックスキームを RTL 設計で最適融合する。クロックスキームを導入した HCgorilla の構造を図2に示す。

図1 クロックスキーム

図 2 図 1 のクロックスキームを導入した HCgorilla の構造

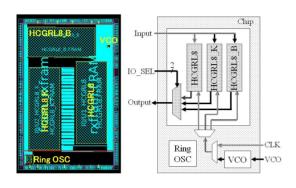

(2) 0.18 µm CMOS 7.4×7.4 mm 角チップで図3に示す HCgorilla チップを試作した。リングオシレータ Ring OSC と HCgorilla の3つのバージョン HCGRL8、HCGRL8\_K、HCGRL8\_Bは、開発したチューニングバッファのウェーブ化に対する効果を確認するために用意した。電圧制御発振器 VCO は内蔵クロックで、パッケージの周波数限界の対処策である。

図 3 HCgorilla 試作チップ

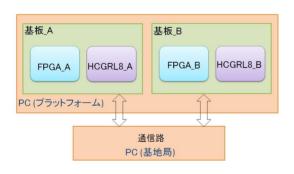

(3) 図 3 に示した HCGRL8 の仕様は、クロックスピードが 200 MHz、演算処理性能が 0.13 GIPS、暗号処理性能は 0.1~0.2 GOPS、消費電力は 200 mW である。図 4 に、HCGRL8 を組み込んだ通信機器システムを示す。標準画像データベースの Pepper.bmp から切り取った1149byte の画像に対して、メディアパイプラインによる浮動小数点演算ルーチンとしてスペクトラム拡散と、サイファーパイプラインによる暗号化復号化の並行動作を行わせた。これにより、HCgorilla チップのユビキタス空間におけるマルチメディアモバイル通信への適応力を示した。

図 4 HCgorilla 組込み型通信機器のプロト タイピング

## 5.主な発表論文等 (研究代表者、研究分担者及び連携研究者に は下線)

### [雑誌論文](計15件)

<u>Masa-aki Fukase</u> and Tomoaki Sato、 Double Cipher Implementation in a Ubiquitous Processor Chip、American Journal of Computer Architecture、査 読有、1 巻、2012、6-11

DOI:10.5923/j.ajca.20120101.02

Masa-aki Fukase 他 6 名、Development of a Next Generation Ubiquitous Processor Chip、ECTI-CIT Trans.、査読有、6 巻、 2012、120-127

http://www.ecti-thailand.org/assets/papers/1295\_pub\_50.pdf

Atsushi Kurokawa, Tatsuya Takaki, and <u>Masa-aki Fukase</u>、Efficient Delay Cells for Wave Pipelined Multifunctional Unit、Proc. of SASIMI、查読有、2012、121-126

Masa-aki Fukase 他 5 名、VLSI Implementation With Double Cipher and Media Processing for Ad-Hoc Network、Proc. of ECTI-CON、查読有、2012、1162-1-1162-4

DOI:10.1109/ECTICon.2012.6254204 <u>Masa-aki Fukase</u>, Atsushi Kurokawa, Kouhei Ichinohe, and Tatsuya Takaki、 Optimum Design of the Execution Stage of Embedded Processors、Proc. of ISCIT、 查読有、2012、538-542

DOI:10.1109/ISCIT.2012.6380957 <u>Masa-aki Fukase</u>、 A Ubiquitous Processor Embedded With Progressive Cipher Pipelines、International Jour. of Multimedia Technology、3 巻、2013、 査読有、31-37

http://www.vkingpub.com/VkUpload/201 406191104129111.pdf

Masa-aki Fukase、VLSI Implementation With Double Cipher and Media Processing for Ad-Hoc Network、ECTI-CIT Trans.、査読有、1 巻、2013、8-14

http://www.ecti-thailand.org/assets/papers/1319\_pub\_54.pdf

Atsushi Kurokawa, Masayuki Watanabe, Makoto Hoshi, and <u>Masa-aki Fukase</u>、Reasonable Circuit Analysis Considering Comprehensively Reliability and Variability、査読有、2013、282-287

DOI:10.1109/ISCIT.2013.6645865

Masa-aki Fukase and Kohta Okamoto、An Interactive Rewards Card System Embedded in Smart phones and a Cloud Server、Proc. of GCCE 2013、查読有、

2013、273-274 DOI:10.1109/GCCE.2013.6664823

Atsushi Kurokawa, Masayuki Watanabe, Makoto Hoshi, Tetsuya Kobayashi, Masa-aki Fukase、Analysis of Corner Conditions in PVT Variations and Reliability degradations、Proc. of SASIMI 2013、查読有、2013、304-309 Masa-aki Fukase、Design of the Optimum

Execution Stage of Embedded Processors、ECTI-CIT Trans., 查読有、8 巻、2014、104-112

http://www.ecti-thailand.org/assets/papers/1405 pub 64.pdf

Nanako Niioka, Masayuki Watanabe, Rosely Karel, Tetsuya Kobayashi, Masashi Imai, <u>Masa-aki Fukase</u>, and Atsushi Kurokawa、Impact of On-Chip Interconnects on Vertical Signal Propagation in 3D ICs、Proc. of APCCAS、查読有、2014、607-610

DOI:10.1109/APCCAS.2014.7032854

Masayuki Watanabe, Rosely Karel,

Nanako Niioka, Tetsuya Kobayashi,

Masa-aki Fukase, Masashi Imai, Atsushi

Kurokawa、Effect of Substrate Contacts

on Reducing Crosstalk Noise between

TSVs、Proc. of APCCAS、查読有、2014、

DOI:10.1109/APCCAS.2014.7032893 Masayuki Watanabe, <u>Masa-aki Fukase</u>, Masashi Imai, Nanako Niioka, Tetsuya Kobayashi, Rosely Karel, Atsushi Modeling of Substrate Kurokawa 、 Contacts in TSV-based 3D ICs, Proc. of 3DIC、查読有、2014、P12-1-P12-4 Masayuki Watanabe, Nanako Niioka, Masa-aki Fukase, Masashi Imai, Tetsuya Kobayashi, and Atsushi Kurokawa, An Effective Mode I for Evaluating Vertical Propagation Delav in TSV-based 3-D ICs、Proc. of ISQED 2015、 査読有、2014、519-523

### [学会発表](計23件)

763-766

一戸康平、成田一貴、三村直道、高木竜 也、黒川敦、佐藤友暁、深瀬政秋、ユビ キタスプロセッサのトレードオフ設計、 電気学会電子・情報・システム部門大会 講演論文集、2012 9月5日、弘前 高木竜哉、深瀬政秋、黒川敦、低コスト・ 高品質な遅延セルの開発、電気学会電 子・情報・システム部門大会講演論文集、 2012 9月5日、弘前 成田一貴、三村直道、高木竜哉、一戸康 平、深瀬政秋、佐藤友暁、ユビキタスプ ロセッサのクロックスキーム融合、電気 学会電子・情報・システム部門大会講演 論文集、2012 9月5日、弘前 三村直道、高木竜哉、成田一貴、一戸康 平、黒川敦、佐藤友暁、深瀬政秋、ユビ キタスプロセッサチップの最適設計電気 学会電子・情報・システム部門大会講演 論文集、2012 9月5日、弘前 宫森博也、今井雅、黒川敦、深瀬政秋、 内蔵型クロック回路の開発、電子情報通 信学会総合大会論文集、2013年3月19 日、岐阜 深瀬政秋、成田一貴、三村直道、高木竜

哉、宮森博也、黒川敦、今井雅、ユビキ タスプロセッサ HCgorilla.8、平成 25 年 度東京大学大規模集積システム設計教育 研究センター年報、2013 8 月

小田桐舞央、今井雅、黒川敦、<u>深瀬政秋</u>、 可変クロック方式の開発、平成 25 年度電 気関係学会東北支部連合大会、2013 8 月 22 日、会津

深瀬政秋、小田桐舞央、可変クロック方 式ウェーブ化 MFU の開発、電気学会電 子・情報・システム部門大会講演論文集、 2013 9月5日、北見

星誠、渡邊眞之、小林徹哉、<u>深瀬政秋</u>、 黒川敦、微細 LSI におけるリーク電流が 回路遅延に与える影響、電気学会電子・ 情報・システム部門大会講演論文集、2013 9月5日、北見

星誠、渡邊眞之、小林徹哉、<u>深瀬政秋</u>、 黒川敦、次世代 LSI 用微細 CMOSFET の特 性解析、電気学会電子・情報・システム 部門大会講演論文集、2013 9 月 4 日、北 見

岡本康太、<u>深瀬政秋</u>、スマートフォンと クラウドサーバーを用いたポイントカー ドシステムの開発、FIT 2013、2013 9月 5日、鳥取

小田桐舞央、<u>深瀬政秋</u>、可変クロック方 式プロセッサの HW/SW 協調設計、電子情 報通信学会総合大会、2014 3 月 19 日、 新潟

一戸康平、<u>深瀬政秋</u>、ユビキタスプロセッサ HCgorilla の post-Si validation、電子情報通信学会総合大会、2014 3 月 19日、新潟

小田桐舞央、<u>深瀬政秋</u>、信頼性とエネルギー効率の両立のための可変クロック方式、LSI とシステムのワークショップ2014、2014 5月26日、北九州

Nanako Niioka, Masashi Imai, <u>Masa-aki</u> <u>Fukase</u>, Rosely Karel, Tetsuya Kobayashi, Atsushi Kurokawa、Modeling and Analysis of Vertical Interconnects in 3D ICs、平成 26 年度電気関係学会東北支部連合大会、2014 8月21日、米沢 Rosely Karel, <u>Masa-aki Fukase</u>, Masashi Imai, Nanako Niioka, Tetsuya Kobayashi, Atsushi Kurokawa、Substrate Contact Effect on TSV-to-TSV Coupling、平成26 年度電気関係学会東北支部連合大会、2014 8月21日、米沢

小田桐舞央、<u>深瀬政秋</u>、可変クロック方 式ユビキタスプロセッサのゲートレベル 評価、平成 26 年度電気関係学会東北支部 連合大会、2014 8月 22 日、米沢

深瀬政秋、一戸康平、黒川敦、ユビキタスプロセッサチップの評価電気学会電子・情報・システム部門大会、2014 9月3日、松江

小田桐舞央、<u>深瀬政秋</u>、ユビキタスプロセッサの低電力高効率高信頼性設計、電

気学会電子・情報・システム部門大会、 2014 9月3日、松江

小林徹哉、新岡七奈子、<u>深瀬政秋</u>、黒川 敦、インダクタンス逆行列を用いた三次 元集積回路の貫通シリコンビア間結合容 量抽出、電気学会電子・情報・システム 部門大会、2014 9月3日、松江

- 21 小田桐舞央、<u>深瀬政秋</u>、可変クロック方式プロセッサへのクロックゲーティング適用に関する研究、電子情報通信学会総合大会、2015 3 月 10 日、草津

- 22 小林徹哉、今井雅、<u>深瀬政秋</u>、新岡七奈 子、黒川敦、ウィンドウベース L 逆行列 による TSV 間容量抽出、電子情報通信学 会総合大会、2015 3月 13日、草津

- 23 星誠、<u>深瀬政秋</u>、今井雅、黒川敦、高効 率遅延セルの実測による性能評価、電子 情報通信学会総合大会、2015 3 月 13 日、 草津

#### [図書](計2件)

小島正典、<u>深瀬政秋</u>、山田圀、共立出版、 デジタル技術とマイクロプロセッサ、 2012、217

Masa-aki Fukase. In tech. Theory and Practice of Cryptography and Network Security Protocols and Technologies. 2013. 26

### 〔産業財産権〕

出願状況(計 件)

名称: 発明者: 権利者: 種類: 番号:

出願年月日: 国内外の別:

取得状況(計件)

名称: 発明者: 権利者: 種類: 番号: 出願年月日

出願年月日: 取得年月日: 国内外の別:

#### 〔その他〕

ホームページ等

http://hue2.jm.hirosaki-u.ac.jp/html/58 4\_ja.html

### 6. 研究組織

(1)研究代表者

深瀬 政秋 (FUKASE MASAAKI) 弘前大学・大学院理工学研究科・教授 研究者番号:10125643

(2)研究分担者

( )

研究者番号:

(3)連携研究者

( )

研究者番号: