#### 科学研究費助成專業 研究成果報告書

平成 27 年 6 月 8 日現在

機関番号: 16101 研究種目: 基盤研究(C) 研究期間: 2012~2014

課題番号: 24500067

研究課題名(和文)遅延付加・検出回路を組み込んだ遅延故障検査容易化回路の設計と評価

研究課題名(英文) Design and evaluation of design-for-testability circuits for delay faults using built-in time-to-digital converter

研究代表者

四柳 浩之(Yotsuyanagi, Hiroyuki)

徳島大学・ソシオテクノサイエンス研究部・准教授

研究者番号:90304550

交付決定額(研究期間全体):(直接経費) 3,800,000円

研究成果の概要(和文):LSIの高集積化にともない,信号線のショートやオープンの欠陥による遅延故障を検査することが高品質な検査を行うために重要となっている。本研究では,LSIチップ内部およびLSIチップ間接続で発生する遅延故障を検出するための検査容易化回路として,遷移信号の遅延時間を観測可能な遅延付加・検出回路をチップ内部に組み込む手法を提案し,シミュレーションがよびIC試作による故障検出能力評価を行った。開発した検査を見ておける。 ニーーこう、にこれでは、アイコン・スコンのある「None IPIC なる) Riper は出まり計画で行った。 開発した映直谷気化設計手法による複数経路の同時検査可能性や,試作ICにおける故障判定可能な遅延欠陥サイズの推定を行い,微小遅延故障の検査が可能であることを明らかにした。

研究成果の概要(英文): Testing delay faults caused by defects like opens and shorts is more important to ensure test quality in recent highly integrated circuits. In this research, we propose design-for-testability circuits for detecting delay faults in both inside of LSI chips and interconnection between chips. The proposed design embeds a time-to-digital converter into a chip that can observe the delay of transition signals. We evaluate feasibility to detect delay faults by the proposed design using simulation and the experimental ICs. The condition for testing delays of two or more paths and the size of detectable delay faults are also evaluated to show the effectiveness of the proposed method.

研究分野: 総合領域

キーワード: VLSIの検査技術 検査容易化設計 遅延故障 テスト生成 VLSI ディペンダブル・コンピューティング LSIテスト

LSIテスト

## 1.研究開始当初の背景

LSI の高集積化にともない,信号線のショ ートやオープンの欠陥により回路の遅延時 間がわずかに増加する遅延故障が問題とな っている。一般に遅延故障のテストでは信号 の伝搬経路(パス)を考慮して検査入力を生 成し,回路動作に影響する長いパス上の信号 遅延がクロック周期内に収まるか否かを判 定する。被検査回路(CUT)内部の最長パス遅 延時間を測定する手法として CUT の入力信 号と出力信号の差分を測定する手法や、 CUT と測定系の遅延時間との差分を測定す る手法などが提案されていた。これらの手法 は LSI 内部の遅延を測定するものであるが, 一方, 近年 SiP(System in package) や 3 次元 実装 IC などの複数チップを一つのパッケー ジ内に実装する技術の利用が進んでおり,チ ップ間接続における故障による異常遅延の 検査も新たな課題となっていた。

### 2.研究の目的

本研究では,LSI チップ内部および LSI チップ間接続で発生する遅延故障を検出するための検査容易化回路の設計および検出まり評価を行う。被検査チップの信号遷移を複数のタイミングで観測可能な遅延付加・検出回路をチップ内部に組み込んだ検査容易検出について,(1) 遅延付加回路に基づく多の削減および故障検出能力向上のための制減および故障検出能力向上のための制御回路の設計,(3)遅延故障検出用検査入力生成手法の開発,(4)シミュレーションおよびIC 試作による故障検出能力評価,の4つについて研究を行う。

### 3.研究の方法

(1) 遅延付加回路に基づく遅延故障検出条件の設定・評価

遅延検出回路とバウンダリスキャン回路のフリップフロップ(FF)を共用化する検査容易化回路を含む IC の設計・試作を行った。テスト時の制御入力印加のタイミングやテストデータ量なども検討しながら設計の修正を行い、また、試作 IC における信号遅延のばらつきの影響を評価し、遅延検出回路中の遅延付加ゲートの選定や遅延故障検出条件の設定を行った。

## (2) 検査データの削減および故障検出能力向上のための制御回路の設計

遅延検出回路を組み込んだ検査容易化回路において、複数パスの信号遷移を遅延付加ゲートである XOR ゲートで重ねあわせて観測する際の故障検出条件および制御信号の設定についての検討を行った。複数パスを一度に検査することで検査データの削減が見込まれるが、信号の重ね合わせによる故障の見逃しが起こる可能性もある。複数パスの同時検査が可能なパスの条件や検査入力、制御信号の条件を考察し、制御回路の設計に反映さ

せる。まずは、複数パスのうち、1つのパスのみに遷移が発生する条件のもとでの故障検出能力評価および検査データ量の評価を行い、さらに観測する複数パスのうち、2つ以上で遷移が発生する場合でも検査可能とするための回路変更、検査入力生成などの手法を開発する。

## (3) 遅延故障検出用検査容易化回路による 検査入力生成手法の開発

商用ツールなどにより遅延故障検出用テスト入力の生成が可能であるが,本テスト容易化設計を適用した回路に対する検査入力の生成および制御信号の生成手順の開発が必要である。また,本テスト容易化回路により検出される遅延故障の遅延サイズの評価,および故障検出能力評価を行う。

## (4) シミュレーションおよび IC 試作による 故障検出能力評価

遅延故障検出用テスト容易化回路を実装した CMOS 0.18  $\mu$ m IC 試作を東京大学大規模集積システム設計教育研究センター(VDEC)の試作サービスを用いて行った。遅延測定回路における遅延時間のばらつきなどの評価を行い,設計時のシミュレーションとの比較等を行った。

### 4. 研究成果

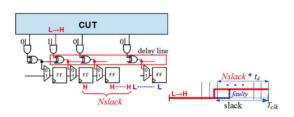

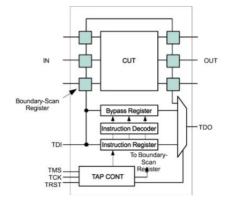

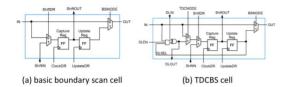

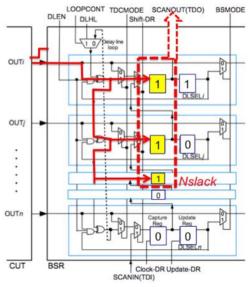

本研究では,タイムデジタイザ回路 (Time-to-digital converter; TDC)を検査 対象回路に組み込み遅延故障の検査容易化 回路として用いる手法を開発した。図1にタ イムデジタイザによる遅延計測の原理を示 す。検査対象の CUT 出力信号を選択し、遅延 付加ゲート(XOR)で構成される遅延付加部に 伝搬させ,遅延させた信号をフリップフロッ プでキャプチャすることでタイミング余裕 時間の計測を行う。TDC を検査容易化設計で 用いられている図2のバウンダリスキャン 回路に併合することで新たな検査容易化設 計回路を提案した。図3(a)の基本バウンダ リスキャンセルを図3(b)の開発した TDCBS セルに置き換えることで,遅延検出が可能と なる。セル内部の FF を TDC の制御・観測部 にも併用することで面積オーバヘッドを抑 えている。TDCBS セルを用いて図1と等価な 遅延計測回路が図4で示すように構成され, 遅延故障検査が可能である。

図1 タイムデジタイザ(TDC)による遅延計測

図2 バウンダリスキャン回路

図3 バウンダリスキャンセル

図4 TDCBS 回路による遅延検査

各研究方法によって得られた成果は次のとおりである。各成果は研究期間中に設計した3種の試作 IC の測定およびシミュレーションにより得られたものである。

(1) 遅延付加回路に基づく遅延故障検出条件の設定・評価

提案した遅延付加・検出回路を実装したICを試作し、製造ばらつきの影響が遅延延付加ゲートに及ぼす影響を観測し、より精度のの近近量の補正を見りである場合のの遅延量の補正を見り行うを観測により行う手法を表すとなる信号を印加する場合、2つの大力を開からである場合の3種を比較し、検口査を用いる場合が最も高いた場合が最も高いた場合が最も高いた場合が最も高いた場合が最も高いた場合が最も高いた場合が最も高いた場合が最も高いた場合が最も高いた。IC設計に用いる静的タイミン遅延析ツールにより検査対象回路に応じ解析の部で必要とされる付加遅延量を概算す

る手法を提案した。これにより必要な付加遅延ゲートの数が求められ,提案手法の適用時の面積オーバヘッドの最適化に有効である。

# (2) 検査データの削減および故障検出能力向上のための制御回路の設計

検査コストを低減するため複数経路の同時観測を行うための条件を検討した。信号遷移時に発生するグリッチの影響も考慮して観測対象のTDCBSセル間段数と遅延付加ゲートの遅延量,およびタイミング余裕が満たすべき条件を明らかにした。 遅延量の評価を簡易にするためのタイミング余裕計測回路の設計を行った。 検査用クロックが低速の場合に実速度検査を行うためのキャプチャ用信号生成回路の設計を行った。

## (3) 遅延故障検出用検査容易化回路による 検査入力生成手法の開発

従来用いられている遷移遅延故障用の検査入力生成ツールを基に、検査入力の生成を行い、提案した検査容易化設計におけるバウンダリスキャン回路の制御系列への変換手順を確立した。また、検査入力生成を試作ICに対して適用し、タイミング余裕の計測が可能であることを確認した。

## (4) シミュレーションおよび IC 試作による 故障検出能力評価

チップ間ばらつきの影響を踏まえて,遅延付加ゲートのゲート遅延値と検出可能な遅延故障サイズの概算を試作 IC の測定結果を基に行った。 チップ内の遅延付加ゲート個別の遅延量の差異による遅延測定への影響を試作 IC により評価し,さらに遅延付加部の遅延量の補正により故障判定可能な遅延欠陥サイズを縮小した。

これ以外に,遅延付加・検出回路をバウンダリスキャン回路に限定せず任意の FF 間の遅延故障検査を行うための FF の検査容易化として,バウンダリスキャン回路と同様に FFに TDC 回路を組み込む手法を検討・設計を行った。また,シリコン貫通ビア(TSV)を用いる3次元実装 IC へ提案の遅延付加・検出回路を適用するため TSV への遷移信号供給可能な TDCBS セルの改良を施した検査容易化設計手法の提案も行なった。

### 5 . 主な発表論文等

### 〔雑誌論文〕(計1件)

H. Yotsuyanagi, H. Makimoto, T. Nimiya, M. Hashizume, "On Detecting Delay Faults Using Time-to-Digital Converter Embedded in Boundary Scan," IEICE Trans. on Information & Systems, 查読有, vol. E96-D, no.9, 2013, pp. 1986 - 1993.

DOI: 10.1587/transinf.E96.D.1986

## [学会発表](計15件)

"Design-for-H. Yotsuyanagi, testability circuit for delay faults in sequential circuits," 2015 Kyutech, UT, and Taiwan Tech Joint Workshop on Advanced VLSI Design Technologies, 2015 年3月5日,台湾科技大学(台北,台湾) H. Yotsuyanagi, H. Sakurai, M. Hashizume, "Delay Line Embedded in Boundary Scan Testina TSVs." Fifth International Workshop on Testina Three-Dimensional Stacked Integrated Circuits, 2014年10月24日, Washington State Convention Center (シアトル,ア メリカ合衆国)

櫻井 浩希, 四柳 浩之, 橋爪 正樹, "TDC 組込み型バウンダリスキャン回路を用いた実測によるタイミング余裕の検証,"電子情報通信学会ソサイエティ大会講演論文集,p.46,2014年9月23日,徳島大学(徳島県徳島市)

濱田 圭吾, 四柳 浩之, 橋爪 正樹, "遅延 故障検査容易化設計用タイミング余裕計 測回路の提案,"電気関係学会四国支部 連合大会講演論文集, p.112, 2014 年 9 月 13 日, 徳島大学(徳島県徳島市)

石場 隆之, 四柳 浩之, 橋爪 正樹, "順序 回路におけるパスの微小遅延故障を測定 する遅延付加回路設計,"電気関係学会 四国支部連合大会講演論文集, p.111, 2014年9月13日, 徳島大学(徳島県徳島 市)

櫻井 浩希, 四柳 浩之, 橋爪 正樹, "TDC 組込み型バウンダリスキャン回路による遅延検出能力評価," 電子情報通信学会技術研究報告(ディペンダブルコンピューティング研究会), vol. 113, no. 430, pp. 7-12, 2014年2月10日,機械振興会館(東京都港区)

池地 大輔, 四柳 浩之, 橋爪 正樹, "遅延 故障検査容易化回路を用いた 複数経路 の同時検査可能性調査,"電気関係学会 四国支部連合大会講演論文集,p.105, 2013年9月21日, 徳島大学(徳島県徳島 市)

二宮 孝暢, 四柳 浩之, 橋爪 正樹, "TDC 組込み型バウンダリスキャンを用いる製造ばらつきを考慮した遅延故障検査法,"電気関係学会四国支部連合大会講演論文集,p.106,2013年9月21日, 徳島大学(徳島県徳島市)

中村 真規, 四柳 浩之, 橋爪 正樹, "隣接 TSV を考慮した TSV 遅延故障検出法につい て," 電子情報通信学会技術研究報告(ディペンダブルコンピューティング研究会), vol. 112, no. 429, pp. 31-36, 2013 年 2 月 13 日,機械振興会館(東京都港区) 池地 大輔, 四柳 浩之, 橋爪 正樹, "遅延 故障検査容易化設計における STA を用 いる必要付加遅延量の導出," 電気関係 学会四国支部連合大会講演論文集, p.106, 2012 年 9 月 29 日, 四国電力株式会社総合研修所(香川県高松市)

### 6.研究組織

### (1)研究代表者

四柳 浩之 (Hi royuki Yotsuyanagi) 徳島大学・大学院ソシオテクノサイエンス 研究部・准教授

研究者番号:90304550