# 科学研究費助成事業 研究成果報告書

平成 27 年 6 月 15 日現在

機関番号: 13201 研究種目: 基盤研究(C) 研究期間: 2012~2014

課題番号: 24560326

研究課題名(和文)LCフィルタレス単相13レベルインバータの超高効率化

研究課題名(英文) Superior High Efficiency for a Single Phase 13 Level Inverter without using a LC

Filter

研究代表者

飴井 賢治 (Amei, Kenji)

富山大学・大学院理工学研究部(工学)・講師

研究者番号:50262499

交付決定額(研究期間全体):(直接経費) 4,100,000円

研究成果の概要(和文): 本研究の目的は、LCフィルタを用いずに高効率と低歪みを両立できる新しいインバータ回路を構築することである。この回路はPWM制御を用いずに複数の電圧レベルから所望の電位を選択して電圧を出力する。オン抵抗の小さな素子の選定により効率改善を図り、4素子1ユニット構成の基板により拡張性を高めた。また、遅延のない動作を実現する制御方式を検討した。これらの改良を施し3レベルの基本回路で実験を行い、高効率と正確な動作を確認した。これを13レベルまで拡張し、良好な動作特性を検証した。さらにスイッチング動作の見直しを図り、従来のインバータを凌駕する98.5%の高効率と約3%の波形歪みを達成した。

研究成果の概要(英文): A purpose of this research is to create the new inverter circuit which can realize both high efficiency and low distortion without using LC filter. This circuit selects desired electric potential from the several voltage levels and outputs voltage without using a PWM control. Improvement of the efficiency was attempted by the selection of the element of the low on-resistance, and extensibility was raised by a circuit-board composed of 4 elements per 1 unit. In addition, it was considered a control method to realize accurate operation. The experiment was carried out in the basic circuit of 3 levels, and high efficiency and operation without the delay were confirmed. It was expanded to 13 levels, and a superior characteristic of the operation was inspected. Furthermore, a review of the switching operation was carried out, and 98.5% of high efficiency to exceed a conventional inverter and approximately 3% of waveform distortion were accomplished.

研究分野: パワーエレクトロニクス

キーワード: マルチレベルインバータ 双方向スイッチ LCフィルタレス PWM制御レス 高効率 低歪み ディジタ

ル制御

### 1.研究開始当初の背景

マルチレベルインバータは、原理的に複数の電源と切り替えスイッチで構成され、負荷に印加する電圧を複数の電圧レベルから自由に選択することができる回路である。階段状の擬似正弦波を生成することができ、スイッチングを行うことなしに出力電圧の調波成分を低減することができ、スイッが損失や高周波障害を回避することがある。1素子あたりの電圧負担が小さくなといら、中性点クランプ型(以下、NPCと略す)のマルチレベルインバータ回路がに実けれている。

マルチレベルインバータの最大の問題は、複数の電源と多くのスイッチング素子を必要とすることである。マルチレベルインバータの原理を実際の半導体スイッチを用いてNPC型で構成すると、2m個の電源に対し4m個のスイッチが必要であり、出力される電圧レベルは正負合わせて(2m+1)レベルである。

PWM制御を用いないで出力電圧の歪み率を3%以下に抑制するためには、正負合わせて13レベル以上が必要であると報告されており、その場合24個の素子が必要になる。しNPC型の回路構成を拡張して多段化する良化する大変であるとする。となり表子数が増え、素子の電圧降下が積に実用化されている三相マルチレベルがしたの電圧レベル数は、3レベル(線を補い、バータの電圧レベル数は、3レベル(線を補い、1と少なく、波形制御性をない、ためにパルス幅変調を適用せざるを得の低が上で5レベル)と少なく、波形制御性をない。ことはつまり、スイッチング損失の低減や高周波障害の抑制といった本来持つである。

#### 2.研究の目的

本研究の目的は、パルス幅変調を行わずに 電圧レベルの多段化によって、従来を上回る 高効率、低歪みの直流/交流変換回路を開発す ることである。従来の回路を拡張した中性点 クランプ型マルチレベルインバータの場合、 複数の素子が直列接続された構成となり、そ れらの素子を流れる電流によって生じる導 通損が積算され効率の低下が避けられない。 そこで本提案では、双方向スイッチを用いた 新しい回路構成を提案し、導通損とスイッチ ング損失の低減を図る。そして電圧歪みの低 減と電圧誤差の最小化を両立する最適スイ ッチング位相を導出し、電圧制御を確立させ る。また、6 つの直流電源電圧を不均一に制 御して出力電圧歪みのさらなる低減を図る。 最高効率のインバータ回路を目指す。

#### 3.研究の方法

(1)主回路の安定動作の確立、電圧歪を抑制するための回路解析

電圧歪みを抑制にする回路動作の実現

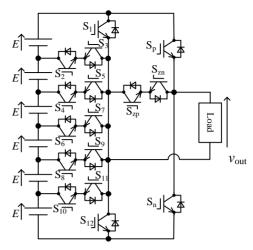

図 1 単相 13 レベルインバータ

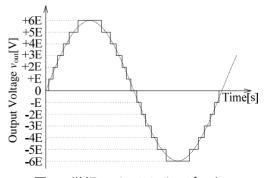

提案する単相13レベルインバータ回路を 図1に示す。本回路は16個のスイッチング切り 替えることで6個の電源から所望の電圧レベルを選択して図2に示すような階段状に出り 電圧を生成する。スイッチの切り替えに出り 13レベルの電位を出力することができる。 けいではいり替えのタイミングによって組みで 電圧を短絡させ素子を破壊させたり、あるい はスイッチの切り替えの際に回路が開放に はスイッチの切り替えの際に回路が開放に なって予期せぬ電圧レベルを出力させたり といった問題が生じる。

そこで、まずはスイッチングモードを詳細に調べ制御方式の見直しを行い、シミュレーションによって回路動作の確認を行う。概略的な動作確認のシミュレーションにはPSIMを用いて行い、特にサージ電圧の発生などの過渡的な動作の確認には、PSpiceを用いて行う。デッドタイムの挿入やスイッチの切り替えタイミングの最適化によって安定動作の実現と電圧歪の抑制を図る。得られた結果を基にインバータ回路を作製する。

小形化を考慮した主回路・制御回路の製作図1に示すように、提案回路は複数のスイッチング素子を用いるため、従来のHブリッジ回路に比べ小形化が困難であることは否

図 2 単相 13 レベルインバータの 出力電圧波形

めない。そこで、計 16 個のスイッチング素子のうち4素子をHブリッジモジュールで構成し、主回路の小形化を試みる。また、双方向スイッチ部に関しては、エミッタコモンで接続することによってドライブ電源を共通化し、電源数の削減を図る。主回路素子による損失発生を抑えるため、飽和電圧の低いIGBT やオン抵抗の小さな FET の中から厳選して使用する。ゲート回路は、シミュレーションの理想状態に近づけるため、信号の遅延時間が均一になるよう考慮して設計・製作する。

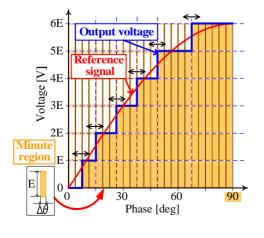

## (2)スイッチング位相の最適化

単相13レベルインバータ回路の出力電圧 波形の生成方法、及びその最適化について検 討する。図3は、電源電圧が均一時における 出力電圧の生成過程を示す。出力電圧は6段 に積層された電圧レベルで構成されており、 各段の電圧を切り替える位相、すなわちスイッチング位相によって波形を構成し制御を 行う。各電圧レベルの横軸を微小位相  $\theta$ 、縦軸を一定電圧Eで区切り、それによって作る れる微小領域をつなぎ合わせて各段の電圧 レベルを構成する。これにより、波形の最適 化が数値解析によって行えるようになる。

#### 電源電圧が均一時の出力電圧の最適化

図 3 出力電圧波形の生成過程 (6電源電圧=均一時)

の導出を行う。得られた結果を基に実験を行い、波形制御性を検証する。

### 4. 研究成果

本研究の目的は、LC フィルタを用いずに低ひずみ化を実現する高効率インバータ回路を構築することである。その目的を達成するためには、高効率化と小形化を考慮した主回路構成、複数のスイッチング素子を自由にかつ精度良く制御、波形ひずみを低減できる最適スイッチング位相の導出が重要である。これらの課題を解決する方法を考案し、実験回路を作製して特性試験を行い、改善効果を検証することが本研究の具体的内容である。

## 電圧歪みを抑制にする回路動作の実現

まず、高効率化と小形化を考慮した主回路 の構成と複数のスイッチング素子の制御に ついて検討した。どんな素子を使用すればよ いか、どのような制御回路で構成すればよい のか、そして電圧レベル数の拡張にも十分に 対応できるようにするにはどのように構成 したらよいのかについて検討した。主回路の 拡張性に関しては、回路基板をユニット化す ることで容易に拡張できる構成にした。また 複数のスイッチング素子の制御に関しては、 制御信号を I/O ポートから出力することで、 遅延無く正確に出力でき、拡張性にも対応で きることが確認された。検討した内容を評価 するために提案する方式のマルチレベルイ ンバータの基本単位である単相3レベルハー フブリッジインバータ回路を試作し、動作特 性を観測した。その結果、良好な波形制御性 と高い効率が確認された。主回路基板をユニ ット構成にすること、そして制御信号を I/O ポートから一括出力することによって、拡張 性が実現された。これらのことから、提案す る 13 レベルインバータ回路を構築する上で 基礎となる貴重な設計データが得られ、当初 の目標を十分に達成できたといえる。

小形化を考慮した主回路・制御回路の製作 高効率化と小形化に主眼を置いて設計を 行った主回路と、複数の SW 素子をマイクロ プロセッサで制御する回路を作製して特性 を評価した。まず主回路構成については、高 効率化を図るために使用するスイッチング 素子の見直しを行った。MOS-FET のオン抵 抗は高耐圧になるほど増加する傾向があり、 出力電圧値と素子耐圧を考慮してルネサス の RJK2511DPK (250V、65A、28mΩ)を選 択した。また小形化に関しては、1 枚の基板 に 4 つの SW 素子とその駆動回路を配置し、 4 素子単位で増設できるユニット構成とした。 これにより電圧レベルの増減に対応でき、ま た使用素子の違いによる動作特性への影響 を比較できるようになった。さらに、このユ ニット基板のパターンを発生させて専用基 板を作製し、回路の製作行程の短縮を図った。

制御回路に関しては、汎用的なマイクロプ

ロセッサによるディジタル制御の可能性を検討した。それは、周期が 16μs の基準クロックでタイマー割り込みを発生させ、予めプリセットされたカウンタをダウンカウントさせてボローが発生したときにゲート信号を更新する方法である。本方式の動作特性を確認するために、ルネサスの H8 / 3052 マイコンを用いて制御回路を作製した。基準クロックの生成やダウンカウント、データ保持はマイコン内部で行い、ゲート信号の出力はI/O ポートを用いて行った。

これらの装置を用いて動作特性試験を行った。出力電圧 100V、電力 700W の条件で実験を行ったところ変換効率は 97.0%、電圧歪み率は 3.47%であった。なお、この結果を学会発表し、電気学会より「ヤングエンジニアポスターコンペティション」、IEEE IAS より「Young Engineer Competition Award」を受賞した。

損失要因の抽出による更なる高効率化

回路の損失発生要因の抽出を行い更なる 高効率化を実現するため、主回路及び制御回 路の見直しを行った。主回路に関しては、13 レベルのマルチレベルインバータに加え、 PWM 制御が施された同原理の 5 レベルの回 路を作製し、動作特性の検証を行った。この 回路は、13 レベルに比べ制御が簡略になり、 主回路の違いによる損失比較をより顕著に 行うために利用した。5 レベルインバータは、 13 レベルの半分の8素子で構成され、同様に 双方向スイッチを切換えながら所望の電圧 レベルを出力する回路である。この5レベル 回路を用いて実験を行ったところ、LC フィ ルタありの時の効率は、出力電力が 730W 時 に 97.8%、LC フィルタなしの時は出力 760W 時に 98.7%であった。これに対し 13 レベルイ ンバータは、700W 時に 97.5%であり、5 レベ ルの PWM スイッチング (LC フィルタあり) と同等の効率であった。このため、スイッチ ングパルスの最適化や、主回路素子の見直し を行った結果、効率を 98.5%まで高めること ができ、5 レベルと同等の特性が得られた。 このことから、同原理で動作する回路で電圧 レベル数やスイッチング素子数の違いがあ っても、効率に影響しないことが確認された。 なお、この効率は、従来のフルブリッジ型イ ンバータを遙かに超える高い値であり、当初 の高効率化の目標が十分に達成されたと言 える。

波形制御性に関しては、LC フィルタが接続されていないため出力電力を 1,000W まで変化させても波形歪みは約 0.3%しか増加しておらず、フィードバック制御に匹敵する波形安定性が確認された。しかし、13 レベルの階段状の波形は、歪みが最小化されたスイッチングパルスを与えても 3%の歪みを含んでおり、高精度な電圧を必要とする用途には電圧レベル数の検討が必要になることが確認された。今後は、これらの結果を基に 13 レ

ベルインバータを電力系統へ接続し、高効率な系統連系インバータの実現に向けて研究を進めていく予定である。

### 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

### [雑誌論文](計 1件)

<u>飴井賢治</u>、加藤雅大、大路貴久、作井正昭、「双方向スイッチを用いた高効率単相 5 レベルインバータの特性」電気学会論文誌 D、査読あり、Vol.135、No.3、pp.321-322 (2015) DOI:10.1541/ieejias.135.320

# [学会発表](計 3件)

加藤雅大、<u>飴井賢治</u>、大路貴久、作井正昭、「双方向スイッチを用いた単相 5 レベルインバータの制御回路の簡略化」、平成 26 年度電気関係学会北陸支部連合大会、A-36 (CD) (2014.9.11)、「富山高専(富山県・富山市)」

足立成史、<u>飴井賢治</u>、大路貴久、作井正昭、「ハーフブリッジ型単相 13 レベルインバータの制御方式」、平成 26 年度電気関係学会北陸支部連合大会、A-38 (CD) (2014.9.11)、「富山高専(富山県・富山市)」

足立成史、<u>飴井賢治</u>、大路貴久、作井正昭、「ハーフブリッジ型単相3レベルインバータの試作」、平成25年度電気学会産業応用部門大会(JIASC13)、YPC、Y-39(CD)(2013.8.28)、「山口大学(山口県・山口市)」

# 6.研究組織

## (1)研究代表者

飴井 賢治 (AMEI, Kenji)

富山大学・大学院理工学研究部(工学)・ 講師

研究者番号:50262499