# 科学研究費助成事業 研究成果報告書

平成 26 年 6月12日現在

機関番号: 1 4 6 0 3 研究種目: 挑戦的萌芽研究 研究期間: 2012~2013

課題番号: 24651163

研究課題名(和文)フォトニック・システム・オン・チップ技術の開拓

研究課題名(英文)Development of photonic-system-on-chip technology

#### 研究代表者

笹川 清隆 (Sasagawa, Kiyotaka)

奈良先端科学技術大学院大学・物質創成科学研究科・助教

研究者番号:50392725

交付決定額(研究期間全体):(直接経費) 3,100,000円、(間接経費) 930,000円

研究成果の概要(和文):イメージセンサ等にモノリシックに搭載可能な集積回路プロセスの配線層を応用したオンチップ光学素子の設計・試作を行なった.オンチップ光学素子はイメージセンサ用画素上に作製された金属グレーティング構造であり,偏光分離特性・波長依存性を有する.近年の先端CMOSプロセスを用いることにより,配線層を用いた金属グレーティングピッチは可視光波長より十分小さくすることが可能である.65nmプロセスを用いて設計することにより,約100程度の消光比を得ることに成功した.

研究成果の概要(英文): On-chip photonic devices based on wiring layers of CMOS process were designed and fabricated. The devices can be monolithically integrated, for example, on images sensors. Its structure is a metal grating on an image sensor pixel, which has characteristics of polarization separation and wavel ength dependence. By using recent advanced CMOS processes, the pitches of the metal grating with wiring layers can be designed finer than visible wavelengths. In this study, the extinction ratio of approximately 100 was successfully achieved by using 65-nm process.

研究分野: 複合新領域

科研費の分科・細目: マイクロ・ナノデバイス

キーワード: マイクロセンサー マイクロ光システム イメージセンサー

### 1.研究開始当初の背景

半導体集積回路加工技術の進展に伴い、これを応用したイメージセンサの画素寸法も微細化が進み、1 μm 以下に到達している。このような微細構造においては、画素上の開口が可視光波長と同程度となり、開口の光透過率が著しく減少するなど、更なる微細化に向けての問題が顕著となっている。

### 2. 研究の目的

本研究では,半導体集積回路技術を用いてサブミクロンの光学素子をモノリシックに形成,集積化することでフォトニック・システム・オン・チップの実現を目指す.光学素子の形成には金属配線層を用い,これとイメージセンサのような光検出回路とを組み合わせることにより,波長,入射角,偏光などの情報を含んだ信号を取得し高機能化を実現する.

# 3.研究の方法

標準 CMOS プロセスによりイメージセンサの画素構造を微細化したイメージセンサを設計する.近年の,先端集積回路別ロセスによりの側えばゲート幅 65nm 等の微細な MOS トランジスタを接続するための金属配線も 100nm以で,金属配線層をがある。マイランが成らに微細なものとなってして,光線層を利用することにより,波長以スリットととにより,波長が一括製造される.金属ナノスリットととによりが一括製造される。金属ナノスリットととによりが一括製造される。金属ナノスリットととによりが一方とは、波長にも依存する。 が長検出の可能性についても検討する.

イメージセンサ試作と並行して,光学系設計のための電磁界シミュレーションを行う.スリット間の間隔によって,フォトダイオードが形成される Si 基板表面での分布パタンが変化することがわかる.試作結果との比較から精度の高いシミュレーションのためのパラメータ抽出を行い,設計へとフィードバックする.

試作画素の評価結果を基に,フォトニック システムオンチップ素子として,グレーティ ング等の微細なスリット構造を有するチップを試作する.CMOSイメージセンサ技術,および,ナノフォトニクスを用いる利点の一つは,個々の素子を微小なスケールで実現できることにある.従来の光学システムでは,光学素子やステージの位置や角度などを可動式とすることで,測定条件を変えるものが発とする。これに対して,提案手法では,「集積化」が可能である.条件の異なる測定系を多数配置することにより,並列計測による高機能化や高速化,高精度化を実現する.

これらの研究を通じて,CMOS集積回路プロセスによるイメージセンサ画素上への微細光学素子統合および機能集積化の可能性を示し,小型かつ高機能な光学センサへの展開を目指す.

#### 4.研究成果

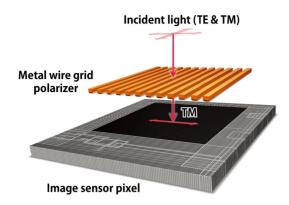

65-nm 標準 CMOS (Complementary Metal-Oxide-Semiconductor)プロセスにおける金属配線層を用いたオンチップ光学素子の検討および試作を行った.また,厳密波結合解析法により画素上における光学素子のシミュレーションを行った.試作素子として,金属グレーティングによる偏光子および回折格子を検討した.シミュレーション結果に基づいて,偏光子搭載画素および画素構造を微細化したイメージセンサを設計した. 図1に画素構造を示す.

画素の微細化により,画素間のクロストークが顕著となることが予測されるため光入射時に Si の表面付近において発生するフォトキャリアのみを検出し,深部で発生したものは,画素周囲に配置したガードリングに流れるようなポテンシャル構造をとる画素を試作し,低クロストーク化を図った.

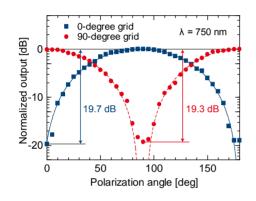

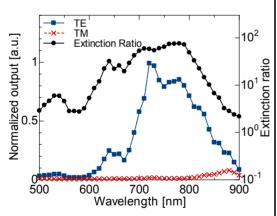

試作した偏光子搭載画素について,光学特性評価を行った.この画素は 65nm プロセスによって作製されているため,金属グレーティングのピッチは可視光波長より十分小さくなっている.グレーティングに対して平行および垂直な偏光に対する感度を比較し,波長 750nm において 19.7dB の消光比を得た.(図 2)また,波長依存性の計測結果から,プロセスに起因する反射および金属配線による吸収のために,700-800nm においてのみ高い消光比が得られることを示した.(図3)

試作画素の結果を踏まえ、配線層による偏光子を搭載したイメージセンサの試作を行った.図4に撮像結果を示す.無偏光の照明(図4a)では、通常のイメージセンサと同様の像が得られ、偏光の照明(図4b)では、偏光子と光源の方向によって透過率が変化することが確認できる.この結果より、偏光像の取得が可能であることがわかる.画素の測定結果から、高い消光比が得られるのは近赤外波長帯に限られるが、THz イメージングや光コヒーレントトモグラフィ(OCT)などの光計測の分野への応用が可能であると期待さ

図 1 金属配線層によるグレーティングを 搭載した画素構造

図 2 金属配線層グレーティング搭載画素 の偏光特性

図3 金属配線層グレーティング搭載画素 の感度および消光比スペクトル

図 4 金属配線層グレーティング搭載イメージセンサ撮像例.(a)無偏光光源,(b)直線偏光光源.

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# [雑誌論文](計 2 件)

Kiyotaka Sasagawa, Norimitsu Wakama, Toshihiko Noda, Takashi Tokuda, Kiyomi Kakiuchi, Jun Ohta, "Image sensor pixel with on-chip hig extinction ratio polarizer based on 65-nm standard CMOS technology," Opt. Express, vol.21, 2013, pp. 11132-11140. DOI:10.1364/OE.21.011132

Norimitsu Wakama, Daisuke Okabayashi, Toshihiko Noda, <u>Kiyotaka Sasagawa</u>, Takashi Tokuda, Kiyomi Kakiuchi, Jun Ohta, "Polarisation analyzing complementary metal-oxide semiconductor image sensor in 65-nm standard CMOS technology," J. Eng., 2013, pp. 1-3. DPO:10.1049/joe.2013.0033

### [学会発表](計 9 件)

<u>Kiyotaka Sasagawa</u>, Norimitsu Wakama, Toshihiko Noda, Takashi Tokuda, Kiyomi Kakiuchi, Jun Ohta, "On-chip polarizer on image sensor using advanced CMOS technology," Photonics West, Feb. 4, 2014, San Francisco, CA, USA(invited).

<u>笹川清隆</u>,若間範光,野田俊彦,徳田 崇,太田 淳,"先端集積回路プロセスによる偏光子搭載イメージセンサ,"光応用電磁界計測(PEM)次元研究専門委員会,2013年8月7日,大阪大学,大阪

Norimitsu Wakama, Daisuke Okabayashi, Toshihiko Noda, <u>Kiyotaka Sasagawa</u>, Takashi Tokuda, Kiyomi Kakiuchi, Jun Ohta, "A polarization-analyzing CMOS image sensor with metal wire grid in 65-nm standard CMOS technology for in-situ chiral analysis," Seventh International Conference on Molecular Electronics and Bioelectronics (M&BE7), Mar. 19, 2013, Fukuoka, Japan.

Kiyotaka Sasagawa, Norimitsu Wakama,

Daisuke Okabayashi, Toshihiko Noda, Takashi Tokuda, Jun Ohta, "Dual-Layer Metal-Grid Polarizer for Polarization Image Sensor in 65-nm CMOS Technology," IEEE sensors 2012, Oct. 31, 2012, Taipei, Taiwan.

Norimitsu Wakama, Nobuya Tachikawa, Kimitada Terao. Mikiko Shibata. Toshihiko Noda, Kiyotaka Sasagawa, Takashi Tokuda, Yasuhiro Nishiyama, Kiyomi Kakiuchi, Jun Ohta, "Real-time multifunctional optical analyzer based on polarization-analyzing CMOS sensor image for microchemical systems, " 2012 International Conference on Solid State Devices and Materials(SSDM2012), Sep. 26, 2012, Kyoto, Japan.

<u>Kiyotaka Sasagawa</u>, Keisuke Ando, Hitoshi Matsuoka, Takuma Kobayashi, Toshihiko Noda, Takashi Tokuda, Jun Ohta, "On-chip metal wire grid polarizer for CMOS image sensor based on 65-nm technology," Conference on Lasers and Electro-Optics (CLEO 2012), May 7, 2012, San Jose, CA, USA.

若間 範充, 岡林 大恭, 野田 俊彦, <u>笹</u>川 清隆, 徳田 崇, 垣内 喜代三, 太田淳, "65 nm 標準 CMOS プロセスを用いた偏光分析 CMOS イメージセンサの消光比評価," 応用物理学会学術講演会, 2012年 09月 13日, 愛媛大学, 松山

岡林 大恭, 若間 範充, 野田 俊彦, <u>笹川 清隆</u>, 徳田 崇, 太田 淳, "65nm プロセスを用いた二層構造オンチップメタル偏光子搭載イメージセンサ," 映像情報メディア学会年次大会, 2012 年 08 月30日,広島市立大学,広島

若間 範充, 松岡 均, 寺尾 公維, 芝田 実希子, 立川 展也, 野田 俊彦, <u>笹川</u> 清隆, 徳田 崇, 西山 靖浩, 垣内 喜代 三, 太田 淳, "偏光分析 CMOS イメージ センサによるマイクロ化学システム用 in situ 不斉計測デバイス," バイオ・マイ クロシステム研究会, 2012年06月12日, 京都大学, 京都

[図書](計 0 件)

### 〔産業財産権〕

出願状況(計 0 件)

取得状況(計 0 件)

[その他]

ホームページ等

http://mswebs.naist.jp/LABs/pdslab/inde

x-j.html

#### 6.研究組織

# (1)研究代表者

笹川 清隆 ( SASAGAWA, Kiyotaka ) 奈良先端科学技術大学院大学・物質創成科 学研究科・助教 研究者番号:5039725

(2)研究分担者 なし

(3)連携研究者なし