# 科学研究費助成事業 研究成果報告書

平成 26 年 5月29日現在

機関番号: 1 2 6 0 8 研究種目: 挑戦的萌芽研究 研究期間: 2012 ~ 2013

課題番号: 24656225

研究課題名(和文)細胞サイズRF CMOSトランシーバ回路技術の研究

研究課題名(英文) A Study on Cell-Size RF CMOS Transceiver Circuit Technology

研究代表者

伊藤 浩之(Ito, Hiroyuki)

東京工業大学・精密工学研究所・准教授

研究者番号:40451992

交付決定額(研究期間全体):(直接経費) 3,000,000円、(間接経費) 900,000円

研究成果の概要(和文):無線通信回路を細胞サイズで実現できるようになれば,環境にばらまいて様々な情報を取得するだけではなく,ナノマシンに用いて体内に注入し癌の病巣検出・治療等にも応用できるのではないか.本研究申請は無線通信回路技術の小型化・スケーラビリティの極限追求を目的とした. 小型化に有利な無線通信回路方式を研究し,集積回路チップの設計や試作・測定を行い,従来よりもはるかに小型な回路で無線通信できる可能性を示した.これにより,目標を達成することができた.

研究成果の概要(英文): If wireless communication circuits could be equivalent to the size of a cell, they are not only distributed in environment for sensing information but can be injected into human body to cu re illness such as cancer. The research purpose is to pursue utmost of small size and scalability of wirel ess communication circuit technology.

We have studied wireless communication circuit architecture suitable for size reduction. Our technology was evaluated through simulation and measurement of integrated circuits, and we could show feasibility of wireless communication by the proposed circuit technology with much smaller size than the conventional one. Thus, the purpose of this work was achieved.

研究分野: 工学

科研費の分科・細目: 電気電子工学・電子デバイス・電子機器

キーワード: 電子デバイス・集積回路

#### 1.研究開始当初の背景

RF 無線通信回路を細胞サイズ(100um 未 満)で実現できれば、環境にばらまくだけでは なく,ナノマシンに用いて体内に注入し癌の 病巣検出・治療等にも応用できるのではない か.本研究申請は RF CMOS 回路技術の小型 化・スケーラビリティの極限追求を目的とす る.LSI プロセス微細化は課題が多いが,依 然として回路小型化の王道である、問題はト ランジスタ(FET)が微細化しても RF・アナロ グ回路が小型化しないことである. インダク タや容量,抵抗が小さくできないためである. インダクタレス回路が研究されているが,容 量や抵抗も FET より大きく対策としては不 十分である.SAW フィルタや水晶発振器の 集積化も課題である. 代替技術としてスイッ チドキャパシタ(SC)や, LC 発振器と補償技 術を用いる手法が提案されているが、LSI上 の受動素子面積が増大する問題がある.

#### 2.研究の目的

細胞サイズという現状より桁違いに小さいRF トランシーバ回路の実現を目指し RF CMOS 回路技術の小型化・スケーラビリティの極限を追求することを目的とする.

アナログ回路小型化問題のシンプルかつ 究極の解決方法は,受動素子を一切用いない ことである.受動素子を基本とする従来のフ ィルタ・発振器に代わる新規技術の開発を行 う.(1) 微細化で FET の遅延が小さくなり 時間分解能が向上した点に着目し,遅延信号 を干渉させてフィルタ特性を実現する新規 連続時間 RF IIR (Infinite Impulse Response) • FIR (Finite Impulse Response) フィルタ技術を研究する . (2) 従来の LC 発 振器に代わる技術として、申請者らが研究し てきた注入同期リング発振器技術を発展さ せる.問題であるスプリアスを低減するため, 発振器に連続時間 RF IIR フィルタ技術を適 用する新規手法を開発する.水晶発振器レス 化のために受信信号を参照信号に用いる技 術を研究する . (3) 小型化に有利なトランシ ーバアーキテクチャ・変調方式を明らかにす る.RFトランシーバチップを試作・測定 し,動作・スケーラビリティを示す.

#### 3 . 研究の方法

(1) 連続時間 RF IIR・FIR フィルタ技術 平成 24 年度に遅延素子のばらつき評価・ デジタル校正技術を研究し,バンドパス LNA を開発する.平成 25 年度に RF DAC とベー スバンドフィルタを研究する.

#### (2) 注入同期リング発振器技術

平成 24 年度にスプリアス低減のための IIR フィルタベース発振器を研究し,平成25 年度に水晶発振器レス技術と PLL 全体の開発を行う.

(3) トランシーバアーキテクチャ・変調方式 の検討

平成 24 年度にアーキテクチャ詳細と変調方式,レベルダイヤグラムを検討する.平成25 年度に研究成果を集約した RF 無線トランシーバを開発する.

アーキテクチャからのトップダウンの観点と,回路からのボトムアップの観点から研究を遂行することにより,研究の効率化を図る.設計,試作・測定,ブラッシュアップをすることで研究の完成度を高める.

#### 平成 24 年度

#### (1) 連続時間 RF IIR・FIR フィルタ技術

提案する RF FIR フィルタが実現可能であることが初期検討で分かっている.遅延ばらつき対策が重要であるため,フィルタ特性の遅延ばらつき感度を計算し遅延時間の仕様を定める.インバータ型アンプやパスゲートをベースとした遅延素子を開発する.時間デジタル変換器(TDC)を用いた新規遅延ばらつきデジタル校正技術を研究する.

上記検討と「(3) トランシーバアーキテクチャ・変調方式の検討」により得られた仕様をもとに、高次バンドパス LNA を研究する. LNA は小型化のために遅延素子数が少ない IIR 型を基本に研究するが、安定性が得られない場合は FIR 型も検討する.

# (2) 注入同期リング発振器技術

注入同期 PLL は申請者や国内外の先行研究で発振信号近傍に現れるスプリアスが問題であることがわかっている。本申請では,バンドパス RF IIR フィルタを応用した新規発振器によってスプリアスを低減させる。全体を IIR 構成にする方法とバッファ自体を IIR 型にする方法を研究し,サイズと雑音が小さい構成を明らかにする。さらに IIR フィルタの通過特性が局所最小となるノッチによってスプリアスを低減させる新規手法も研究する。

(3) トランシーバアーキテクチャ・変調方式 の検討

数 m 程度の近距離通信(特定小電力無線局)を想定し,受信感度-80dBm,出力電力 0dBm, 最高伝送レート 1Mbps を目標としてトランシーバアーキテクチャの詳細を検討する.上 記仕様でトランシーバ構成を最も単純化できる変調方式を検討する.遅延素子の遅延時間が小さくなるほど連続時間アナログIIR/FIR フィルタのカットオフ周波数は高くできる.「(1) 連続時間 RF IIR・FIR フィルタ技術」の研究の知見をもとにフィルタが作りやすいキャリア周波数を検討する.これらの結果をもとにトランシーバ要素回路のレベルダイヤグラムを検討し個別仕様を決める.PLL 参照信号に受信信号を用いるため、妨害波・雑音の影響を考慮しながら LNA の詳細仕様を決定する.

## 平成 25 年度

#### (1) 連続時間 RF IIR・FIR フィルタ技術

RF DAC とベースバンド(BB)フィルタを開発する.前年度の「(3) トランシーバアーキテクチャ・変調方式の検討」で送信信号を位相変調方式に決定した場合は,PLL 出力信号をベースバンド IQ 信号で選択する RF DAC 技術を開発する.変調方式に関係なく,RF DAC 出力信号の隣接チャネル電力比改善のために本研究の遅延ベース FIR/IIR フィルタ技術を活用する.コムフィルタ技術を用いて BB 信号に含まれる高次成分を減衰させる小面積 BB フィルタ回路技術を研究する.

#### (2) 注入同期リング発振器技術

水晶発振器レス化のために受信信号を PLL 注入同期信号に用いる手法を研究する.受信信号が振幅変調の場合,LNA 出力信号をインバータで rail-to-rail に変換して PLL に注入する.QPSK といった多値変調信号の場合,同期信号生成のために位相比較を用いる新規手法を開発する.受信変調信号の位相変化部分を回避するために,遅延信号との自己相関を用いる技術を検討する.

前年度に開発した LNA・発振器と水晶発振器レス化技術を組み合わせ,位相雑音等のトランジスタレベルシミュレーションを行う.必要があれば LNA と発振器の設計をブラッシュアップする.

# (3) トランシーバアーキテクチャ・変調方式 の検討

集大成として、要素回路を統合しトランシーバを構築する.22nm プロセスで 100um 角が目標であるため,180nm CMOS プロセスで818um 角(100um / 22nm×180nm 角)を目標とする.スケマティック設計において,Verilog-AMS 等で要素回路をモデリングしMixed-Signal 解析によりトランシーバ全体での動作検証を行う.試作後のデバックのために外部 Local 入出力機能を含める等の工夫をする.

トランシーバチップは年度後半に試作・測

定を行い,動作とスケーラビリティを示すと ころまでを行う.

#### 4. 研究成果

#### (1) 平成 24 年度

連続時間 RF IIR・FIR フィルタ技術の開発を目標とした.インバータ特性の時間領域シミュレーションを行い,0.5V 電源電圧でコーナー条件を変化させた場合,遅延時間が約10倍ばらつくことがわかった.時間デジタル変換器(TDC)を90nm Si CMOS プロセスで設計し,遅延ばらつきデジタル校正技術の要素技術を開発した.ビヘイビアモデルを用いてバンドパスLNAの基礎検討を行い,目標とした高次のバンドパス特性実現の見通しを得た.

注入同期リング発振器技術として,バンドパス RF IIR フィルタを応用した新規発振器によって注入同期 PLL で問題となるスプリアスを低減させる手法の開発を目標とした.注入信号の低周波成分を高域通過フィルタによって削減することによって,発振信号近傍に現れるスプリアスを低減する新規回路技術を開発した.

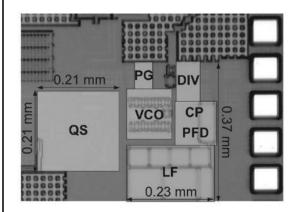

図 1. 注入同期 PLL (雑誌論文[5])

トランシーバアーキテクチャ・変調方式の検討を行った.トランシーバ構成を単純化できる変調方式として On-Off Keying を採用し、トランシーバの低電力化のためにUncertain-IF Architecture を採用した.初期検討としてキャリア周波数は 5GHz 帯とし、レベルダイヤグラムを計算し-74dBm の受信感度が得られる見込みを得た.

## (2) 平成 25 年度

RF DAC やベースバンド(BB)フィルタに利用可能な連続時間 RF IIR・FIR フィルタ技術について研究を行った、遅延差を持たせた方形波を合成するフィルタ技術を開発した、RF

DAC 出力信号の隣接チャネル電力比を 10dB 程 度改善できることを確認し, さらに, BB 信号 に含まれる高次成分を減衰させる小面積 BB フィルタ回路技術実現の見通しを得た.

注入同期リング発振器技術として,受信 信号を PLL 注入同期信号に用いる手法を検討 した.さらに,受信信号を送信機のローカル 信号として用いる技術を研究し,QPSK変調や 16-QAM 変調, 32-QAM 変調が可能であること をトランジスタレベルシミュレーションと 実測にて確認した.

トランシーバアーキテクチャ・変調方式 を検討し,前年度開発した注入同期 PLL 技術 等を統合したトランシーバを構築した.トラ ンシーバコア部の寸法は 65nm プロセスにお いて 850umX450um であり目標の 4 倍の面積と なってしまったが、電源や要素回路形状の最 適化を行うことで目標面積が達成できる見 込みを得た.また, QPSK 変調の場合, 4.3% の EVM で 50Mbps の信号伝送が可能であるこ とを示した.

以上により、小型化に有利なトランシーバ アーキテクチャ・変調方式を研究し,RFトラ ンシーバチップの設計・試作・測定を通して, 回路動作とスケーラビリティの可能性を示 すことができた.細胞サイズという現状より 桁違いに小さい RF トランシーバ回路の実 現を目指し, RF CMOS 回路技術の小型化・ スケーラビリティの極限を追求するという 目的を達成した.

## 5 . 主な発表論文等

## [雑誌論文](計11件)

- [1] Sangyeop Lee, Hiroyuki Ito, Noboru Ishihara, Kazuya Masu, "A Novel Direct Injection-Locked QPSK Modulator Based on Ring VCO in 180 nm CMOS," IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, 查読有, Vol.24, No.4, pp. 269-271, 2014. 10.1143/JJAP.51.04DE07

- [2] Motohiro Takayasu, Atsushi Shirane, Sangyeop Lee. Daisuke Yamane. Hiroyuki Ito, Xiaoyu Mi, Hiroaki Inoue, Fumihiko Nakazawa, Satoshi Ueda, Noboru Ishihara, and Kazuya Masu, "An 8-ch, 20-V Output CMOS Switching Driver with 3.3-V Power Supply for Integrated MEMS Devices Controlling," Japanese Journal of Applied Physics,

- 查読有, Vol. 53, pp. 04EE13.1-8, 2014. 10.1143/JJAP.51.04DE07

- [3] Sho Ikeda, Sangyeop Lee, Tatsuya Kamimura, Hiroyuki Ito, Noboru Kazuva Ishihara. and Masu. "Fractionally Injection-Locked Frequency Multiplication Technique Multi-Phase Voltage-Controlled Oscillator," Japanese Journal of Applied Physics, 查 読 有 , Vol. 52, no. 4, pp. 04CE15-1-04CE15-6, 2013. 10.1143/JJAP.51.04DE07

- [4] Sangyeop Lee, Hiroyuki Ito, Shuhei Amakawa, Noboru Ishihara, and Kazuya Masu. "An Inductorless Cascaded Phase-Locked Loop with Pulse Injection Locking Technique in 90 nm CMOS," International Journal Microwave Science and Technology, 査 読有, Vol. 2013, Article ID 584341, pp. 1-11, 2013. 10.1155/2013/584341

- [5] Sangyeop Lee, Tatsuya Kamimura, Shin Yonezawa, Atsushi Shirane, Sho Ikeda, Hirovuki Ito. Noboru Ishihara, Kazuva Masu, "A Multi-Band Quadrature Clock Generator With High-Pass-Filtered Pulse Injection Technique," IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, 查読有, Vol. 23, No. 2, pp. 96-98. 2013.

- 10.1109/LMWC.2013.2239634

- [6] Hamid Kiumarsi, Hiroyuki Ito, Kenichi Okada, Yusuke Uemichi, Yasuto Chiba, Noboru Ishihara, and Kazuya Masu, "A 60 GHz 3-dB tandem coupler using offset broadside-coupled lines on a silicon substrate, "IEICE Electronics Express, 查読有, Vol. 10, No. 2, pp. 1-12, 2013. 10.1587/elex.10.20120901

- [7] Sangyeop Lee, Hiroyuki Ito, Satoru Tanoi, Noboru Ishihara, Kazuya Masu, "Injection-Locked Fractional Frequency Multiplier with Automatic Reference Pulse-Selection Technique, "IEICE Electronics Express, 查読有, Vol. 9, No. 21, pp. 1624-1629, 2012. 10.1587/elex.9.1624

- [8] Sangyeop Lee, Norifumi Kanemaru, Sho Ikeda, Tatsuya Kamimura, Satoru Tanoi, Hiroyuki Ito, Noboru Ishihara, Kazuya Masu, Ring-VCO-Based Injection-Locked Frequency Multiplier Pulse with Nove I Generation Technique in 65nm CMOS," IEICE Transactions, 查読有, Vol.

- E95-C, No. 10, pp. 1589-1597, 2012. 10.1587 / transele.E95.C.1589

- [9] Atsushi Shirane, Hiroyuki Ito, Noboru Ishihara, and Kazuya Masu, "Planar Solenoidal Inductor in Radio Micro-Electro-Mechanical Frequency Systems Technology for Variable Inductor with Wide Tunable Range and High Quality Factor," Japanese Journal of Applied Physics, 查読有, Vol. 51, 05EE02, pp. 1-4, 2012. 10.1143/JJAP.51.05EE02

- [10] Tatsuya Kamimura, Sangyeop Lee, Satoru Tanoi, Hiroyuki Ito, Noboru Ishihara, and Kazuya Masu, "0.1 V 13 Transformer-Based Quadrature Voltage-Controlled Oscillator with a Capacitor Coupling Technique in 90 nm Complementary Metal 0xide Semiconductor," Japanese Journal of Applied Physics, 查読有, Vol. 51, 04DE04. pp. 1-6. 2012. 10.1143/JJAP.51.04DE04

- [11] Dayang Nur Salmi Dharmiza, Mototada Oturu, Satoru Tanoi, <u>Hiroyuki Ito</u>, Noboru Ishihara, and Kazuya Masu, "An Inverter-Based Wideband Low-Noise Amplifier in 40 nm Complementary Metal Oxide Semiconductor," Japanese Journal of Applied Physics, 查読有, Vol. 51, 04DE07, pp. 1-5, 2012. 10.1143/JJAP.51.04DE07

## [学会発表](計24件)

- [1] Sho Ikeda, Tatsuya Kamimura, Sangyeop Lee, <u>Hiroyuki Ito</u>, Noboru Ishihara and Kazuya Masu, "A 950 µW 5.5-GHz Low Voltage PLL with Digitally-Calibrated ILFD and Linearized Varactor," The 19th Asia and South Pacific Design Automation Conference, Singapore, Jan. 21, 2014.

- [2] Sho Ikeda, Tatsuya Kamimura, Sang yeop Lee, <u>Hiroyuki Ito</u>, Noboru Ishihara, and Kazuya Masu, "A Transformer-Based Current-Reuse QVCO with a Capacitor Coupling Technique in 180 nm CMOS," European Microwave Integrated Circuits Conference 2013 (EuMIC2013), pp.93-96, Germany, Oct. 7-9, 2013.

- [3] Motohiro Takayasu, Atsushi Shirane, Sangyeop Lee, Daisuke Yamane, <u>Hiroyuki Ito</u>, Mi Xiaoyu, Hiroaki Inoue, Fumihiko Nakazawa, Satoshi Ueda, Noboru Ishihara, and Kazuya Masu, "An 8-ch, 20-V Output CMOS Switching

- Driver with 3.3-V Power Supply for Integrated MEMS Devices Controlling," Proc. 2013 Int. Conf. on Solid State Devices and Materials (SSDM 2013), pp.116-117, Fukuoka, Japan, Sep. 24-27, 2013.

- [4] Sho Ikeda, Tatsuya Kamimura, Sangyeop Lee, <u>Hiroyuki Ito</u>, Noboru Ishihara, and Kazuya Masu, "A Sub-1mW 5.5-GHz PLL with Digitally-Calibrated ILFD and Linearized Varactor for Low Supply Voltage Operation," IEEE Radio Frequency Integrated Circuit 2013 (RFIC 2013), USA, Jun. 2-4, 2013.

- [5] Sho Ikeda, <u>Hiroyuki Ito</u>, Noboru Ishihara, Kazuya Masu, "Optimal Design Method for Chip-Area-Efficient CMOS Low-Dropout Regulator," 2012 IEEE Asian Pacific Conference on Circuit and Systems (APCCAS 2012), Taiwan, Dec. 4, 2012.

- [6] Sho Ikeda, Tatsuya Kamimura, Sangyeop Lee, Norifumi Kanemaru, <u>Hiroyuki Ito</u>, Noboru Ishihara, Kazuya Masu, "A 0.5-V 5.5-GHz Class-C-VCO-Based PLL with Ultra-Low-Power ILFD in 65 nm CMOS," IEEE Asian Solid-State Circuits Conference 2012 (ASSCC 2012), Hyogo, Japan, Nov. 12-14, 2012.

- [7] Sho Ikeda, Sangyeop Lee, Tatsuya Kamimura, <u>Hiroyuki Ito</u>, Noboru Ishihara, and Kazuya Masu, "Fractionally Injection-Locked Frequency Multiplication Technique with Multi-Phase Ring VCO," 2012 Int. Conf. on Solid State Devices and Materials (SSDM 2012), Kyoto, Japan, Sep. 25-27, 2012.

- [8] Dayang Nur Salmi Dharmiza, <u>Hiroyuki Ito</u>, Noboru Ishihara, and Kazuya Masu, "Inductorless Wideband Low Noise Amplifier with Variable Gain in 65nm CMOS," 2012 Int. Conf. on Solid State Devices and Materials (SSDM 2012), Kyoto, Japan, Sep. 25-27, 2012.

- [9] Sangyeop Lee, Sho Ikeda, Hiroyuki Ito, Satoru Tanoi, Noboru Ishihara, and Kazuya Masu, "An inductorless injection-locked PLL with 1/2- and 1/4-integral subharmonic locking in 90 nm CMOS," IEEE Radio Frequency Integrated Circuits Symposium 2012 (RFIC2012), Canada, Jun. 17-19 2012.

- [10] Atsushi Shirane, Mototada Otsuru, Sang\_yeop Lee, Shin Yonezawa, Satoru Tanoi, Hiroyuki Ito, Noboru Ishihara,

and Kazuya Masu, "A Process-Scalable RF Transceiver for Short Range Communication in 90 nm Si CMOS," IEEE Radio Frequency Integrated Circuits Symposium 2012 (RFIC2012), Canada, Jun. 17-19 2012.

# 他,国内口頭発表 14件

# 〔その他〕

ホームページ等

http://masu-www.pi.titech.ac.jp/index.html

# 6.研究組織

# (1)研究代表者

伊藤 浩之 (ITO, Hiroyuki)

東京工業大学・精密工学研究所・准教授

研究者番号: 40451992