# 科学研究費助成事業 研究成果報告書

平成 27 年 6 月 24 日現在

機関番号: 16301 研究種目: 若手研究(B) 研究期間: 2012~2014

課題番号: 24700050

研究課題名(和文)多値決定グラフに基く汎用プロセッサの研究開発

研究課題名(英文)A general purpose processor based on a multi-valued decision diagram

# 研究代表者

中原 啓貴 (NAKAHARA, Hiroki)

愛媛大学・理工学研究科・講師

研究者番号:20624414

交付決定額(研究期間全体):(直接経費) 3,400,000円

研究成果の概要(和文):新規決定グラフとしてMulti-terminal multiple-valued decision diagram for characteri stic function representing cluster decomposition (MTMDD for CF)を提案し、国際会議で発表した。また、そのグラフを応用した枝重み付多値決定グラフの一種であるEdge-valued MDD(k)を用いてパケット分類専用回路と組込み用マルチコアプロセッサを考案し、実装した。実装した回路のノウハウを共同研究企業(NDAのため非公開)に技術移転を行い、実用化した。

研究成果の概要(英文): We proposed the Multi-terminal multiple-valued decision diagram for characteristic function representing cluster decomposition (MTMDD for CF) as a new kind of a decision diagram, then presented at the international conferences. Also, we applied the edge-valued MDD(k), which is a variation of the MTMDD for CF, to realize a new embedded processor. We used it to the multi-core processor to realize the packet classification. Also, we developed the commercial packet classifier with co-development company.

研究分野: Embedded System

キーワード: Decision Diagram Multi-valued Logic FPGA Processor

# 1.研究開始当初の背景

ディープサブミクロン時代以前のプロセ ッサではLSIのプロセスを微細化することで. 消費電力を抑えつつ性能向上を達成してき た. しかし, プロセス微細化が 90nm に突入 すると、リーク電流による消費電力の増加が 問題となり、微細化だけではプロセッサの性 能を向上できず、マルチコア等の消費電力性 能に優れたプロセッサが採用されている[1]. 近年、スマートフォンに代表されるモバイル 機器の需要が増え、プロセッサ市場に占める モバイル機器向けのプロセッサの割合が 50%を越えている. モバイル機器はバッテリ 容量に制限があるので、消費電力性能に優れ たプロセッサが必要である[2]. 一方, CMOS プロセスの微細化の限界が議論されるよう になり、2025年に10nmに達した時点で微細 化の限界となると予測されている[3].

以上のことから、将来のプロセッサは(1)短期的視点では消費電力性能に優れること、(2) 長期的視点では CMOS 微細化に変わる方法 を採用できることが求められる.

[1] P. P. Gelsinger, "Microprocessors for the New Millennium: Challenges, Opportunities, and New Frontiers," ISSCC'01, pp. 22-25.

[2] Y. Huh, "New Era of Power Analog," MWSCAS'11, Aug., 2011.

[3] T. Kuroda, "Panel Discussion: The Semiconductor Industry in 2025," ISSCC'10, Feb. 2010.

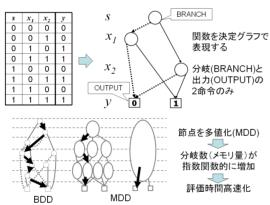

図 1: 決定グラフを模擬する命令

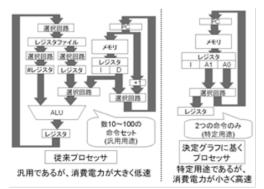

図 2: 決定グラフに基づくプロセッサ

決定グラフとは、論理関数を表現するグラフの一種であり、特定の関数をコンパクトに

表現できる(図 1). 申請者は 2 値決定グラフ (BDD: Binary Decision Diagram)を多値に拡張した多値決定グラフ (MDD: Multi-valued Decision Diagram)に基く特定用途プロセッサ(図 2)の研究開発に従事してきた. MCNC ベンチマーク関数 (主に組み込み用途の制御回路)を多値決定グラフに基くプロセッサに実現した結果,Intel 社Core2Duo プロセッサと比較してピーク性能で 100 倍高速であり,消費電力は 4 分の 1 であった. 多値決定グラフに基くプロセッサが優れている理由は

- 1.決定グラフが制御回路をコンパクトに表現できるため

- 2.決定グラフを模擬する専用命令を用意し、専用命令に特化したアーキテクチャを持つため

であった. 従って, 決定グラフを改良したプロセッサを実現すれば, 従来の問題を解決できると着想した.

#### 2.研究の目的

申請者は MDD で表現できなかった関数をコンパクトに表現する新しい決定グラフを考案し、そのグラフに基くプロセッサの研究開発に取り組む. また、研究開発後に RISC に代表される従来プロセッサと消費電力性能を比較し、提案プロセッサがどの程度優れているのかを明らかにする. 実験的な比較だけではなく、理論的な解析にも取り組む.

本研究は BDD や MDD とは異なる決定グラフを提案し、プロセッサをメモリと単純な回路で実現する点が特色である. 現在のプロセッサがマルチコア化による性能向上を狙っているのに対し、提案手法はメモリ量を増加させることで性能向上を狙っている点が独創的である.

本研究により、汎用の論理回路をコンパクトに表現できる決定グラフを得ることができる、本研究ではプロセッサへの応用に限定しているが、LSIの設計や検証・テストへの転用も可能である。学術的には、CMOSプロセス微細化の限界に達しても、性能向上を続けることができるプロセッサの提案という点に関して意義がある。

# 3.研究の方法

まず、汎用の回路をコンパクトに表現できる新しい決定グラフを考案する.次に,新しい決定グラフに基く汎用論理プロセッサのアーキテクチャを設計し,FPGAとメモリを用いて試作する.そして,消費電力性能に関して従来のプロセッサと試作の比較を行う.最後に,理論的な解析を行い,提案プロセッサが優れていることを示す.

## ・平成 24 年度

汎用の論理回路をコンパクトに表現できる

新しい決定グラフを考案する.新しい決定グラフが考案できない場合は、比較を行う予定のデータ構造(SSBDD: Structure Synthesized BDD)[4]のプロセッサ化を行う.現在、SSBDD はデータ構造のみが提案されているだけであり、プロセッサにした事例は報告されていない.この場合、データ構造の新規性はないが、従来プロセッサに変わるプロセッサを提案する目的は達成可能である.

#### ・平成 25 年度

新しい決定グラフの考案に成功した場合、模擬するための命令セットを検討しコード生成ツールの開発を行う. 不成功の場合はSSBDD からのコード生成ツールを開発する. そして、プロセッサのプロトタイプを FPGAとメモリを用いて実装する. Intel 社の従来プロセッサと消費電力性能に関して比較を行い、理論的な解析を行う.

# ・平成 26 年度

新規決定グラフの考案に成功した場合,理論的解析,及び最適化の検討を行う.並行して実装したプロトタイプの解析を行う.最後に,成果を還元するため,共同研究企業への技術移転を行う.

[4] R. Ubar, "Description of models of digital devices by altrantive grpahs", Proc. of the Tallinn Polytechnic Institute, No. 474, 1979, 11-33.

# 4. 研究成果

新規決定グラフとして Multi-terminal multiple-valued decision diagrams for characteristic function representing cluster decomposition を提案し、国際会議で発表した。また、その決定グラフを応用した枝重み付多値決定グラフの一種である Edge-valued MDD(k)を用いてパケット分類専用回路と組込み用マルチコアプロセッサを考案し、実装した。実装した回路のノウハウを共同研究企業に技術移転を行い、パケット分類器として実用化した。

#### 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# [雑誌論文](計10件)

- 1) <u>Hiroki Nakahara</u>, Tsutomu Sasao, Munehiro Matsuura, Hisashi Iwamoto, and Yisanori Terao, "A memory-based IPv6 lookup architecture using parallel index generation units," *IEICE Transactions on Information and Systems*, Vol.98-D,No.2, pp.262-271, 2015..

- 2) <u>Hiroki Nakahara</u>, Tsutomu Sasao, and Munehiro Matsuura, "A packet classifier based on prefetching EVMDD(k) machines," *IEICE Transactions on Information and Systems*, Vol. 97-D, No. 9,

- pp.2243-2252, 2014. (查読有)

- 3) Hiroki Nakahara, Tsutomu Sasao, and Munehiro Matsuura, "A heterogeneous multi-valued decision diagram machine for encoded characteristic function for non-zero outputs," Journal of Multiple-Valued Logic and Soft Computing, Vol. 23. No.3-4. pp.365-377,2014.(査読有)

- 4) <u>Hiroki Nakahara</u>, Tsutomu Sasao, Munehiro Matsuura, "An architecture for IPv6 lookup using parallel index generation units", *Lecture Note in Computer Science (LNCS7806)*, pp.59-71, 2013. (查読有)

- 5) <u>Hiroki Nakahara</u>, Hiroyuki Nakanishi, Tsutomu Sasao, "On a Wideband Fast Fourier Transform for a Radio Telescope," *ACM SIGARCH Computer Architecture News*, Vol.40, No.5, pp.46-51, 2013.(查読有)

- 6) <u>Hiroki Nakahara</u>, Tsutomu Sasao, Munehiro Matsuura, "A virus scanning engine using an MPU and an IGU based on row-shift decomposition," *IEICE Transactions on Information and Systems*, Vol.E96-D, No.8, pp.1667-1675, 2013. (查読有)

- 7) <u>Hiroki Nakahara</u>, Tsutomu Sasao, and Munehiro Matsuura, "A design method of a regular expression matching circuit based on decomposed automaton," *IEICE Transactions on Information and Systems*, Vol.E95-D, No.2, pp.364-373, 2012. (查読有) 8) <u>Hiroki Nakahara</u>, Tsutomu Sasao, and Munehiro Matsuura, "A low-cost and high-performance virus scanning engine using a binary CAM emulator and an MPU," *Lecture Notes in Computer Science (LNCS7199)*, Vol.7199, pp.202-214, 2012. (查読有)

- 9) <u>Hiroki Nakahara,</u> Tsutomu Sasao, Munehiro Matsuura, "A comparison of multi-valued and heterogeneous decision machines," Journal diagram Multiple-Valued Logic and Soft Computing, Vol.19, No.1-3, pp.203-217, 2012. (査読有) 10) Hiroki Nakahara, Tsutomu Sasao, Munehiro Matsuura, "A Regular Expression Matching Circuit: Decomposed Non-deterministic Realization With Prefix Sharing and Multi-Character Transition," Microprocessors and Microsystems, Vol.36. No.8, pp.644-664, 2012. (査読有)

### [学会発表](計8件)

1) <u>Hiroki Nakahara</u>, Hiroyuki Nakanishi, Kazumasa Iwai, "An AWF digital spectrometer for a radio telescope," *Int'l* Conf. on Reconfigurable Computing and FPGAs (ReConFig2014), メキシコ (メキシ コ), pp.1-6, 2014. (査読有)

2) Hiroki Nakahara, Tsutomu Sasao, Munehiro Matsuura, "An update method for a CAM emulator using an LUT cascade based on an EVMDD(k)", IEEE 44th International Symposium Multiple-Valued Logic(ISMVL-2014)、ブレ ーメン (ドイツ), pp.1-6,2014.(査読有) 【Kenneth C.Smith Early Career Award を

#### 妥當】 3) Hiroki Nakahara, Tsutomu Sasao, "A machine to Matsuura, Munehiro evaluate decomposed multi-terminal multi-valued decision diagrams

functions," characteristic IEEE43rdInternational Symposium on Multiple-Valued Logic(ISMVL-2013)、富山 国際会議場(富山), pp.90-95, 2013. (査読有) 4) Hiroki Nakahara, Tsutomu Sasao, Munehiro Matsuura, "A Packet Classifier LUT cascades Based using EVMDDs(k)," 23rd International Conference on Filed-Programmable Logic and Applications (FPL 2013)、ポルト(ポル トガル), pp.1-6, 2013. (査読有)

5) <u>Hiroki Nakahara</u>, Tsutomu Sasao, Munehiro Matsuura, "A packet classifier using parallel EVMDD(k) machine," IEEE International Symposium on Embedded Multicore SoCs (MCSoC-13),国立情報学研 究所(東京), pp.43-48, 2013. (査読有)

# 【MCSoC2013 Best Paper Award を受賞】

Hiroki Nakahara, Kazumasa Iwai, Hiroyuki Nakanishi, "A high-speed FFT based on a six-step algorithm: Applied to a radio telescope for a solar radio burst," International Conference Field-Programmable (FPT *Technology* 2013), KRP 京都 (京都), pp.430-433, 2013. (査読有)

7) 中原 啓貴,中西 裕之,笹尾 勤, "ポリフェ-ズ・フィルタ・バンクを用いた基数 2<sup>k</sup> FFT に関して: 電波望遠鏡用分光器への適用," 第 11 回情報科学フォーラム(FIT2012), Vol.RC, No.005, 法政大学(東京), pp.49-56, 2012. (査読有) 【FIT2012 船井ベストペーパー賞を

# 受賞】

8) Hiroki Nakahara, Hiroyuki Nakanishi, Tsutomu Sasao, On a wideband fast Fourier transform using piecewise linear approximations: Application to a radio telescope spectrometer.

Lecture Note in Computer Science, Vol.7439, 九州産業大学( 福岡 ), pp.202-217, 2012. (査読有)

[図書](計 0件)

〔産業財産権〕

出願状況(計 0件)

取得状況(計 0件)

[その他]

ホームページ等

愛媛大学研究教育者要覧

http://kengweb.office.ehime-u.ac.jp/Pro files/0009/0004086/profile.html

Hirokinakaharaoboe.net

http://www.hirokinakaharaoboe.net/publi cations J.html

# 6. 研究組織

(1)研究代表者

中原 啓貴 (NAKAHARA, Hiroki) 愛媛大学・大学院理工学研究科・講師 研究者番号:20624414

(2)研究分担者

なし

(3)連携研究者

なし