# 科学研究費助成事業 研究成果報告書

平成 2 9 年 5 月 7 日現在

機関番号: 12501

研究種目: 基盤研究(A)(一般)

研究期間: 2013~2016

課題番号: 25240015

研究課題名(和文)ホログラフィ専用計算システムによる次世代3次元映像・計測技術の研究

研究課題名(英文)Next-generation three-dimensional imaging and measurement by special-purpose computer system for holography

研究代表者

伊藤 智義 (Ito, Tomoyoshi)

千葉大学・大学院工学研究科・教授

研究者番号:20241862

交付決定額(研究期間全体):(直接経費) 31,900,000円

研究成果の概要(和文):次世代3次元映像・計測システムとして期待されているホログラフィ技術において課題となっている計算高速化について,三つのアプローチから研究を展開した.一つめはホログラフィ専用大規模FPGA(Field Programmable Gate Array)ボードの開発である.1ボードでパソコンよりも100倍速い計算速度を記録し,ボード枚数にほぼ比例する並列計算システムの試作に成功した.二つめは種々のアルゴリズムにGPU(Graphics Processing Unit)を適用し,高速化に成功した.三つめは手法そのものの高速化・高画質化である.これらの成果について,40編を越える論文で公表した.

研究成果の概要(英文): Computer holography including electro-holography and digital holography has a potential to be a next-generation three-dimensional technology for imaging and measurement. The most important problem is speedup of the calculating process. We have studied it from three approaches. First, we developed FPGA (Field Programmable Gate Array) board for holography calculation, whose scale is larger than that in the market. The performance of the board is 100 times faster than a personal computer. Furthermore, the parallel system consisting of several boards showed the computing speed improvement in proportion to the number of boards. Secondly, we applied GPU (Graphics Processing Unit) calculation to various algorithms and succeeded in speedup for them. Thirdly, we suggested several methods for speedup and/or high resolution. We published these results in more than 40 articles.

研究分野: 計算機科学

キーワード: 高性能計算 計算システム ホログラフィ 3次元映像 3次元計測

### 1.研究開始当初の背景

ホログラフィは3次元波面を忠実に記録・再生できる唯一知られた手法である.コンピュータの発達とともに,ホログラフィ技術をデジタル化して電子的に扱う研究が進められている.

記録媒体であるホログラムは光の伝搬をコンピュータでシミュレートして作成することもでき、CGH (計算機合成ホログラム:Computer-Generated Hologram)と呼ばれる.CGH に参照光を当てて空中に3次元映像を投影する技術を電子ホログラフィといい、主に映像システムに用いられる.将来の3次元テレビになる可能性を持っている.

一方,ホログラムを光学機器で撮像(取得)し,そのデータからコンピュータ内で元の3次元像を再現(可視化)する技術はデジタルホログラフィと呼ばれ,主に計測システムに用いられる.3次元顕微鏡の実用化が期待されている.

基盤となる技術の研究が盛んになりつつあり,日本の研究が世界を一歩リードしている状況にあった(総務省「ユニバーサル・コミュニケーション技術に関する調査研究会」最終報告,2007).収益に直結するような企業研究にはなり得ていないが,将来の産業の柱になり得る技術であり,アカデミックな研究機関で当該研究領域を促進させることは重要な課題であった.

### 2.研究の目的

ホログラフィは冗長性の高いイメージング技術であり、ホログラムは膨大な情報量を持っている.実用的なサイズのホログラム在現界には現在した計算機環境でも難しく、実用化になの発達した計算機環境でも難しく、実用化にないる.一方で、ホログラムの情報とは、専用計算システムは開発することで大幅な高速化が望める.本研究は、高速なホログラフィ専用計算システムに適用したの研究を大きく進展させることを目的とした.

#### 3.研究の方法

3つのアプローチから研究を展開した.

(1) ホログラフィ専用計算機システムを読み書き可能な LSI である FPGA を用いて開発する.現在のテレビが受像機器であるように,将来,ホログラフィによる映像システムや計測システムが実用化された場合には,専用ハードウェアの量産が行われると予想される.そこで,私たちの研究室では 1992 年から継続して HORN (HOlographic ReconstructioN)と名付けたホログラフィ専用計算機の研究開発を行っている.今回のシステムは8番目の試作(HORN-8)であり,大規模 FPGA を複

数用いたシステムを(外注せずに)独自で行う。今日の大規模化した電子回路においては、回路設計,及び,基板設計には高いノウハウが必要であり、ユーザー(計算機を使う側)が直接開発に携わることは、ほとんど行われなくなってきている。しかし、どのようなハードウェアが必要かはユーザーでなければわからないことが多い。今回の試作を自作することで、ハードウェアによる実用化への可能性、及び、課題を導出する。

- (2) 専用計算機システムはコストも時間もかかる.そこで,GPU を用いた計算システムで高速化の研究を並行して行う.GPU ボードはどのコンピュータにも搭載されているもので,安価で並列計算を行うことができる.ここでの研究成果は専用計算機の開発にも連動する.

- (3) ホログラフィ技術を実用化するためには,高速化,及び,高画質化のアルゴリズムを改善していく必要がある.ソフトウェアレベルで新しいアルゴリズムの研究開発を行う.

### 4. 研究成果

(1) 図 1 が開発した HORN-8 ボードである.PCI Express の規格にそった基板にザイリンクス社製の大規模 FPGA である Virtex5 チップを 8 個搭載している.これほど大規模 FPGA ボードは(少なくとも)市場には出回っていない.1 ボードにホログラム生成回路を4,480 個実装し,250 MHz で動作させることに成功した.毎秒 15 フレーム以上の速つを10歳功した.毎秒 15 フレーム以上の速つさい映像となることが知られている.HORN-8 ボードは,10,000 点で構成される3次元物体に対して,1 秒間に30 フレームのCGH を生成し,パソコンと比較して130 倍の高速化を実現した.

図 1 . HORN-8 ボード

図 2 は HORN-8 ボードを 6 枚実装したクラスタシステムである . 2 枚 , 4 枚 , 6 枚とボード数を増加させたシステムの計算速度は , ほぼ比例して高速化し , 6 枚のときでパソコンの 700 倍に達した .

図 2 . HORN-8 クラスタシステム

(2) FPGA が内蔵しているメモリ容量はそれほど大きくない.そのため,一度に計算できる3次元物体の規模に制約が生じる.3次元物体を点群で表したとき,HORN-8ボードに取り込めるのは16,000点までである.しかしまである3次元物体を扱うことが可能のある.し約るのように物体点を分割してCGHを作えばよい.例える3のように物体点を分割してCGHを作えばよい.例れる物体点を分割し、6枚のHORN-8ボードに並列計算をはる.FPGA ボードの開発と並行して,GPUを用いて検証を行い,所望の結果を得た.

図3.物体点分割による並列計算

上述のように,主に映像システムに用いられる電子ホログラフィにおいては,計算システムのメモリ量の負荷を軽くできる.これは,必要なデータ量が3次元物体に比例して取り扱うことができるためである.

一方で,主に計測系で使われるデジタルホログラフィでは,ホログラムサイズに応じたメモリ量が必要になることが多い.ホログラフィは冗長性の高い技術であり,3次元物体に比べてホログラムのデータ量は1~2桁大きい.そのため,FPGAを用いた専用計算機システムは,より複雑になる.現段階では,FPGAよりも汎用性の高いGPUを用いた並列計算システムの方が有効であることが多い.そは,GPUによる並列計算システムを多く取り組んだ.GPUシステムを用いることで,パソコン(CPU)単体に比べて20-50倍の高速化が達成できている.

本研究課題では, CPU, GPU, FPGA に加え,

一般の CPU よりも多くの計算コアを持つ Intel 社 Xeon-phi を使った並列計算も行った.計算対象に応じて使い分けると効率的である.それぞれの特徴を表1にまとめる.ホログラフィ計算においては,多くの場合,GPUのコストパフォーマンスが高い.

表1.計算デバイスの特徴

|          | コア数                              | 実装 | コスト |

|----------|----------------------------------|----|-----|

| CPU      | 10¹                              | 易  | 低   |

| Xeon-phi | 10 <sup>2</sup>                  | 標準 | 標準  |

| GPU      | 10 <sup>3</sup>                  | 標準 | 標準  |

| FPGA     | 10 <sup>1</sup> -10 <sup>4</sup> | 難  | 高   |

(3) 新たな高速化手法として,主に2つのアルゴリズムを提案した.一つはウェーブレット縮退を利用して計算量を削減した WASABI (WAvelet ShrinkAge-Based superposition) 法である.従来の手法に比べて,50倍の高速化を記録した.

もう一つは私たちのグループで開発した 波面記録法の改良である.波面記録法ではコンピュータ内に仮想的な波面記録面を置く. この波面記録面を複数にし,自動配置することで,3次元形状に応じた高速化を可能にした.

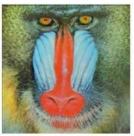

画質の改善については,ランダム位相フリー法を提案した.デジタルホログラフィで再である。しかし,きれいな平面に光を照射する。しからに反射してしまって,所望のでもこのように反射してしまって,所望のででもでするででする。とですらいですが近間でですが近間でである。とでする。私たちは、所望の像相はの代わりに計算された光を照射した。図4がそのの第である。

図 4. ランダム位相法(左)とフリー法(右)

(4) ホログラフィに代わる可能性がある技術として,ボリュームディスプレイの研究を並行して行った.指向性を持つアルゴリズムの開発に成功し,光制御のディスプレイの可能性を示すなどの成果を上げた.

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### [雑誌論文](計44件)

平山竜士,鈴木智孝,<u>下馬場朋禄</u>,白木厚司,成瀬誠,中山弘敬,<u>角江崇</u>,<u>伊藤智</u> 義 , Inkjet printing-based volumetric display projecting multiple full-colour 2D patterns, Sci. Rep., 查読有, 7, 46511, 2017,

10.1038/srep46511

下馬場朋禄, 伊藤智義, Fast generation of computer-generated hologram using wavelet shrinkage, Opt. Express, 查読有, 25, 77-87, 2017,

10.1364/0E.25.000077

下馬場朋祿,角江崇,伊藤智義, Review of fast algorithms and hardware implementations on computer holography, IEEE Trans. Ind. Inform., 查読有, 12, 1611-1622, 2016,

10.1109/TII.2015.2509452

平山竜士,白木厚司,成瀬誠,中村振一郎,中山弘敬,<u>角江崇</u>,<u>下馬場朋禄</u>,<u>伊藤智義</u>,Optical Addressing of Multi-Colour Photochromic Material Mixture for Volumetric Display,Sci. Rep.,查読有,6,31543,2016,

10.1038/srep31543

遠藤優,<u>下馬場朋禄</u>,<u>角江崇</u>,<u>伊藤智義</u>, GPU-accelerated compressive holography, Opt. Express, 查読有, 24, 8437-8445, 2016,

10.1364/0E.24.008437

平山竜士,中山弘敬,白木厚司,<u>角江崇</u>, 下馬場朋禄,伊藤智義, Image quality improvement for a 3D structure exhibiting multiple 2D patterns and its implementation, Opt. Express,查 読有, 24, 7319-7327, 2016,

10.1364/0E.24.007319

西辻崇, <u>下馬場朋禄</u>, <u>角江崇</u>, 荒井大輔, <u>伊藤智義</u>, Simple and fast cosine approximation method for computer-generated hologram calculation, Opt. Express, 查読有, 23, 32465-32470, 2015,

10.1364/0E.23.032465

<u>角江崇</u>, 西辻崇, 川島徹也, 鈴木啓介, 下馬場朋禄, 伊藤智義, Aerial projection of three-dimensional motion-picture by electro-holography and parabolic mirrors, Sci. Rep., 查読有, 5, 11750, 2015,

10.1038/srep11750

下馬場朋禄,角江崇,遠藤優,平山竜士, 檜山大輔,長谷川鋭,長浜佑樹,佐野麻 理恵, 老川 稔, 杉江崇繁, 伊藤智 義,Random phase-free kinoform for large objects, Opt. Express, 查読有, 23, 17269-17274, 2015,

10.1364/0E.23.017269

西辻崇, 下馬場朋禄, 角江崇, 伊藤智義, Fast calculation of computer-generated hologram using run-length encoding based recurrence relation, Opt. Express, 查読有, 23, 9852-9857, 2015,

10.1364/0E.23.009852

下馬場朋禄,伊藤智義, Random phase-free computer-generated hologram, Opt. Express, 查読有, 23, 9549-9554,2015, 10.1364/0E.23.009549

平山竜士,成瀬誠,中山弘敬,竪直人,白木厚司,<u>角江崇</u>,<u>下馬場朋禄</u>,大津元一,<u>伊藤智義</u>, Design, Implementation and Characterization of a Quantum-Dot-Based Volumetric Display, Sci. Rep.,查読有,5,8472,2015,10.1038/srep08472

荒井大輔,下馬場朋禄,村野弘樹,遠藤優,平山竜士,檜山大輔,<u>角江崇</u>,<u>伊藤智 義</u>, Acceleration of computergenerated holograms using tilted wavefront recording plane method, Opt. Express,查読有, 23, 1740-1747, 2015, 10,1364/0E.23.001740

庭瀬裕章,高田直樹,荒木啓充,中山弘敬,杉山充,<u>角江崇</u>,<u>下馬場朋禄</u>,*伊藤* 智義, Real-time spatiotemporal division multiplexing electroholography with a single graphics processing unit utilizing movie features, Opt. Express 查読有, 22, 28052-28057, 2014,

10.1364/0E.22.028052

村野弘樹,<u>下馬場朋禄</u>,杉山充,高田直樹,<u>角江崇</u>,老川稔,<u>伊藤智義</u>,Fast computation of computer-generated hologram using Xeon Phi coprocessor, Comput. Phys. Commun., 查読有, 185, 2742-2757, 2014,

10.1016/j.cpc.2014.06.010

### [学会発表](計181件)

木村祐哉,川口梨紗花,杉江崇繁,<u>角江</u> <u>崇,下馬場朋禄</u>,<u>伊藤智義</u>,Circuit Design of Special-Purpose Computer for Holography HORN-8 Using Eight Virtex-5 FPGAs,3D systems and Applications (3DSA2015), Taipei, Taiwan, 2015.8.25-28

#### [その他]

ホームページ等

http://www.te.chiba-u.jp/~brains/jp/ind

ex.html

### 6.研究組織

### (1)研究代表者

伊藤 智義 ( ITO, Tomoyoshi ) 千葉大学・大学院工学研究科・教授 研究者番号: 20241862

## (2)研究分担者

下馬場 朋禄 (SHIMOBABA, Tomoyoshi) 千葉大学・大学院工学研究科・准教授 研究者番号: 20360563

## (3) 研究分担者

角江 崇 ( KAKUE, Takashi ) 千葉大学・大学院工学研究科・助教 研究者番号: 40634580

## (4) 研究分担者

増田 信之 (MASUDA, Nobuyuki) 東京理科大学・基礎工学部・准教授 研究者番号: 60323333