#### 科学研究費助成專業 研究成果報告書

平成 27 年 6 月 1 1 日現在

機関番号: 12701

研究種目: 挑戦的萌芽研究 研究期間: 2013~2014

課題番号: 25630141

研究課題名(和文)演算エネルギーの熱力学的限界の実験的解明と可逆演算回路への展開

研究課題名(英文)Experimental verification of minimum energy limit of computation and its

application to reversible computing

#### 研究代表者

吉川 信行 (YOSHIKAWA, NOBUYUKI)

横浜国立大学・工学(系)研究科(研究院)・教授

研究者番号:70202398

交付決定額(研究期間全体):(直接経費) 3,100,000円

モードQFP回路のビットエネルギーが実測により10zJまで低減できること、論理的・物理的に可逆な論理回路が断熱モードQFP回路を用いて構成できることを明らかにした。

研究成果の概要(英文): In this project, we aimed to verify the minimum energy consumption in computation, known as the Landauer limit, by using adiabatic quantum flux parametron (QFP) circuits. In order to investigate the Landauer limit, the energy consumption of the adiabatic QFP gate was measured by using a superconducting resonator coupled with an adiabatic QFP gate. In addition, we proposed a new reversible QFP logic gate, whose entropy is not changed during the computation. The results showed that the bit energy of the adiabatic QFP logic gate is estimated to be 10 zJ in experiment. It was also verified that logically and physically reversible logic gate can be realized by using adiabatic QFP circuits.

研究分野: 電子工学 集積回路工学 超伝導エレクトロニクス

キーワード: 超伝導材料・素子 先端機能デバイス 低消費電力 超高速情報処理 デバイス設計・製造プロセス 超伝導回路 ジョセフソン素子 集積回路

#### 1.研究開始当初の背景

論理回路の1ビットの演算に要する最小エネルギーは、Landauerによる考察以来[1]、様々な議論がなされているが、未解決な問題である。熱力学的考察によれば、1ビットの最小演算エネルギーは kgTln2 と予想される。また、演算に伴う情報の消失がなければ、Landauerリミット kgTln2 を下回る無限小のエネルギーでの演算を可能とする、いわゆる可逆計算機も提案されている。

一方、近年の CMOS 論理回路に基づく情報機器の消費電力の増大は著しく、その消費エネルギーが情報機器の性能を制限している。したがって、論理回路のビットエネルギーの最小値を明らかにすることは、学術上のみならず、工学的にも極めて重要な課題である。

このような背景の中で、最近、演算エネルギーの最小値に関する研究がにわかに活発になっている。例えばダブルウェルポテンシャル中の微小ビーズの運動を論理演算に見立てた力学系において、Landauer リミットの存在を示唆する実験結果が報告されている[2]。

これに対して、我々は QFP (Quantum Flux Parametron)回路と呼ばれる超伝導論理ゲートを適切なパラメータで断熱動作させることで、その演算エネルギーを動作速度に比例して減少できることを示した[3]。我々は、断熱モード QFP 回路をゆっくりと動作させることにより、Landauer リミットに迫る微小エネルギーでの演算が可能であると考えている。

#### 2.研究の目的

本研究は、集積化が可能な超伝導断熱モード QFP 回路を用いて、演算エネルギーにおける Landauer リミットの存在を明らかにする。超伝導共振法に基づく微小エネルギー測定法を用いて断熱モード QFP 回路の消費エネルギーを測定し、その下限値を同定する。更に論理演算で情報消去を伴わない可逆論理ゲートを新たに提案し、その動作実証を通して Landauer リミットを破る論理演算の可能性を示す。これらの技術は、現在の演算回路の消費エネルギーを 6 桁以上下げることを可能とし、情報機器の消費電力を飛躍的に低減できる。

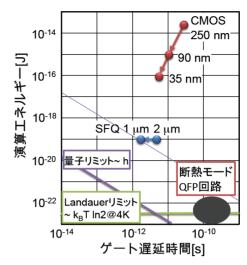

演算におけるエネルギー下限値の存在は、 長年の未解決問題であり、集積化が可能な演 算回路での実証例はない。本研究により、情 報の消去に伴う Landauer リミットの存在 が実証され、情報の消去を伴わない可逆演算 では Landauer リミット以下のエネルギー での演算が可能であることが実証されれば、 学術的な意義は極めて大きい。また、図1に 示す様に、これらの技術は現在の演算回路の 消費エネルギーを6桁以上引き下げること を可能とし、情報機器の消費電力を飛躍的に 低減できる。

図 1 各種論理ゲートの演算エネルギーと遅延時間の比較

#### 3.研究の方法

本研究における主要な研究課題は以下の2つである。

断熱モード QFP 回路の演算エネルギーの評価

## 可逆論理回路の提案と動作実証

研究は研究代表者である吉川が研究全般を推進した。研究協力者として大学院学生3名が、それぞれ可逆 QFP 回路のシミュレーション、断熱モード QFP 回路の設計とエネルギー測定、可逆 QFP 回路の設計と動作実証を行なう。チップ試作は産業技術総合研究所の Nb 超伝導集積回路プロセスを用いた。以下にそれぞれの具体的な研究項目を示す。

断熱モード QFP 回路の演算エネルギーの評価

熱雑音を考慮した数値シミュレーションにより、断熱モード QFP 回路の誤り確率 (BER)とビットエネルギーを評価した。QFP 回路の動作スピードやシャント抵抗の変化に対して、ビットエネルギーや BER がどのように変化するかを調べた。これにより、断熱モード QFP のビットエネルギーの下限値を数値シミュレーションにより明らかにした。

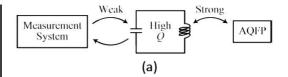

また、実験において超伝導共振法に基づき、 断熱モード QFP 回路の演算エネルギーを測 定した。測定では断熱モード QFP 回路を高 Q 超伝導共振器と結合させ、外部 Q をネット ワークアナライザにより測定した。

# 可逆論理回路の提案と動作実証

断熱モード QFP を用いた可逆演算回路を提案し、その論理動作の可逆性をシミュレーションにより検証した。また、演算エネルギーと動作周波数の関係を数値シミュレーションにより評価し、演算エネルギーの理論的下限値を明らかにした。さらに、実際に断熱オード QFP 回路を超伝導集積回路プロセスを用いて作製し、回路の論理的、物理的可逆動作を実験的に検証した。

### 4.研究成果

善各研究項目に対して以下の研究成果を得 た。

断熱モード QFP 回路の演算エネルギーの評価

有限温度を仮定し、断熱モード QFP 回路のビット誤り率(BER)を数値シミュレーションにより評価した。これにより有限温度においても断熱モード QFP 回路が安定に動作することを明らかにした。また、アンシャントで Q 値の高い断熱モード QFP 回路は、Landauer リミット kBT を下回るビットレーションにより示した。これにより断熱モード QFP 回路は、従来の SFQ 回路に対して 3 桁以上の低消費電力で動作できることを明らかにした。

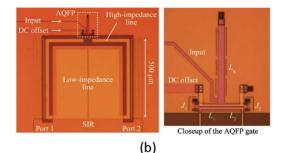

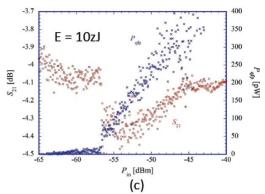

超伝導共振法に基づき、断熱モード QFP 回路の演算エネルギーを測定した。図 2 に我々が行なった超伝導共振法による微小エネルギーの測定結果を示す[論文 ]。測定では1つの断熱モード QFP 回路を高 Q 超伝導共振器イザにより測定した。図 2 (c)に示す様の大部が見られた。この量から断熱モード QFP 回路の損失を見積もることができる。その結果、測定において1ビットの演算を行う値を限が要な消費エネルギーとして10zJの値を得た。この値は従来のSFQ 回路に対して100倍以上小さく、また最新の CMOS 回路に対しても5 桁以上小さい。

# 可逆論理回路の提案と動作実証

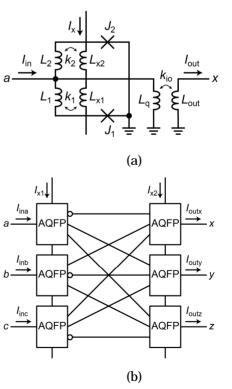

図3に断熱モード QFP 回路を用いた可逆 回路の構成を示す。可逆 QFP 回路は、図 3 (a) の断熱モード QFP を構成要素とし、3つの ディジタル信号入力端子(a, b, c)と3つのデ ィジタル信号出力端子(x, y, z)を持つ。3つの 端子から入力された信号に対して論理演算 が行なわれ、3つの出力端子から信号が出力 される。本回路は、任意のディジタル信号入 力に対する出力信号をそのまま出力端子か ら入力すると、元のディジタル信号が入力端 子に出力されるという可逆的動作を行なう ことができる。したがって、入力端子から出 力端子に、あるいは出力端子から入力端子に 双方向の論理演算が可能である。このような 可逆回路は、演算における情報のエントロピ ーの変化が無く、原理的に無限小のエネルギ ーでの論理演算が可能である。

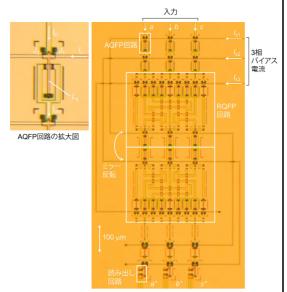

本研究で我々は、可逆 QFP 回路を提案・設計し、産業技術総合研究所のニオブ集積回路プロセスを用いて試作を行った。図4に試作した可逆 QFP 回路の顕微鏡写真を示す。写真の回路は可逆 QFP 回路2段から構成され、そのうち1段は物理的に入出力が反転されている。我々はこの回路において、可逆QFP 回路での論理演算が可逆的に行なわれることを実験的に示した。また、数値シミュ

図2 超伝導共振法による断熱モード QFP 回路のビットエネルギーの測定。(a) 回路構成。(b)チップ写真。(c) S パラメータと消費エネルギー測定結果。

図3 可逆 QFP の構成。(a) 構成要素である断熱モード QFP。(b) 断熱モード QFP によって構成された可逆 QFP 回路。

図4 可逆 QFP 回路のチップ写真。回路は 産業技術総合研究所の標準ニオブ集積回路 プロセスで製作された。

レーションによりにより可逆 QFP 回路の論理演算にエネルギーの下限がないことを示した。

本回路は、5 GHz のクロック周波数を仮定した場合、1 ビットあたり 1 zJ のエネルギーでの論理演算動作が可能である。これは同じスピードで動作する半導体 CMOS 回路に対して6桁以上優れており、本研究により極限的低消費エネルギーで動作可能な論理ゲートの原理実証に成功した。

# <引用文献>

- [1] R. Landauer, IBMJ. Res. Develop., 5, 183 (1961).

- [2] A. Bérut et al., Nature 483, 187 (2012).

- [3] N. Yoshikawa et al., SSDM 2011, Nagoya, 2011.

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文](計33件)

K. Inoue, N. Takeuchi, T. Narama1, Y. Yamanashi, N. Yoshikawa, "Design and demonstration of adiabatic quantum-flux-parametron logic circuits with superconductor magnetic shields," Supercond. Sci. Technol., vol. 28, 2015, 045020. DOI: 10.1088/0953-2048/28/4/045020

N. Takeuchi, Y. Yamanashi, N. Yoshikawa, "Energy efficiency of adiabatic superconductor logic," Supercond. Sci. Technol., vol. 28, 2015, 015003. DOI: 10.1088/0953-2048/28/1/01500

N. Takeuchi, Y. Yamanashi, <u>N. Yoshikawa</u>, "Reversible logic gate using adiabatic

superconducting devices," Scientific Reports, vol. 4, 2014, 6354. DOI: 10.1038/srep06354

N. Takeuchi, T. Ortlepp, Y. Yamanashi, N. Yoshikawa, "(Invited) High-speed Experimental Demonstration of Adiabatic Quantum-Flux-Latches," IEEE Trans. Appl. Supercond., vol. 24, 2014, 1300204. DOI: 10.1109/TASC.2014.2311444

D. Si, K. Inoue, Y. Yamanashi, N. Yoshikawa, "Yield analysis of large-scale adiabatic-quantum-flux-parametron logic: The effect of the distribution of the critical current," Physica C, vol. 504, 2014, pp. 102-105. DOI: 10.1016/j.physc.2014.05.007

N. Takeuchi, T. Ortlepp, Y. Yamanashi, <u>N. Yoshikawa</u>, "Novel latch for adiabatic quantum-flux-parametron logic," Journal of Appl. Physics, vol. 115, 2014, 103910. DOI: 10.1063/1.4868336

N. Takeuchi, Y. Yamanashi and N. Yoshikawa, "Simulation of sub-k<sub>B</sub>T bit-energy operation of adiabatic quantum-flux parametron logic with low bit-error-rate," Appl. Phys. Lett., 103, 062602 (2013). DOI: 10.1063/1.4817974

K. Inoue, N. Takeuchi, K. Ehara, Y. Yamanashi, and N. Yoshikawa, "Simulation and Experimental Demonstration of Logic Circuits Using an Ultra-low-power Adiabatic Quantum-flux-parametron," IEEE Trans. Appl. Supercond., vol. 23, 2013, 1301105. DOI: 10.1109/TASC.2012.2236133

N. Takeuchi, K. Ehara, K. Inoue, Y. Yamanashi and N. Yoshikawa, "Margin and Energy Dissipation of Adiabatic Quantum-Flux-Parametron Logic at Finite Temperature," IEEE Trans. Appl. Supercond., vol. 23, 2013, 1700304. DOI: 10.1109/TASC.2012.2232336

N. Takeuchi, Y. Yamanashi and N. Yoshikawa, "Measurement of 10 zJ energy dissipation of adiabatic quantum-flux- parametron logic using a superconducting resonator," Appl. Phys. Lett., 102, 052602 (2013). DOI: 10.1063/1.4790276

N. Takeuchi, D. Ozawa, Y. Yamanashi and N. Yoshikawa, "An Adiabatic quantum flux parametron as an ultra-low-power logic device," Supercond. Sci. Tech., vol. 26, 2013, 035010. DOI: 10.1088/0953-2048/26/3/035010

# [学会発表](国際会議 87 件、国内会議 99 件、計 186 件)

N. Takeuchi, T. Ortlepp, Y. Yamanashi, N. Yoshikawa, "Experimental demonstration of quantum-flux-latch-based circuits," 2014 Appl. Superconductivity Conference (ASC 2014), Charlotte, North Carolina, USA, August, 2014, 4EOr3A-05.

吉川信行、"【招待講演】SFQ 回路を用いたデジタル多重化"、未踏科学技術協会超伝 導科学技術研究会第83回ワークショップ、 全日通霞が関ビルディング(東京) 2014 年3月10日。

N. Yoshikawa, "Sub-KBT Bit-Energy Operation of Superconducting Logic: What is the Minimum Energy Bound in the Computation?," East Asia Symposium on Superconductor Electronics (EASSE2013), Taiwan Normal University, Taipei, October 23-26, 2013.

N. Takeuchi, T. Ortlepp, K. Inoue, Y. Yamanashi, N. Yoshikawa, "Proposal and Implementation of High-Speed Test Circuits for Adiabatic Quantum-Flux-Parametron Gates," 26th International Symposium on Superconductivity (ISS2013), Tokyo, Japan, November 18-20, 2013, FDP-32.

N. Yoshikawa, N. Takeuchi, K. Inoue and Y. Yamanashi, "(**Invited**) Recent Developments on Ultra-Low-Energy Adiabatic Quantum-Flux-Parametron Logic," 26th International Symposium on Superconductivity (ISS 2013), Tokyo, Japan, November 18-20, 2013, FD-12-INV.

吉川信行、"【**招待講演**】断熱型超伝導回路と可逆演算への展開"、応用物理学会超伝導分科会第48回研究会、産業技術総合研究所つくばセンター(つくば) 2013年11月22日。

吉川信行、佐野京佑、山梨裕希、全伸幸、大久保雅隆、"【**招待講演**】超伝導ストリップ線イオン検出器を用いた飛行時間分析装置のための単一磁束量子読みだし回路の研究"、電子情報通信学会超伝導エレクトロニクス研究会 SCE2013-32、東北大学 電気通信研究所(仙台)、2013年10月3日。

吉川信行、"【**招待講演**】極限的低エネルギー動作を実現する断熱型超伝導回路とその可逆演算動作の可能性"、日本学術振興会超伝導エレクトロニクス第 146 委員会通信・情報処理分科会第 9 回研究会、機械振興会館、2013 年 7 月 22 日。

## [その他]

ホームページ等

http://www.yoshilab.dnj.ynu.ac.jp/yoshilab hp/

- 6. 研究組織

- (1)研究代表者

- (1)研究代表者

吉川 信行 (YOSHIKAWA, Nobuyuki) 横浜国立大学・大学院工学研究院・教授 研究者番号:70202398