#### 科学研究費助成專業 研究成果報告書

平成 27 年 6 月 1 6 日現在

機関番号: 32689 研究種目: 若手研究(B) 研究期間: 2013~2014

課題番号: 25800159

研究課題名(和文)高輝度ハドロン衝突実験での飛跡トリガーを可能にする高速集積回路の新規開発

研究課題名(英文)High-speed circuit development for the fast tracking trigger in high luminosity

hadron collider

研究代表者

木村 直樹 (Kimura, Naoki)

早稲田大学・理工学術院・助教

研究者番号:30547617

交付決定額(研究期間全体):(直接経費) 3,000,000円

研究成果の概要(和文):本研究では、高輝度ハドロン衝突実験のビーム輝度増強の伴う膨大なデータをリアルタイムで選別収集することを可能にする、新しいハードウェアの飛跡認識方法を確立することを目的としている。本研究ではXilinx社のVC707評価ボードを使用しVertix-7 FPGAにて開発を行った。 実装された3連奏メモリの応用からなる飛跡認識法はFPGAに実装され、期待された通りの性能を発揮した。実際には同じ分解能での飛跡認識を約30%程度のメモリサイズで実装することが可能となった。これらの結果は今後のFPGA-ASIC技術の予測される進化と共に、今後の速度を要する飛跡認識や画像認識などにも応用可能である。

研究成果の概要(英文):This study's purpose is establishment a new track recognition method by hardware system for the very high luminosity hadron collision experiment. Because very large quantity memory are necessary for real time tracking and to reduce the cost, it is desirable to develop the original ASIC tip which I specialized in a memory size, but I can largely reduce development time and cost by testing a circuit to implement with development in FPGA.

The track recognition method consisting of the application of ternary content addressable memory was implemented by FPGA and showed performance as I was expected. I was able to really implement track recognition in the same resolving power with around 30% of memory sizes. These results are applicable for track recognition or image recognition with the predicted evolution of the future FPGA-ASIC technology in real time to need future gathering speed, and a new study is in progress.

研究分野: 素粒子物理学 (実験)

キーワード: LHC ATLAS トリガー パターン認識 FPGA 飛跡検出

## 1.研究開始当初の背景

欧州原子核研究所のLHC加速器を用いた ATLAS 実験では、2012 年 7 月のヒッグス粒子 の有力候補となる新粒子の発見など、非常に 大きな成果を見せている。本研究では、デー タ収集方法に着目する。ATLAS 実験では、40 MHz(現在は 20MHz)でビームの衝突がおきる のに対して、最終的に保存することができる データは 400Hz 程度である。つまりデータ取 得システムは衝突データを 1/105 に選別しな ければならないことになる。実際の ATLAS 実 験のデータ取得システムはハードウェアシ ステムである Level-1 トリガーで 40 MHz の 入力を 100 kHz 程度まで選別し、ソフトウェ アシステムの Level-2 とイベントトフィル ター(EF)で最終的な 400 Hz までデータ選別 を行うシステムを取っている。

# 2.研究の目的

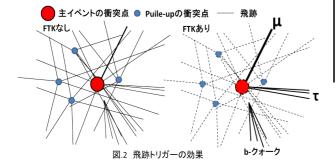

今後の LHC 加速器では、希少データ量を 増やすために LHC ビーム輝度が増強されるこ とによって(SLHC)、ビーム衝突中に複数の粒 子が衝突反応を起こす pile-up 事象が増える ことになり、衝突データの選別を非常に難し くしてしまう。つまり、選別目標であるオブ ジェクトが pile-up からの多大な偽物のオブ ジェクトに隠れてしまい、より特徴的な高い エネルギーをもった物しか選別されない状 態になる。低質量の新粒子の詳細研究を行う としても、すでにトリガーレベルで信号事象 を捨ててしまっている可能性が高く、解析の 幅を狭めている。この問題を解決する手段の 一つが、高速飛跡トリガー(FTK)である。FTK では、100 kHz でシリコン飛跡検出器からの 荷電粒子が残した位置情報を受け、荷電粒子 の飛翔方向、運動量、衝突点からの飛跡発生 ポイントのずれなどの飛跡情報を Level - 2 ト リガーに送る。それにより Level-2 では、オ ブジェクトの生成点が分かるため、pile-up のオブジェクトを削除することができるよ うになる。例えば、長寿命で衝突点から飛跡 の発生源がずれるbクォークや、特徴的な飛 跡を残す レプトンなどを高効率に選別す ることができる(図2)。 つまり今までイベン ト選別に使用できなかった情報を使うこと により、従来はトリガーの時点で捨てていた 重要な事象を FTK で救うことができるのでる。

そこで本研究では、今までにない新しいパターン認識アルゴリズムを開発し、その性能評価を行うことで、FTK システムのさらなる効率化と今後の高輝度ビーム衝突にも対応できるシステムの構築を最終目的としている。本研究期間内では FPGA を用い、システムの効率など有用性を示す。

## 3.研究の方法

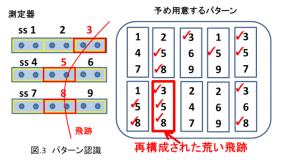

パターン認識は高速で荒い飛跡(パターン)を発見するもので、内容を次に示す(図.3):

1 . 測定器の荒い飛跡情報(スーパーストリップ:SS)を定義する

- 2.測定器上の予想される飛跡の SS パターンを全てあらかじめ用意する

- 3. 実際の飛跡情報がパターン上に現れたら、そこをマークする

- 4 . 全て SS がマークされたパターン情報 を荒い飛跡として送る

このパターン認識では、パターン自体を飛跡情報と照らし合わせるのではなく、飛跡情報をマークしていくだけなので、ハードウェア上では指定されたパターンの SS の AND を取るだけでよい。つまり**ず**べての飛跡情報を受け取ると同時に全ての荒いトラックが認識されることになり、高速な動作が可能である。

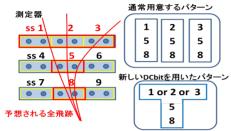

実際のパターン認識の速度は、荒い 飛跡情報である SS のサイズに強く依存して いる。大きな SS サイズを用いた場合、実際 は本物の飛跡からではない偽物のパターン が多く認識されてしまい(図.4)、プロセス時 間を延ばす。しかもこの現象は、今後の高輝 度ビーム衝突では飛跡量が増えることから さらに多くなってくる。一方 SS サイズを小 さくした場合、予め用意しておくパターンの 数が膨大になり(SS サイズ半分でパターン約 10倍)、必要となるチップ数が非常に増大す ることから現実的ではない。つまり今後はチ ップの高密度化で保存できるパターン数を 増やす、単純な方法では対処できなくなる。 それを解決するのが、三値連想メモリに発想 をえた、メモリのデータワード検索時に気に しない bit(Don't Care: DCbit)を用いる方

法である。図.5 のように予想される合いである。図.5 の本がに予想される合いででは、M. ないのでは、DCbit を用いるとででは、1,2,3 は Don't Care)、用意はパターはよりに対すに関すが1パケでは3パンに対しているが1パの飛跡が1の飛跡が1の飛跡が1の飛跡が1の飛跡が1の表が1のでは3 かいのでは3 かいのでは4 かいのである。図.5 かいのでは4 かいのである。図.5 かいのでは4 かいのでは4

されない箇所では細かい SS サイズが保持することで、本来消さなければならない偽物の飛跡(図中 ss1 4 7 などのパターン)を消すことができる。

実際の実験では、飛跡認識に必要となる大量のメモリを安価に確保するため、メモリサイズに特化した独自の ASIC チップを開発することが望ましいが、実装する回路をFPGA にて開発とテストを行うことにより、開発時間とコストを大幅に縮小でき、非常に効率の高い研究が可能となる。FPGA への実装では本来の ASIC に実装される回路を全く同等の回路として実装可能なため、新しい飛跡認識方法の有用性を示すには十分である。

図.5 新たなパターン認識アルゴリズム

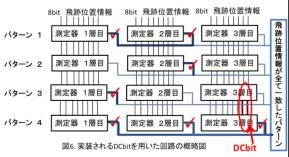

本研究では Xilinx 社の VC707 評価ボードを 使用し Vertix-7 FPGA にて開発を行った。る FPGA に実装される回路は、各測定器の層に 2bitのDCbitを実装した比較的大規模な変更 が少ない回路を作成する。図.6 に全体の概略 図を示し説明する。図.6中では4個のパター ンから一致するパターンを探しており、8bit の飛跡位置情報である SS の情報が上から送 られている。ここではパターン 4 で全ての SS が一致しており、そのパターン情報が送られ ることになるのだが、注目するところは、パ ターン 3,4 では 3 層目の飛跡情報の下位 2bit が DCbit に設定されていることである。 つま り、このパターンでの 3 層目の飛跡情報は、 例えば上位 6bit が 111111 の場合 11111100, 11111101, 11111110,11111111 の 4 種類が許 されることになり、その測定器の層では4倍 の SS サイズでのパターン認識が行われる。

それにより、先に述べた通り、必要なところでは細かい分解能で偽物の飛跡を消すことができる。最終的に予想される性能では、保存するパターン数を保ったまま、偽物の飛跡を除去することができる。

### 4.研究成果

実装された 3 連奏メモリの応用か

らなる飛跡認識法はFPGAに実装され、期待された通りの性能を4発揮した。実際には同じ分解能での飛跡認識を約30%程度のメモリサイズで実装することが可能となった。つまり同サイズのメモリで、より高分解能で飛跡を認識することも可能である。これらの結果は今後のFPGA-ASIC技術の予測される進化と共に、今後の寄り速度を要するリアルタイム飛跡認識や画像認識などにも応用可能であり、新たな研究が進行中である。

## 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文](計 2 件)

- 1 <u>Naoki Kimura</u> on behalf of the ATLAS TDAQ Group, A fast hardware tracker for the ATLAS trigger system Nucl.Instrum.Meth. 査読あり A731 (2013) 224-228

- 2 A. Andreani, N.Kimura (25 the on 56), The Fast Tracker real time processor and its impact on muon isolation, tau and bJet online selection at ATLAS. IEE Trans.Nucl.Sci. 査 読 あ り , 59(2012)348-357

## [学会発表](計 7 件) 招待講演

- 1 <u>Naoki Kimura</u> On behalf of the FTK Collaboration, A Highly Parallel FPGA Implementation of a 2D-Clustering Algorithm for the ATLAS Fast TracKer (FTK) Processor, 19<sup>th</sup> Real-Time Conference, Nara Japan, May 2014

- 2 <u>Naoki Kimura</u> On behalf of the ATLAS Collaboration, Fast Tracker: A hardware Real Time Track Finder for ATLAS Trigger System, 13 th Topical Seminar on Innovative Particle and Radiation Detectors Siena, Italy. Oct 2013

- 3 Naoki Kimura On behalf of the ATLAS TDAQ Group, A Fast Hardware Tracker for the ATLAS Trigger System, 6th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging. Inawashiro, Japan. September 2012

## 一般公演

- 4 木村直樹,三谷貴志,桜井雄基,飯澤知弥,郡川智洋,昌子貴洋,白神賢,仲松弥, 寄田浩平, ATLAS 実験における高速飛跡ト リガー(FTK)の開発現状と今後の展望,日 本物理学会 第69回年次大会

- 5 郡川智洋,飯澤知弥,木村直樹,昌子貴

洋,白神賢,仲松弥,寄田浩平,ATLAS 実験における高速飛跡トリガー(FTK)の開発現状と今後の展望, 日本物理学会 2013 秋季大会

- 6 飯澤知弥,大矢章晴,<u>木村直樹</u>,郡川智 洋,昌子貴洋,白神賢,寄田浩平,ATLAS実 験における高速飛跡トリガーシステムの開 発と構築1、日本物理学会 第68回年次大会

- 7 <u>木村直樹</u>, 飯澤知弥, 大矢章晴, 郡川智 洋, 寄田浩平, ATLAS 実験における高速トラ ッキングトリガーシステムの開発状況, 日本 物理学会 2012 秋季大会

[図書](計 0 件)

〔産業財産権〕

出願状況(計 0 件)

名称: 発明者: 権利者: 種類: 番号:

出願年月日: 国内外の別:

取得状況(計 0件)

名称: 発明者: 権利者: 種類: 番号:

出願年月日: 取得年月日: 国内外の別:

〔その他〕 ホームページ等 なし

- 6.研究組織

- (1)研究代表者

木村直樹 (KIMURA, Naoki) 早稲田大学 理工学術院 助教 研究者番号:30547617

(2)研究分担者

なし ( )

研究者番号:

(3)連携研究者

なし ( )

研究者番号: