## 科学研究費助成事業 研究成果報告書

平成 27 年 6 月 15 日現在

機関番号: 14301 研究種目: 若手研究(B) 研究期間: 2013~2014

課題番号: 25820142

研究課題名(和文)低電磁雑音設計のためのGHz帯におけるLSI電源分配回路の等価回路モデル化手法

研究課題名(英文) Equivalent circuit model of LSI power distribution network for reduction design of electromagnetic emission

研究代表者

松嶋 徹(Tohlu, Matsushima)

京都大学・工学(系)研究科(研究院)・助教

研究者番号:00571415

交付決定額(研究期間全体):(直接経費) 1,800,000円

研究成果の概要(和文):電子機器の高速化に伴い配線が細密化し動作周波数が高くなる中で、信号伝送や電源供給のための配線が近傍の金属と結合し、所望の動作を得られないなどの問題が顕在化している。本研究では、IC内部や回路基板との間を橋渡しするインターポーザの電源供給用の配線を対象に、高周波電磁界結合を表現する等価回路モデル構築を行った。準静近似下での集中素子ではなく、電磁界の分布も考慮した集中素子モデルを導出した。また、CMOSのサブストレートモデルを測定により構築法する手法を示した。市販のICを対象に等価回路モデルを構築し、電磁雑音混入時の特性をシミュレーションにより求めた結果、実測結果と実用上十分な精度で一致した。

研究成果の概要(英文): Signal traces or power supply lines on a printed circuit board (PCB) and an LSI interposer are coupled with the other conductors. The coupling affects it's operation or causes large emissions and degradation of immunity to RF disturbance. High frequency electromagnetic couplings in an IC, an interposer and a PCB are focused in this study, and construction methods of equivalent circuits which express these couplings are proposed. The circuit parameters, C and L, in the proposed equivalent circuit for the PCB and the interposer are defined using electromagnetic energy. In addition, an equivalent circuit model of CMOS with a substrate coupling are extracted by S parameter measurement, and resistances of substrate are measured. Finally, an equivalent circuit of a commercial IC is constructed using measurement and general information of this IC. Measurement results are in good agreement with results of immunity estimation to conducted disturbance using the proposed equivalent circuit.

研究分野: 環境電磁工学

キーワード: EMC 等価回路モデル 電源分配回路 寄生結合 電源系高周波電流 CMOS回路

#### 1.研究開始当初の背景

電子機器の高速化、小型化に伴って回路基 板やLSIインターポーザに存在する寄生結合 の考慮なしでは回路設計が困難になってい る。信号配線など長手方向に一様に長い場合 には伝送線路モデルにより計算が可能であ るが、付近に別の金属パターンが有る場合や、 複雑な形状の配線の場合は電磁界解析に頼 らざるを得ない。しかし、微細配線や不要電 磁放射の要因となるコモンモード電流によ る放射などを計算する場合には、計算コスト が膨大になり、結果を得られるまでの時間が 非常に長くなる。この問題に加えて、昨今で は商品開発の期間が短縮される傾向にあり、 電磁界解析の結果を十分に検証することな く回路設計を完了しなくてはならない場合 が多い。そのため、回路設計や試作後に、不 要電磁放射が規定値を超えることもあり、後 付の対策が必要となる。特に、LSIへ電源供 給を行なう回路基板上およびLSIインターポ ーザ上の電源系配線においては、一般的に配 線が多岐に渡り、配線幅が変化するなど信号 伝送系に比べて複雑な形状となる。電源系配 線への高周波電流の伝達などを加味して回 路設計するためにも3次元や2.5次元の電磁 界解析シミュレータが用いられるが、同様に 計算コストが膨大になる。また、波長に対し て十分に短い区間に分割し、集中素子モデル で表現する PEEC (Partial element equivalent circuit)法も提案されているが、 回路素子が膨大になることや、計算結果から 物理現象を理解する事が難しく、回路設計の 根本的な改善には繋がらない。

このような状況下において、研究代表者は信号伝送系の平衡度に着目してコモン東電流の発生を簡易な計算により予測で表表を提案した。また、その方法を用いて要電磁放射を低減する回路設計方針を出ていてもいていてもいての電源・グラウンド配線についてをポーガ上の電流のが開発を担合した。この抑制設計手法をノイズの発生源であるLSI内部に適用することで、回路基流を抑わることが推測できる。そのためには、

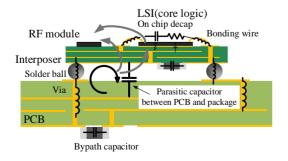

図 1: LSI-インターポーザ回路基板間寄生結

電源系異配線に存在する寄生キャパシタや インダクタによる寄生共振を把握し抑制す る必要がある。

電源系配線の設計に要求される事項としては、LSIから電源供給側をみた入力インピーダンスが十分低く(ターゲットインピーダンス以下)、不必要な高周波電流を外部に伝達させないことが挙げられる。電源系配線に存在する寄生結合によって生じる反共振は、この入力インピーダンスを増加させ、大きな共振電流を発生させる。これらは回路の誤動作を引き起こしたり、外部に放射される電磁雑音を増加させる。

図 1 に示す LSI インターポーザ基板が回路基板 に実装されている系を考える。動作の安定化のために、各基板のグラウンドは広い面を持つことが多い。そのため、対向するグラウンド面間に数 pF 程度の寄生結合が引き起こす反共振周波数は 1 GHz~5 GHz程度となる。携帯電話のようなは、これらが引き起こすこの反共振同波数は 1 GHz~5 GHz程度となる。携帯電話のようなは、論理回路によるが引き起こすこの反共振によって、過間での対害を与える可能性が高く、設計段階の十分な予測と抑制がますます重要になる。

#### 2.研究の目的

研究代表者らは、従来にないインピーダンスバランスや平衡度という概念により、LSIから発生する電磁雑音の低減法を提案してきた。その技術の実用化へ向けて、LSI回路部、LSIインターポーザおよび回路基板それぞれで下記の課題が残っており、それらの解決を本研究の目的とする。

## (1) LSI 内部等価回路モデルの構築

多くの LSI は複数の回路ブロックからなり、同一のサブストレート上に構築される。サブストレートは回路ブロックが動作する際の高周波電流の伝達経路になる。回路ブロックの動作を検証するためには、他回路ブロックから回りこむ高周波電流を正確に予測する必要があり、その計算を簡略化させるためにはサブストレートの等価回路モデルを用いることが重要である。

また、CMOS 回路とサブストレートの結合 を調整することで、LSI 内部回路におけるイ ンピーダンスバランスを実現する。

# (2) LSI インターポーザ回路基板間寄生結 合の等価回路モデル化

これまでの研究により、図1における LSI インターポーザと回路基板のグラウンドに 生じる反共振は、準静近似のもとで求められるキャパシタンスとインダクタンスでは表現できないことを見出した。これに変わる方法として、共振により蓄積された電磁界エネルギーに着目したキャパシタンスとインダクタンスの導出方法を検討し、平板が複数箇

所接続されたより実用的な構造において、その有効性を検証する。

また、グラウンド間に生じる反共振の抑制 手法について検討する。通常、LSI インター ポーザと回路基板間は低インピーダンスで 接続されることが望まれ、抵抗は損失の原因 になるために極力小さくなるよう設計され る。そこで、電源供給時には抵抗の影響を受 けず、共振時のみに抵抗経由で電流が流れ Q 値が低減される構造について検討する。

## (3) 提案等価回路モデルの実用性の検証

市販の IC を対象に本研究で得られた等価 回路構築手法によりモデル構築を行うこと で、提案手法の妥当性を検証する。

本研究では、受動系の等価回路モデル化に着目しており、内部のノイズ源のモデル化を行っていない。そこで、対象とする IC に外部から電磁妨害波が印加された場合の高周波伝達特性や IC の挙動を表現できるかどうかを提案等価回路モデルを用いて検証する。

### 3. 研究の方法

#### (1) LSI 内部等価回路モデルの構築

### (a) CMOS 回路のサブストレート高周波等 価回路

試作した LSI を用いて、ロジック回路電源・グラウンド・サブストレート電位をそれぞれを外部の安定したグラウンドを基準にした3ポート回路として扱い、その特性を外部測定により求める。また、内部回路情報から等価回路トポロジを決定し、測定結果との比較により、回路パラメータを決定する。サブストレートとの結合(pn 接合容量やサブストレート抵抗)を、設計情報からも求め、国路パラメータと比較することで検証する。

## (b) LSI 内部でのインピーダンスバランス の実現

上記で作成した等価回路モデルから、発生する電源系コモンモード電流が最小となるインピーダンスバランス条件を導出する。さたに、LSI内部を模擬した回路を、回路基板上に作製し、可変抵抗によりインピーダンスバランスを変化させ、コモンモード電流の実測により、手法の検証を行う。

## (2) LSI インターポーザ回路基板間寄生結 合の等価回路モデル化

## (a) 複数接続があるグラウンド平板間の反 共振を表す等価回路モデル化

複数接続がある平板間が反共振する際の共振キャパシタンスと共振インダクタンスを定式化する。また、接続の場所や個数を変化させた場合の電磁現象を3次元電磁界解析により求め、平板間に蓄積されるエネルギーにより共振キャパシタンスと共振インダクタンスを算出する。等価回路によって得られた共振特性を、3次元電磁界解析の結果と比較することにより、精度を検証する。

## (b) グラウンド間反共振の抵抗を用いた抑

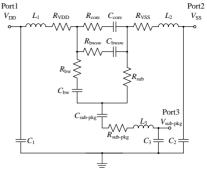

図 2: 試作 LSI の内部回路

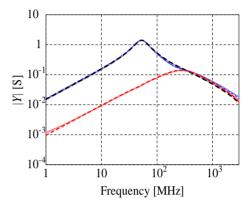

図 3: Y パラメータの比較(黒: Y<sub>11</sub>, 青: Y<sub>22</sub>, 赤: Y<sub>33</sub>, 実線: 測定, 破線:回路計算)

#### 制法

多層 LSI インターポーザにおいて、グラウンド面を 2 層に配置し、それらの間を抵抗性で接続する構造を提案する。また、提案構造を施策し、異なる箇所にグラウンド接続がある場合について、反共振の低減効果を検証する。

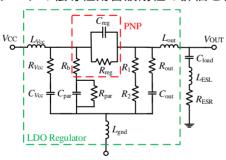

### (3) 提案等価回路モデルの実用性の検証

市販のLDO レギュレータIC を使用して、提案した手法により等価回路モデルを構築する。(1)で検討したベアチップのLSIとは異なり、市販ICにはパッケージのリードフレームやICまでの回路基板上の配線があるが、それらの影響を取り除く手法を検討する。さらに、等価回路トポロジをLDO レギュレータ回路構造により決定し、回路基板設計者の立場に立った等価回路構築を行なう。

また、外部から伝導性妨害波を印加した際の伝達特性や回路動作の挙動を等価回路を 用いたシミュレーションにより求め、実測と 比較することによりその精度や妥当性を検 証する。

# 4. 研究成果

### <u>(1) LSI 内部等価回路モデルの構築</u>

CMOS 回路のサブストレート結合を含む等価 回路を測定により抽出した。試作 LSI におけ る電源系等価回路モデルのトポロジを、回路 図や CMOS の構造から図 2 のように決定した。 これは、インターポーザに実装するためのボ

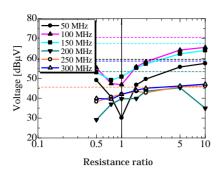

図 4: インピーダンスバランス法によるコ モンモード励振の抑制

ンディングワイヤー等も含んだ等価回路で ある。

電源 VCC, グラウンド VSS, サブストレート電位 Vsub-pkg それぞれをインターポーザ上の安定な電位を基準として 3 ポート回路としてモデル化する。各パラメータは S パラメータ測定結果を元に、回路フィッティングにより求め、設計情報から得られる値と比較することによりその妥当性を検証した。

得られた等価回路を用いて、回路の Y パラメータを計算したところ、図 3 に示すように、 1MHz から 3GHz までの周波数範囲で非常に良い精度で実測結果と一致した。また、pn 接合の容量に直列にあるサブストレート抵抗が数 $\Omega$ 程度であることがわかった。

次に、これらのサブストレート抵抗の値を変化させることで、インピーダンスバランス法によるコモンモード電流の低減法を実測により検証した。ここで、試作LSIの回路内部に抵抗を変化する機構を作製することが困難であったため、回路基板上に市販 CMOS

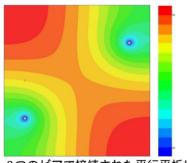

図5: 2つのビアで接続された平行平板にお ける共振時の電界分布((0,0)モード)

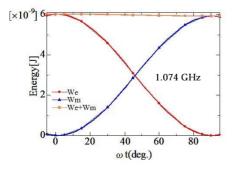

図 6: 電界蓄積エネルギーWe と磁界蓄積エネルギーWm の変化(f<sub>r</sub> = 1.074 GHz)

回路とサブストレートを模擬した回路を回路基板上に実装し、可変抵抗器によりサブストレート抵抗に相当する抵抗を変化させた。結果として、図4に示すように、電源供給側の電源およびグラウンド配線のインダクタンスと、サブストレート抵抗が特定の比になる時に、コモンモード電流を励振するコモンモード電圧が最小になることを示した。

# (2) LSI インターポーザ回路基板間寄生結 合の等価回路モデル化

インターポーザのグラウンド面と回路基板上のグラウンド面を想定した平行平板に下で表える。グラウンド接続用のビアが複なある場合における、平行平板の共振時の電界分布(1.074 GHz)を図 5 に示す。図に示す。図に示す。図に示す。図に示すを中心として弱くなり、ビアのない場所では強い。このような共振を LC 共振してが場所では強い。そこで、図 6 に示す電界正しくない。そこで、図 6 に示す電界エネルギーと関系にあり共振インダクタンスを求める式を導出した。

図 5 のような例では、各ビアを流れる電流は同相であり、電界の向きも同方向であるが、更に高次の共振においてはビアによって電

$$C_{\text{r}i} \equiv \frac{1}{\varepsilon} \frac{Q_{\text{net}i}^2}{e_{\text{r}i}^2} = \frac{1}{\varepsilon} \left( \int \frac{\boldsymbol{E}_{\text{r}i}}{Q_{\text{net}i}} \cdot \hat{\boldsymbol{E}}_i d^3 x \right)^{-2}$$

$$L_{\text{r}i} \equiv \mu \frac{h_{\text{r}i}^2}{I_{\text{net}i}^2} = \mu \left( \int \frac{\boldsymbol{H}_{\text{r}i}}{I_{\text{net}i}} \cdot \hat{\boldsymbol{H}}_i d^3 x \right)^2$$

流の流れる向きが異なったり、電界の向きが異なる場合がある。この場合、電荷の総量 Q と電界エネルギーが対応しない。そこで、1 枚の平板から出る電東密度の法線成分の絶対値を積分した正味の電荷量  $Q_{net}$ を用いて電界エネルギーを規格化し、共振キャパシタとした。また、磁界についても同様に、ビア毎の電荷流量の絶対値の総和を正味の電荷流量(電流) $I_{net}$ とし、これを用いて磁界エネルギーを規格化し、共振インダクタとした。

電磁界エネルギーに着目した共振キャパシタおよび共振インダクタは、高次の共振についても 1 %程度の誤差で共振周波数を計算す

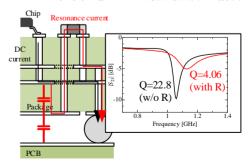

図7: 2つのビアで接続された平行平板にお ける共振時の電界分布((0,0)モード)

ることが出来た。なお、比較には市販の3次 元電磁界解析ソフトウェアを使用した。

次に、この反共振をLSI インターポーザ上で低減する手法について述べる。本来、グラウンド間の接続には、電力消費や電圧降下の観点から抵抗を配置することは望ましくない。そこで、図7に示すようにDC電圧を供給する際には低インピーダンスの経路を電流が流れ、半共振時に抵抗を含む経路を電流が流れる構造を検討した。同図に示すように、直流給電では抵抗を経由しない経路を電流が流れ、抵抗を配置することで、反共振のQ値を低下させることが出来た。

## (3) 提案等価回路モデルの実用性の検証

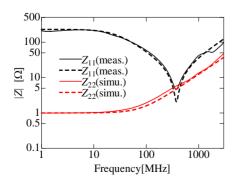

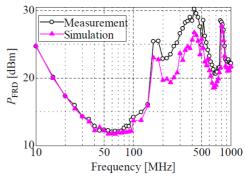

市販の LDO(Low Dropout)電圧レギュレータ IC を使用して、提案等価回路モデル化手法の 実用性を検証した。この LDO 電圧レギュレー タを回路基板上に実装し、外部測定から電源 系等価回路モデルを構築した。対象とした LDO 電圧レギュレータの一般使用者向けに公 開されている情報を元に、図8に示すように 等価回路トポロジを決定し、外部からのSパ ラメータ測定により等価回路パラメータを 推定した。このとき、回路基板上配線が影響 するが、これらを除去する手法を示した。対 象とする IC のみの特性を実測結果から抽出 した後に回路パラメータを推定した。推定し た結果を用いた回路計算により、入出力電圧 端子を各ポートとした2ポート回路における Z パラメータを求め、実測結果と比較したと ころ、図9に示すように良い精度で一致した。 また、本等価回路を用いて、LDO 電圧レギ ュレータの伝導性妨害波耐性の評価を行っ

図 8: LDO 電圧レギュレータの内部回路

図 9: Z パラメータの比較

図 10: LDO 電圧レギュレータの妨害波耐性における実測と等価回路による計算の比較

た。DPI (Direct RF Power Injection)法により、入力電源端子(VCC 端子)に単一周波数の伝導性妨害波を印加した際に、出力端子電圧の DC 成分の変動を観測し、所定の電圧変動幅に達した時を誤動作と判断した。誤動作時の印加妨害波電力を評価量として、実測結果と等価回路を用いたシミュレーション結果を比較したところ、図 10 に示すように、誤差 5dB 程度で一致した。また、妨害波耐性が悪い周波数帯も実測結果と一致していることから、実用上問題ない精度であることを示した。

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### [学会発表](計 9件)

T. Matsushima, N. Ikehara, H. Miyahara, T. Hisakado and O. Wada, "Macro model of LDO voltage regulator for estimation of immunity to conducted disturbance," IEICE technical report, EMC Joint Workshop 2015, Bangkok, Thailand, June 2015 (in press).

池原伸明, 宮原秀敏, 松嶋徹, 久門尚史,

和田修己, ``シリーズレギュレータを対象とした伝導性妨害波耐性の評価用モデルの構築," エレクトロニクス実装学会春季講演大会, 東京, March 2015.

T. Murakami, M. Maeda, Y. Mabuchi, T. Matsushima, T. Hisakado and O. Wada, ``Power and ground phase relation in LSI power distribution network at common mode reduction," 2014 International symposium on Electromagnetic compatibility, Tokyo Japan, May 2014. (査読有り)

前田真彰, 松嶋徹, 久門尚史, 和田修己, "インピーダンスバランス制御による CMOS 基板雑音抑制法,"信学技報, EMCJ2013-30, pp.15-20, July 2013. 松嶋徹, 木村誠, 久門尚史, 和田修己, "CMOS 基板内寄生結合を考慮した LSI 電源系の高周波等価回路の抽出,"電気 学会電磁環境研究会資料, pp.29-34, June 2013.

A. Nakamura, M. Maeda, <u>T. Matsushima</u> and O. Wada, ``Substrate Noise Reduction Based on Impedance Balance using Tunable Resistances,"

9th International Workshop on Electromagnetic Compatibility of Integrated Circuits, pp. 33-36, Nara, Japan, Dec. 2013. (査読有り)

T. Matsushima, N. Ikehara, T. and Hisakado O. Wada, "Improvement of Reproducibility of DPI Method to Quantify Conducted **Immunity** of **LDO** 9th International Regulator," Workshop on Electromagnetic Compatibility of Integrated Circuits, pp. 59-62, Nara, Japan, Dec. 2013. (查 読有り)

M. Maeda, <u>T. Matsushima</u> and O. Wada, "Impedance Balance Control for Suppression of Fluctuation on Ground Voltage in LSI Package," 9th International Workshop on Electromagnetic Compatibility of Integrated Circuits, pp. 134-137, Nara, Japan, Dec. 2013. (查読有り)

T. Matsushima, Y. Mabuchi, T. Hisakado and O. Wada, ``Reduction Method of Common-Mode Noise on Power Supply Cable Using Floating Conductor," Asia-Pacific International Symposium on Electromagnetic Compatibility, pp.85-88, Melbourne, Australia, May 2013. (査読有り)

### 6. 研究組織

# (1)研究代表者

松嶋 徹 (Tohlu Matsushima) 京都大学・大学院工学研究科・助教 研究者番号:00571415