#### 科学研究費助成事業 研究成果報告書

平成 28 年 6 月 17 日現在

機関番号: 13501

研究種目: 挑戦的萌芽研究 研究期間: 2014~2015

課題番号: 26540020

研究課題名(和文)量子化器設計を工夫した広帯域・低消費電力デルタシグマA/D変換器実現への挑戦

研究課題名(英文)Wide-band and Low Power Dissipation Delta-sigma A/D Converter utilizing Optimized Design of Quantizer

### 研究代表者

兼本 大輔 (KANEMOTO, Daisuke)

山梨大学・総合研究部・助教

研究者番号:90603332

交付決定額(研究期間全体):(直接経費) 2,800,000円

研究成果の概要(和文):本課題ではデルタシグマA/D変換器に用いられるデルタシグマ変調器の為の,量子化器利得を設計パラメータとして活用した新たな設計方法の解明を目指し研究を行った為,その研究成果を報告する.「ループフィルタに求められる要求仕様と消費電力」の関係および,「各ループフィルタの係数と量子化器利得」との関係に着目し,ループではないでは、1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円では、1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。1000円である。 する提案並びに検証を行った.

研究成果の概要(英文): A research of design methodology for delta-sigma modulator, which is used in delta-sigma A/D converter, utilizing optimized equivalent gain of quantizer is reported. In the proposed design methodology, "relationship between required specification and power dissipation in loopfilter", and "relationship between coefficient of integrator and equivalent gain" were used to achieve optimized equivalent gain.

研究分野: LSI

キーワード: A/D変換器 デルタシグマ

#### 1.研究開始当初の背景

Information and Communication Technology (ICT)への注目が高まるにつれて,大容量通信が可能なモバイル通信機器の需要がますます増加している.その背景より,広帯域の信号を高精度に変換し,低消費電力で動作する Analog-to-Digital (A/D) 変換技術の重要性が高まってきている.

A/D 変換器には様々な種類が存在する.たとえば,デルタシグマ変調器を用いたデルタシグマ A/D 変換器は A/D 変換器前段に配置するアンチエイリアシングフィルタの仕様要求を抑える事が出来る利点があり,注目されている A/D 変換器の一つである.さらに,連続時間型デルタシグマ変調器は,フィルタ内でのサンプリングが不要になることから,高速・低消費電力動作が見込める A/D 変換器として研究が進められている.

ところで,LSI の多くは製造コストの観点から Complementary Metal Oxide Semiconductor (CMOS)プロセスを用いて製造されている.今までは, CMOS 微細加工技術の進化(スケーリング則)が,高速 A/D 変換回路の特性向上の一端を担ってきた.しかし,今後はその微細化に限界が生じる可能性があることが指摘されており,微細加工技術だけに頼らずとも,A/D 変換器の特性を向上させる,新たな設計方法を提案する必要性が高まってきている.

# 2. 研究の目的

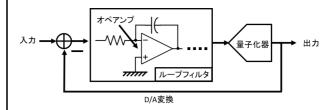

デルタシグマ A/D 変換器は,主にアナログ 回路で実現するデルタシグマ変調器と,ディ ジタル回路で実装されるデシメーションフィルタから構成されている.本課題では,デルタシグマ変調器に関して研究を行った.デルタシグマ変調器は「ループフィルタ」・「量子化器」,D/A 変換器(フィードバックパス)から構成される.例として,図1にアクティブ RC 積分器から構成される連続時間型デルタシグマ変調器の概略図を示す.

多くの研究では、消費電力の大半を決定づけるループフィルタに関する改良がなされてきた.ただし、変調器の広帯域化が求められると、ループフィルタ内にもちいられるオペアンプの広帯域要求が過度に進むこと、さらに CMOS スケーリング則の鈍化への懸念により、変調器の帯域増加以上に消費電力が増大する問題を考える必要がある.

そこで本研究では、ループフィルタの後段に位置する量子化器の利得に着目し、得られる Signal-to-Quantization Noise Ratio (SQNR)を一定の基、オペアンプに求められる仕様を緩和する、デルタシグマ変調器の設計

図 1: アクティブ RC 積分器を用いた 連続時間型デルタシグマ変調器

方法の解明を目指し,研究を行った.本研究における設計方法の検証には,無線通信機器に用いる A/D 変換器を想定し進めることとした.

#### 3.研究の方法

広帯域積分器を初段に用いる場合,後段に 位置する積分器の入力換算雑音量を抑える 事が出来る.ただ,広帯域積分器を実現する ためには, 広帯域にわたり十分な利得を有す るオペアンプを用いる必要があり,消費電力 が増加する傾向にある.フィードフォワード パスを有する Cascade of Integrators with Feed-Forward summation (CIFF) 型デルタシ グマ変調器では,初段の積分器はシステムを 安定に動作するために広帯域設計、すなわち 帯域の広いオペアンプの利用が求められる. 入力換算雑音を抑える目的には有利に働く 為,選択されやすい構成である.ただし,回 路設計を行う上で,入力換算雑音の抑制以上 に過度の広帯域積分器を用いる必要が発生 した場合は,消費電力の観点から好ましくな

本研究ではCIFF型に関して、得られるSQNRが一定の基、量子化器の利得と初段の積分器利得が反比例の関係にある事を利用し(

),積分器利得要求の緩和を目指す.ただし量子化器利得の増加(積分器利得の減少)により雑音の影響が大きくなることや,量子化器のしきい値ばらつきの影響を考慮する必要が発生する可能性があるため,最適な設計指針を立てる必要がある.本研究では,以上の効果を考慮しつつ,量子化器利得を活用した設計方法の解明を行った.

### 4. 研究成果

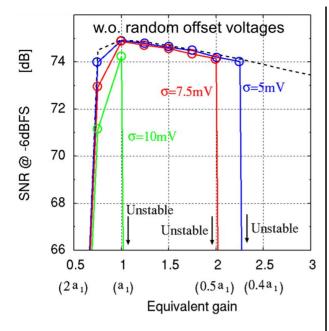

まず、信号帯域が 25MHz サンプリング周波数を 800MHz の変調器をターゲットとしたシステムレベル設計に関して解説を行う.今回の設計では CIFF 型 3 次の連続時間型デルタシグマ変調器を対象とした.8 レベルで判定が可能な量子化器を用いて検証を行った.積分器はアクティブ RC 積分器を想定し,内部のオペアンプのスイングレンジを 800mVpp とした.図 2 は、量子化器利得(Equivalent Gain)を 0.5 から 3 に変更した場合(積分器

図 2:量子化器利得(積分器利得) および SNR の関係()

利得もループゲインを一定にするために調 整)のSignal-to-Noise Ratio (SNR)を示し ている().変調器が発振した場合, Unstable (不安定動作)として判定した.実 線は3種類のしきい値ばらつきを有した際 の SNR を示している.量子化利得の増加に伴 い,初段積分器の帯域を削減することが可能 であるが,入力換算雑音の増加により SNR が 若干劣化していることが本結果から読み取 れる . 具体的には =5.0mV 程度では . 量子化 器利得を考慮しない場合に比べて,SNR が 0.9dB 程度の減少に引き替え,積分器利得を 半分以下に抑えられることが,シミュレーシ ョン検証により算出された.SNR の劣化量と 積分器に求められる要求仕様の緩和可能量 はトレードオフの関係になるが, SNR 劣化量 が許容できる程度で,量子化利得を増加する ことは,積分器の低消費電力化設計に繋がる.

次に,65nm CMOS プロセスを用いた連続時 間型デルタシグマ変調器の設計を行った.シ ステム設計では,上記に説明した方法を用い て,SNR の大幅な劣化を避けながら,初段の 積分器の帯域を抑えることを目標に行った . 帯域は 25MHz とし, サンプリング周波数 800MHz を実現するクロック源を用いた .ルー プフィルタの構成は,アクティブ RC 積分器 を用いた3次の連続時間型ループフィルタを 採用した.また量子化器レベルは8を採用し た.積分器にはスルーレートを増強する回路 構成を用いた.量子化器のしきい値とオペア ンプのトランジスタ数を可変にすることで, 傾向を確認することが出来た.本変調器は, 利得最適化以前と比べ,初段の積分器の消費 電力を削減出来る傾向にあることがトラン ジスタレベルのシミュレーションでも確認

が出来た.本成果は学会等を通して公表して いく予定である.

本課題期間に得られた研究成果は,3度の国内会議ならびに2度の国際会議での論文発表を通して,国内外に広めることが出来た今後の方針として,本デルタシグマ変調器を用いた更なる検証研究を引き続き進める予定である.

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# [学会発表](計5件)

Daisuke Kanemoto, and Makoto Ohki, A CT Delta-Sigma Modulator Design Technique with Equivalent Gain of Multi-bit ADC Having Random Offset Voltage due to Device Mismatch, 2015 IEEE/ACM Workshop on Variability Modeling and Characterization (VMC), 查読有, 2015年11月5日, Austin (USA), pp.1-2

<u>Daisuke Kanemoto</u>, Naoki Fukasawa, Takahide Sato, and Makoto Ohki, A 3rd Order Delta-Sigma Modulator Utilizing Equivalent Gain of Internal Multi-bit ADC, IEEE Symposium on Low-Power and High-Speed Chips COOL Chips XVIII, 査 読有, 2015 年 4 月 14 日, 横浜情報文化センター(神奈川県).Poster 18

兼本大輔,佐藤隆英,大木真,内部 A/D 変換器の等価ゲインを活用したデルタシグマ変調器,電気学会電子回路研究会資料,査読無,2014年12月19日,東京理科大学 森戸記念館(東京都),pp.71-75

兼本大輔,大木真,軽量脳波測定ヘッド ギアに用いる低消費電力デルタシグマ A/D 変換 LSI,日本生体医工学会 甲信越 支部大会,査読無,2014年10月18日, 山梨大学 山梨工業会館(山梨県),pp.41-42

兼本大輔, 佐藤隆英, 大木真, 内部 A/D 変換器の等価ゲインを活用したデルタシ グマ変調器設計, 電子情報通信学会 アナログ RF 研究会, 査読無, 2014 年 7 月 21 日, 屋久島環境文化村センター(鹿児島県)

〔その他〕 ホームページ等

山梨大学 大木兼本研究室 http://www.sp.es.yamanashi.ac.jp/~kanem oto/

# 6.研究組織

# (1)研究代表者

兼本 大輔 (KANEMOTO, Daisuke) 山梨大学·総合研究部·助教 研究者番号:90603332