# 科学研究費助成事業 研究成果報告書

平成 29 年 4 月 20 日現在

機関番号: 17401 研究種目: 若手研究(B) 研究期間: 2014~2016

課題番号: 26730028

研究課題名(和文)3次元FPGAアーキテクチャおよびその設計方式に関する研究

研究課題名(英文)Three dimensional FPGA architecture and its design method

#### 研究代表者

尼崎 太樹 (Amagasaki, Motoki)

熊本大学・大学院先端科学研究部(工)・助教

研究者番号:50467974

交付決定額(研究期間全体):(直接経費) 2,700,000円

研究成果の概要(和文): FPGA (Field Programmable Gate Array)を3次元積層した3D-FPGAは高集積,高速度の面で期待されている.しかしTSV (Through Silicon Via)は面積が大きいため,どこに幾つ使うかが重要である. TSVの数と面積,速度のパフォーマンスにはトレードオフが存在するため,本研究では3次元積層方式とアーキテクチャ探索ツールを研究開発した.アーキテクチャにおいては2層積層ではface-down方式,4層積層ではface-up方式を取りいれ,使用するTSVの数を限定する形で3次元積層が可能となった.また,これらの評価を行い面積,速度面での有効性を確認した.

研究成果の概要(英文): 3D FPGAs are expected to offer higher logic density, delay and low power by utilizing 3D integrated circuit technology. However, because TSVs for conventional 3D FPGA interlayer connections have a large area overhead, there is an inherent tradeoff between connectivity and small size. To find a balance between cost and performance, and to explore 3D FPGAs with realistic 3D integration processes, we propose two types of 3D FPGA and construct design tool sets for architecture exploration. In previous research, we created a TSV-free 3D FPGA with a face-down integration method; however, this was limited to two layers. In this study, we discuss the face-up stacking of several face-down stacked FPGAs. To minimize the number of TSVs, we placed TSVs peripheral to the FPGAs for 3D-FPGA with 4 layers. According to our results, a 2-layer 3D FPGA has reasonable performance when limiting the design to two layers, but a 4layer 3D FPGA is a better choice when area is emphasized.

研究分野: 計算機アーキテクチャ

キーワード: 3D-FPGA face-down face-up TSV

### 1.研究開始当初の背景

システムLSI はプロセス微細化により小型化,多機能化,高速化など高性能化を果たしてきた.しかし,22nm世代以降では微細化を阻む大きな障壁が二つ存在する.(1)微細化の弊害(配線遅延,漏れ電流の増大)により性能向上が見込めないこと,(2)チップ製造コストが増大することである.

これを受けて3次元積層技術がチップの高性能化や低価格化を牽引する手段として注目を浴びている.平面上に実装されたLSIをTSV(貫通ビア)を利用し縦方向に積層することで,機能そのままに小型化・高集積化が可能となる.

FPGA の高性能化は多品種少量生産が顕著なLSI業界において至上課題と言われてきた.FPGA の特徴である回路変更能力(柔軟性)により,HW アップデート,複数仕様への対応,バグ修正など多機能なLSI が実現可能となり多品種化を回避できる.一方で,現在の FPGA は柔軟性と性能間にトレードオフが存在しASIC の代替手段にはなりきれてない.そこで FPGA の3次元化(3D-FPGA)により柔軟性と性能の両立が可能となり,ASIC との性能差を打破できる可能性が生まれる.

#### 2.研究の目的

性能面では FPGA 自体の面積が大きい点 が課題となる.特にチップの大半を占める構 成メモリ量を減らすことが重要である.構成 メモリ量性能改善のためには LUT と同様の 表現能力を保ちつつ、小型かつ省構成メモリ な論理セル、およびそれを支援する CAD ツー ルが必要である、申請者は従来の LUT より も小型化・高速化を目指した論理セル,および 対応 CAD ツールの研究実績があるため,こ れらを基本に3次元FPGA用の設計環境を構 築する .他にも 3次元積層の点において TSV を初めとする垂直配線数は面積制約が大き く潤沢には使えない.定量的なアプローチで 垂直配線は最適化されるべきである.以上よ リ、本研究では3次元積層技術とFPGAを組 合わせることで高性能・高機能な 3D-FPGA を開発することを目的とし,論理セルアーキ テクチャ,3次元配線構造,CADツールの研 究開発を行う.

### 3.研究の方法

本研究では 3 次元積層技術と FPGA を組合わせることで高性能・高機能な 3D-FPGA を開発することを目的とし, (1)基本論理セルアーキテクチャの研究・開発, (2)3 次元配線構造の研究, (3)3D-FPGA 向け統合 CAD ツール開発に分割して研究を進めた.研究機関は3年であった.

初年度は 3D-FPGA を構成する論理セル,および配線構造の検討・評価を行うことでアーキテクチャベースの低消費電力化を目指た. 従来より提案していた SLM(Scalable Logic Module)アーキテクチャをベースに,テクノロジマッピングレベルで性能を改善できる 仕組みを明らかにした.

次年度は 3 次元積層方式の検討を行った. FPGA は論理部と配線部に大別される.それぞれを別レイヤで設計し,face-down 方式を用いて 3 次元積層することで TSV を一切必要としない 3D-FPGA アーキテクチャを明らかにした.また,集積度を向上させるためにface-downFPGA を 2 枚重ねることで 4 層で構成されたアーキテクチャの提案を行った.

最終年度は 3D-FPGA 向けの消費電力分析ツールの研究および開発を行った.これにより,電力面で従来の 2 次元 FPGA との比較評価が可能となった.

### 4.研究成果

(1) 小構成メモリ論理セル SLM およびテク ノロジマッピング手法

FPGA (Field Programmable Gate Array) の論理セルとして広く用いられている LUT (Look-Up Table) は任意の論理関数を実装 することが可能であるが,入力数に応じてメ モリのビット数が指数関数的に増加する. 我々は回路中に出現する論理関数の特徴に 着目し, 少メモリで論理関数を実装可能な SLM (Scalable Logic Module) アーキテクチ ャを提案している.SLM はシャノン展開を利 用した階層構造をとることで, 少構成メモリ 数で入力数の拡張が可能である反面,同入力 の LUT に比べ実装できる論理関数の種類に 制約があり、テクノロジマッピング後の論 理セル数が多くなる傾向がある. 本稿では SLM を対象としたテクノロジマッピング手 法として,LUT を対象としたマッピングアル ゴリズムをベースに,(a) 論理フィルタ,(b) 関数分解手法,(c) 論理フィルタ+関数分解 手法を適用する.その結果,(c) 論理フィル タ + 関数分解手法は , (a) 論理フィルタに対 し、論理セル数が8%改善された.

### (2)3 次元 FPGA 積層方式に関する研究

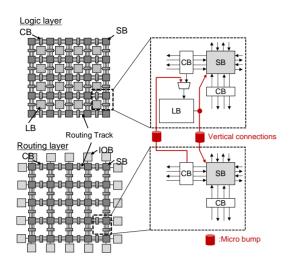

シリコンレイヤ間を接続する TSV や Micro Bump などの垂直配線は水平方向と面積オーバーヘッドが大きいため,レイヤ間接続を削減した3次元 FPGA アーキテクチャの検討が必要となる.本研究では,空間分散型と機能分散型の2方式を提案し評価を行った.図1に2層のウェハを用いて配線部と論理部を分離した FPGA 構成を示す.チップ間の接続はロジックブロックの入出力部に限定される.さらに,積層方式として face-down を用いているため,レイヤ間の接続に TSV は不要である.

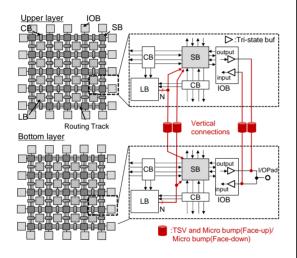

この結果,層数を2に限定した場合ではface-down 方式の機能分散型 FPGA の性能が最も良いことがわかった.2層以上の積層においては,face-down 積層 FPGAを2枚用いた4層 FPGAの提案を行い(図2),2D-FPGAと比較して約60%程度の面積削減が可能であった.

図 1. Face-down 積層による接続方式

図 2. Face-down FPGA を 2 枚用いた 4 レイヤ 積層方式

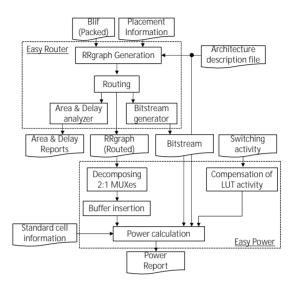

(3)3D-FPGA 向け消費電力解析ツール FPFA アーキテクチャ探索時には,微細な プロセスでは動作速度の向上や

リーク電力などにより,低消費電力な設計が 求められている.しかし,既存の消費電力解 析ツールでは 3 次元 FPGA に対応しておらず アーキテクチャの探索への適用が難しい. 我々の研究グループでは任意の配線トポロ ジに対応可能な配置ツール Easy Router を開 発している.Easy Router はソースコードが C#で書かれており,アーキテクチャ情報も同 様に C#で記載する. Easy Router では定義し たアーキテクチャを RR(Routing Resource) グラフとして表現することで配線を行う.そ こで Easy Router と連携して消費電力解析を 行う Easy Power の開発を行った . Easy Power では Easy Router が出力する RR グラフを利 用することでノードを構成する回路と配線 容量を扱うことができる(図3).これに,ス タンダードセルの電力情報を用いて電力を 算出する.本ツールの精度は商用ツール Power Compiler と比較して10%以内の誤差精度であった.本ツールを用いて評価を行い, 2層の FPGA は面積,電力面で2次元の FPGA よりも優れることがわかった.また,面積を 重視する場合は4層で構成された FPGA が有 利であることがわかった.

図 3. 消費電力ツール EasyPower の機能ブロック図

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

### [雑誌論文](計 3件)

[1]M.Amagasaki, Q.Zhao, M.Iida, M.Kuga and T.Sueyoshi, `` A 3D FPGA Architecture to Realize Simple Die Stacking", IPSJ Transactions on System LSI Design Methodology, Vol.8, pp.116-122, Aug. 2015.

[2]M.Amagasaki, M.Iida, M.Kuga and T.Sueyoshi, `FPGA PLACEMENT BASED ON SELF-ORGANIZING MAP", International Journal of Innovative Computing, Information and Control, Vol.11, No.6, pp.2001-2012, Dec. 2015.

[3] M.Amagasaki, R.Araki, M.Iida and T.Sueyoshi, ``SLM: A Scalable Logic Module Architecture with Less Configuration Memory", IEICE Transactions Fundamentals of Electronics, Communications and Computer Sciences, Vol.E99-A, No.12, pp.2500-2506, Dec. 2016.

## [学会発表](計 10件)

[1]Q.Zhao, K.Yanagida, <u>M.Amagasaki</u>, M.Iida, M.Kuga and T.Sueyoshi,

`` A Logic Cell Architecture Exploiting

the Shannon Expansion for the Reduction of Configuration Memory, ''Proc. 24th International Conference on Field Programmable Logic and Applications (FPL2014), T2a-3, Munich, Germany, Sep. 2014.

[2]T.Kajiwara, Q.Zhao. M.Amagasaki, M. Iida, M. Kuga and T. Sueyoshi, Three-dimensional Nove I **FPGA** Architecture with High-speed Serial Communication Links, ''Proc. International Conference on Field Technology(ICFPT2014), Programmable pp.306-309, shanghai, China, Dec. 2014.

[3]梶原拓也, <u>尼崎太樹</u>, 飯田全広, 久我守弘, 末吉敏則, ``高速シリアル通信を用いた3次元FPGAの検討,''信学技報 RECONF2014-7, vol.114, no.75, pp.31-36, June 2014.

[4]趙 謙, <u>尼崎太樹</u>, 飯田全広, 久我守弘, 末吉敏則, ``レイヤ間接続を削減した3次元 FPGA アーキテクチャの検討, ''信学技報 RECONF2014-53, vol.114, no.428, pp.41-46, Jan. 2015.

- [5] M.Amagasaki, Q.Zhao, M.Iida, M.Kuga and T.Sueyoshi, ``A CONFIGURATION MEMORY REDUCED PROGRAMMABLE LOGIC CELL, ''Proc. of IEEE Symposium on COOL Chips XVIII, Session IV-6, Apr. 2015.

- [6] M.Amagasaki, Q.Zhao, M.Iida, M.Kuga and T.Sueyoshi, ``Simple Wafer Stacking 3D-FPGA Architecture,''Proc. of the 2015 IEEE International Conference on Integrated Circuit Design and Technology (ICICDT), K-3, June 2015.

- [7] M.Amagasaki, Y.Takeuchi, Q.Zhao, M.Iida, M.Kuga and T.Sueyoshi, ``Architecture Exploration of 3D FPGA to minimize internal layer connection,''Proc. of IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), pp.110-115, Oct. 2015.

- [8] 竹内悠登 ,趙 謙 , <u>尼崎太樹</u> ,飯田全広 , 久我守弘 , 末吉敏則 ` 高速シリアル通信機構をもつ 3 次元 FPGA の面積最適化 , ''信学技報 RECONF2015-4 , vol.115 , no.109 , pp17-22 , Jun. 2015.

- [9] 荒木 亮,飯田全広,<u>尼崎太樹</u>,久我守弘,末吉敏則、少構成メモリ論理セル SLM向けテクノロジマッピング手法の検討,''信学技報 RECONF2015-27, vol.115, no.109, pp147-152, Jun. 2015.

[10] 池邊雅登,趙 謙,<u>尼崎太樹</u>,飯田全広,久我守弘,末吉敏則 、、3次元 FPGA 向け消費電力解析ツール,''

3 次元 FPGA 向け消貨電力解析ツール, 信学技報 RECONF2016-46, vol.116, no.332, pp35-40, Nov. 2016.

### [その他]

研究成果公開(研究室 HP)

http://www.arch.cs.kumamoto-u.ac.jp

## 6. 研究組織

### (1)研究代表者

尼崎 太樹 (Motoki Amagasaki) 熊本大学・大学院先端科学研究部・助教 研究者番号:50467974