## 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 14 日現在

機関番号: 10101

研究種目: 新学術領域研究(研究領域提案型)

研究期間: 2013~2017

課題番号: 25110015

研究課題名(和文)粗粒デバイスのための新規情報処理アーキテクチャの開拓

研究課題名(英文)Novel Information Processing Architectures for Coarse-Grained Devices

#### 研究代表者

浅井 哲也 (Asai, Tetsuya)

北海道大学・情報科学研究科・教授

研究者番号:00312380

交付決定額(研究期間全体):(直接経費) 53,800,000円

研究成果の概要(和文):分子ネットワークのゆらぎを利活用する計算アルゴリズムおよびアーキテクチャの開拓を行った。神経素子に類似したスパイクを発生する分子ネットワークのモデルを構築し、そのダイナミクスを用いて「リザーバ計算」の学習評価を行った。その結果、一般的に用いられる時系列データセットを高い精度で学習できることが明らかになり、リザーバ計算の有効性が確認できた。この計算を現実の系で再現するためには、リザーバ計算の初期値依存性とダイナミクス再現性の問題を解決する必要がある。この問題に対し、各試行毎に外部から同じ雑音を印加することで、リザーバの初期値に依存せずに同じ複雑ダイナミクスを生成できることが明らかになった。

研究成果の概要(英文): Novel computing methods and architectures were constructed for coarse-grained molecular devices and materials that utilize noise and fluctuations. The following two computing methods were developed. A cellular-automaton model that imitates neuromorphic spike generation in a molecular spiking neural networks was developed. By using dynamics of the model, performance of 'reservoir computing' was evaluated by using standard benchmarks for memorizing complex temporal sequences. The results showed that the model was able to learn complex temporal sequences at high precision. For the physical demonstration, one had to resolve two issues, i.e., reservoir's initial-value dependence and difficulty in reproduction of complex temporal sequences. To resolve this problem, a nonlinear phenomena, called consistency, was introduced in the reservoir, which resulted in successful generation of initial-value independent and reproductive complex temporal sequences.

研究分野: 集積回路工学

キーワード: 粗粒素子 ゆらぎ 分子ネットワーク リザーバ計算 コンシステンシ セルオートマトン

#### 1. 研究開始当初の背景

現代の汎用情報処理プロセッサは CMOS 素 子の微細化により発展してきた。その基本方 針は、ゆらぎ(素子バラツキや配線遅延バラ ツキ、クロストークノイズなど)の要素を極 力排除するというものである。しかし、量子 限界を目前とした現在、ゆらぎを排除して情 報処理プロセッサを設計するアプローチは破 綻を迎える一歩手前にあり、それを打破する 新アーキテクチャの創出が急務である(国際 半導体ロードマップ委員会 (ITRS) の 2012 年の予測による)。一方、脳はゆらぎを排除せ ず、むしろ積極的に利用して情報処理を行う ことがよく知られている。神経細胞やそれら を繋ぐシナプスなどの脳の構成要素は粗粒素 子である(精度、バラツキ、応答速度、クロス トークなど、あらゆる点で半導体素子に劣る)。 研究代表者はこれまで、高精度な半導体素子 を用いなくても、神経細胞などと同程度の粒 度を持ち、かつその機能を模する素子が実現 できれば、脳の機能を模する情報処理システ ムを構築できることを示してきた。すべての 脳機能を創り出すことはまだ難しいと思われ るが、現在明らかになっている脳の一部機能 を現代の情報処理プロセッサに組み込むこと で、低コスト・極低電力・環境にやさしい情報 処理システムが構築できると期待されている。 しかし、その設計手法・学問(粗粒素子のため の回路・システムアーキテクトニクス) は確 立されておらず、半導体素子の量子限界を目 前とした今、このような新学術領域の樹立お よびその浸透が急務であった。

#### 2. 研究の目的

粗粒デバイスを演算要素として持つ新規情報 処理アーキテクチャ設計学(粗粒素子アーキ テクトニクス)の開拓を本研究の目的とする。 粗粒デバイス(coarse-grained device)とは、 特性バラツキやゆらぎ(曖昧さ)を持つデバイスのことを指し、分子ナノデバイス,量子 限界目前のナノ半導体デバイス,極低電圧デバイスなどがこれに該当する。

### 3. 研究の方法

全研究期間にわたり、班間ミーティングを年に数回設けて情報交換と技術交流を図り、分子アーキテクト領域の一つの柱として機能するよう、班内連携を強化してゆくかたちで研究を遂行した。

## (1) <u>粗粒素子の回路応用の基礎となるアーキ</u> テクチャ設計学の確立

研究代表者の発案による「ゆらぎを利用する脳型アーキテクチャ」と「確率共鳴ゲート」を大規模化して回路応用につなげるためには、A01-03 班の粗粒分子素子の粒度を考慮しながら、系統立てて回路設計ができるような設計基盤を整える必要があった。そのために、分子素子の電子素子としての特性テーブルを作製し、過去に提案した脳型情報処理の一つ一確率共鳴現象一を応用し、粗粒素子アーキテ

クチャの基礎となる回路設計学を確立する方 法をとった。

## (2) <u>分子粗粒素子と同程度の粒度を持つ CMOS</u> による回路動作の実証

分子粗粒素子をいきなり回路に組み込むことは難しいと思われたため、作成・制御が容易な CMOS 回路 (分子粗粒素子の等価回路)を試作して回路動作の実証を行った。具体的には、CMOS 回路の電源電圧を極限まで下げた状態(素子ゆらぎがあわられる状態)での電力評価、安定性評価を行った。なお、シミュレーションのみでは実世界のゆらぎを取り入れた実評価ができないため、CMOS 回路の試作を要素回路毎に行う必要があった。

## (3) 確率共鳴ゲートを用いた非同期式論理回路の設計手法の確立

確率共鳴ゲートは出力の確定タイミングが確率的であるため、現在主流の(設計が容易な)同期式回路を設計できない。よって、回路のアーキテクチャを非同期にした。そのために、粗粒素子を用いて非同期回路を設計するための新しい手法の確立が必要であった。確率共鳴ゲートを用いた冗長論理を構成することで、誤動作を抑制できるという見込みのもと研究を遂行した。

## (4) <u>単一分子素子(粗粒素子)を用いた確率共</u>鳴ゲートの要素回路設計

研究分担者の専門分野である単一電子回路技術をもとに、確率共鳴ゲートの要素回路設計と検証を行った。クーロンブロッケードに基づく単一電子回路の設計・シミュレーション技法は単一分子素子にも適用可能であり、これまでの知見を活かして確率共鳴ゲートの分子モデルを作出した。具体的には、過去に構築した単電子ニューロンのネットワークまたは単電子箱を用いて確率共鳴ゲート回路を構成し、単一分子素子回路へ応用した。

## (5) <u>ゆらぎを利用する脳型情報処理の新規開</u> 拓

脳の情報処理は研究代表者のみで解明できるものではなく、これまでも神経生理学者、神経計算科学者などの協力のもと、発見された新現象を「回路応用」の観点から解釈し、役に立つ機能を抽出したうえで回路設計を行ってきた。本研究においても、これまで同様、有用と思われる新現象については積極的に回路に取り入れて粗粒分子素子回路に反映させる方針で研究を遂行した。

## 4. 研究成果

#### (1) ゆらぎを利用した論理ゲートの確立

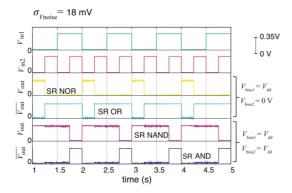

自然界や生体にみられる「確率共鳴」とよばれるゆらぎ利用現象に着目し、その仕組みを取り入れた基本ディジタル素子「ゆらぎ利用論理ゲート」を提案した。このゲートの論理はしきい論理に基づいて構築されるが、しきい値がゆらぐと、一般的には正しい論理動作が期待できない。しかし、生物の仕組みに学んでしきい素子にダイナミクス(ヒステリシ

ス)を持たせると、素子バラツキによりしきい 論理が正しく動作しない場合でも、しきい値 にゆらぎを与えることで安定して正しい論理 動作ができることが明らかになった。これに よって、素子バラツキが顕著になる程度まで 電源電圧を下げても正しく動作する低電力論 理ゲートが実現可能になる。その理論を構築 し、数値シミュレーションおよび試作回路上 でその動作を実証した(図 1)。

図1: ゆらぎ利用論理ゲートの実験結果。

# (2) ゆらぎ利用論理ゲートを用いた非同期ディジタル情報処理システムの構築

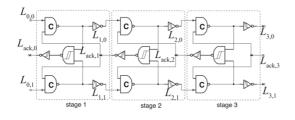

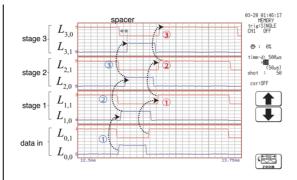

上記(1)で提唱・実証した「ゆらぎ利用論理ゲ ート」を組み合わせた大規模情報処理に向け た基本アーキテクチャを提唱し、その理論解 析と実機による評価結果を示し、極低電力で 動作する計算システムの設計手法を確立した。 提唱したゆらぎ利用論理ゲートは、素子バラ ツキによりしきい論理が正しく動作しない場 合でも、しきい値にゆらぎを与えることで安 定して正しい論理動作ができるというもので あるが、与えたゆらぎに起因する「論理出力 値の確定時間」にゆらぎが発生するため、同 期式のディジタルアーキテクチャには不向き である。そこで、論理出力値の確定時間に無 頓着な「ゆらぎ利用論理ゲートのための非同 期式ディジタル演算システムの設計理論」を 提唱・構築した(図2)。提案した設計法によ って、素子バラツキが顕著になる程度まで電 源電圧を下げても動作する低電力・非同期デ ィジタル情報処理システムの構築が可能にな る。数値シミュレーションおよび試作回路上 でその基本動作を実証した(図3)。

図2: ゆらぎ利用論理ゲートの3段パイプライン構造。

図3:ゆらぎ利用論理ゲートの3段パイプライン動作(実験結果)。

### (3) ゆらぎを利用した伝送回路の構築

神経軸索はゆらぎを有効利用して雑音環境下 での神経パルスの伝搬を加速させている。神 経軸索は神経膜により構成され、神経膜の内 部ポテンシャル(膜電位)に応じてスパイク (パルス)を発生する。神経軸索は軸索外部か ら雑音を受けるが、神経膜が休止状態にある とき(膜電位が低い場合)には雑音の感受性が 低く、神経膜が活動状態にあるとき(膜電位が 高い・上昇中の場合)には雑音の感受性が高く なることが知られている。よって、神経軸索 上をスパイクが伝搬している状況において、 ゆらぎや欠損によりスパイクの伝搬が阻害さ れるような状況であっても、スパイク伝搬に よる膜電位の増加が雑音の感受性を上げて、 雑音がスパイク伝搬をアシストできるように なる。この仕組みを電子回路モデルに取り込 んでアクティブ伝送回路を構築し、素子バラ ツキや欠損がある場合でも、雑音を利用して 伝送回路上をパルスが伝搬できることを示し た。具体的には、バラツキの大きな抵抗アレ イと、神経軸索の回路モデルの一つである Maeda-Makino ニューロンの 1 次元アレイを結 合してアクティブ伝送回路を構築し、この回 路上のパルス伝搬特性を調べた。回路シミュ レーションおよび実回路の実験の結果、雑音 強度がしきい値以上であればスパイク伝送率 はほぼ一定となること、および抵抗アレイの 抵抗の平均値とスパイク伝送率の間に確率共 鳴カーブが見られることが明らかになった。

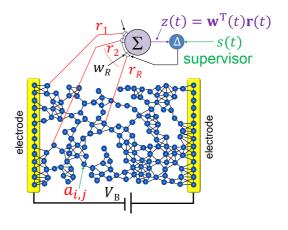

図4: POM/SWNT 分子ネットワークモデル。

### (4) POM/SWNT ランダム分子ネットワークのモ デル構築とリザーバ計算機への応用

粗粒素子の集団のバラツキは制御せず、外側の機構において粗粒素子集団のバラツキの特性を活かした機械学習を行うことで機能を発現させる、という考えを導入した。そのためにまず、神経素子に類似したスパイクを発生する POM/SWNT 分子ネットワークのセルオートマトンモデルを構築した(図4)。

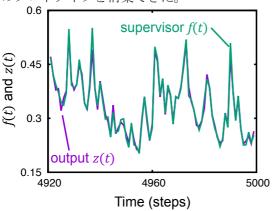

このモデルはターゲットとする分子ネット ワークの重要な性質(スパイク生成、および NDR 特性)をうまく再現する。このモデルのダ イナミクスを用いて「リザーバ計算」と呼ば れる脳型計算アルゴリズムの一つに着目して 時系列の学習評価を行ったところ、リザーバ 計算の評価において一般的に用いられる時系 列データセット(時間依存性のある時系列デ ータ)を高い精度で学習できることが明らか になり、リザーバ計算の有効性が確認できた (図5)。この計算を現実の系で再現するため には、リザーバ計算の初期値依存性とダイナ ミクス再現性の問題を解決する必要がある。 つまり、リザーバ計算のために高い精度で試 行毎に同じ複雑ダイナミクスを生成する必要 があった。この問題に対し、コンシステンシ と呼ばれる非線形現象を利用して、試行毎に 外部から同じ雑音を印加することで、リザー バの初期値に依存せずに同じ複雑ダイナミク スを生成できることが明らかになった。以上 より、複雑分子ネットワークの構造・ダイナ ミクスを生かした脳型計算機アーキテクチャ のプロトタイプを構築できた。

図5: NARMA10 時系列(supervisor)の学習と 再生結果(output)。

## 5. 主な発表論文等 〔雑誌論文(抜粋)〕(計 24 件)

- [1] Tanaka H., Akai-Kasaya M., Termeh Yousefi A., Hong L., Fu L., Tamukoh H., Tanaka D., <u>Asai T.</u>, and Ogawa T., "A molecular neuromorphic network device consisting of single-walled carbon nanotubes complexed with polyoxometalate," Nature Communications, 2018, in press. (查読有)

- [2] Tanibata A., Schmid A., Takamaeda

- Yamazaki S., Ikebe M., Motomura M., and <u>Asai T.</u>, "Proto-computing architecture over a digital medium aiming at real-time video processing," Complexity, vol. 2018, pp. 3618621-1-11 (2018). (查読有)

- [3] <u>浅井 哲也</u>, "人工知能のシンギュラリティ到 達を加速する情報科学とものづくりの融合 研究にむけて," 超精密, vol. 23, no. 1, pp. 4-7 (2017). (査読無)

- [4] Hida I., Takamaeda-Yamazaki S., Ikebe M., Motomura M., and <u>Asai T.</u>, "An energy-efficient dynamic branch predictor with a two-clock-cycle naive Bayes classifier for pipelined RISC microprocessors," Nonlinear Theory and Its Applications, vol. E8-N, no. 3, pp. 235-245 (2017). (查読有)

- [5] Hida I., Takamaeda-Yamazaki S., Ikebe M., Motomura M., and <u>Asai T.</u>, "A high performance and energy efficient microprocessor with a novel restricted dynamically reconfigurable accelerator," Circuits and Systems, vol. 8, no. 5, pp. 134-147 (2017). (查読有)

- [6] Marukame T., Ueyoshi K., <u>Asai T.</u>, Motomura M., Schmid A., Suzuki M., Higashi Y., and Mitani Y., "Error tolerance analysis of deep learning hardware using restricted Boltzmann machine towards low-power memory implementation," IEEE Transactions on Circuits and Systems II, vol. 64, no. 4, pp. 462-466 (2017). (查読有)

- [7] Satomi K. and <u>Oya T.</u>, "Design of Slime-Mold-Inspired Multi-Layered Single-Electron Circuit," International Journal of Parallel, Emergent and Distributed Systems, (2017), in press. (查読有)

- [8] Tanabe T. and <u>Oya T.</u>, "Study of Singleelectron Information-processing Circuit Mimicking Foraging Behavior of Honeybee Swarm," Japanese Journal of Applied Physics, vol. 56, 06GF13, (2017). (查読有)

- [9] Ueyoshi K., Marukame T., <u>Asai T.</u>, Motomura M., and Schmid A., "FPGA implementation of a scalable and highly parallel architecture for restricted Boltzmann machines," Circuits and Systems, vol. 7, no. 9, pp. 2132-2141 (2016). (查読有)

- [10] Ueyoshi K., Marukame T., <u>Asai T.</u>, Motomura M., and Schmid A., "Robustness of hardware oriented restricted Boltzmann machines in deep belief networks for reliable processing," Nonlinear Theory and Its Applications, vol. E7-N, no. 3, pp. 395-406 (2016). (查読有)

- [11] Ushida M., Schmid A., <u>Asai T.</u>, Ishimura K., and Motomura M., "Motion vector estimation of textureless objects exploiting reaction-diffusion cellular automata," International Journal of Unconventional

- Computing, vol. 12, no. 2-3, pp. 169-187 (2016). (査読有)

- [12] Prati E., Giussani E., Ferrari G., and <u>Asai</u> <u>T.</u>, "Noise-assisted transmission of spikes in Maeda-Makino artificial neuron arrays," International Journal of Parallel, Emergent and Distributed Systems, vol. 32, no. 3, pp. 278-286 (2016). (查読有)

- [13] Takano M., <u>Asai T.</u>, and <u>Oya T.</u>, "Design and evaluation of single-electron associative memory circuit," International Journal of Parallel, Emergent and Distributed Systems, vol. 32, no. 3, pp. 259-270 (2016). (查読有)

- [14] Ishimura K., Schmid A., <u>Asai T.</u>, and Motomura M., "Stochastic resonance induced by internal noise in a unidirectional network of excitable FitzHugh-Nagumo neurons," Nonlinear Theory and Its Applications, vol. 7, no. 2, pp. 164-175 (2016). (查読有)

- [15] Nakada K., Miura K., and Asai T.,

"Dynamical systems design of silicon

neurons using phase reduction method,"

Nonlinear Theory and Its Applications, vol.

7, no. 2, pp. 95-109 (2016). (查読有)

- [16] Shirata K., Inden Y., Kasai S., <u>Oya T.</u>, Hagiwara Y., Kaeriyama S., and Nakamura H., "Robust myoelectric signal detection based on stochastic resonance using multiple-surface-electrode array made of carbon nanotube composite paper," Japanese Journal of Applied Physics, vol. 55, 04EM07(5 pages), (2016). (查読有)

- [17] Hirashima R. and Oya T., "Design of Thermal-Noise-Harnessing Single-Electron Circuit for Efficient Signal Propagation," Japanese Journal of Applied Physics, vol. 55, 06GG10, (2016). (查読有)

- [18] (解説記事) <u>浅井 哲也</u>, "ニューロモルフィック工学・脳型機械学習ハードウェアの行方," 日本神経回路学会誌, vol. 22, no. 4, pp. 162-169 (2015). (査読有)

- [19] El-Sankary K., <u>Asai T.</u>, Kuroda T., and Motomura M., "Crosstalk rejection in 3D-stacked inter-chip communication with blind source separation," IEEE Transactions on Circuits and Systems II, vol. 62, no. 8, pp. 726-730 (2015). (查読有)

- [20] Ishimura K., Komuro K., Schmid A., Asai <u>T.</u>, and Motomura M., "FPGA implementation of hardware-oriented reaction-diffusion cellular automata models," Nonlinear Theory and Its Applications, vol. 6, no. 2, pp. 252-262 (2015).(査読有)

- [21] Gonzalez-Carabarin L., <u>Asai T.</u>, and Motomura M., "Application of nonlinear systems for designing low-power logic gates based on stochastic resonance," Nonlinear

- Theory and Its Applications, vol. 5, no. 4, pp. 445-455 (2014). (査読有)

- [22] Ishimura K., Komuro K., Schmid A., <u>Asai</u> <u>T.</u>, and Motomura M., "Image steganography based on reaction diffusion models toward hardware implementation," Nonlinear Theory and Its Applications, vol. 5, no. 4, pp. 456-465 (2014). (查読有)

- [23] Gonzalez-Carabarin L., <u>Asai T.</u>, and Motomura M., "Low-power asynchronous digital pipeline based on mismatch-tolerant logic gates," IEICE Electronics Express, vol. 11, no. 15, pp. 20140632/1-9 (2014). (查読有)

- [24] Shinde Y. and <u>Oya T.</u>, "Design of Single-Electron "Slime Mold" Circuit and Its Application to Solving Optimal Path Planning Problem," Nonlinear Theory and Its Applications, IEICE, vol. 5, no. 1, pp. 80-88 (2014). (查読有)

#### 〔学会発表(抜粋)〕(計22件)

- [1] <u>浅井 哲也</u>, "ニューロモルフィックハードウェアの過去と現在および可能性のある未来像," 第 65 回応用物理学会春季講演会シンポジウム「ニューロモルフィックハードウェアとはどんなものだろうか」, Waseda University, Tokyo, Japan (Mar. 17-20, 2018).

- [2] <u>浅井 哲也</u>, "三次元ニューラルネットワーク デバイスの実現に向けた材料・デバイス・回 路技術," 東北大学電気通信研究所「新規固体 デバイス・回路を用いた脳型コンピューティ ングに関する研究」共同プロジェクト研究会, Tohoku University, Sendai, Japan (Dec. 26, 2017).

- [3] Asai T., "Emerging research architectures for brain-morphic AI," SNU-HU 2017 International Workshop on New Frontiers in Convergence Science and Technology, Seoul National University, Seoul, Korea (Nov. 24, 2017)..

- [4] <u>浅井 哲也</u>, "ニューラルネットワーク集積回 路概論," 「NEDO IoT 推進のための横断技術 開発プロジェクト」第 2 回人材育成スクール, Waseda University, Tokyo, Japan (Oct. 10, 2017).

- [5] <u>Asai T.</u>, "More-than-Neumann and beyond-Neumann architectures," International Conference on Solid State Devices and Materials, Sendai International Center, Sendai, Japan (Sep. 19-22, 2017).

- [6] <u>浅井 哲也</u>, "情報科学とデバイス・ものづくり融合研究による人工知能のシンギュラリティ到達加速," 富士通研究所専門技術講座, FUJITSU Laboratories Atsugi Office, Atsugi, Japan (Jul. 25, 2017).

- [7] <u>浅井 哲也</u>, "AI のハードウェア: イントロダ クション," 日本学術振興会 151 委員会研究 会, RIKEN, Wako, Japan (Jul. 10, 2017).

- [8] <u>浅井 哲也</u>, "ニューラルネットワーク集積回路概論," 「NEDO IoT 推進のための横断技術開発プロジェクト」第1回人材育成スクール, AIST, Tsukuba, Japan (Feb. 24, 2017).

- [9] <u>浅井 哲也</u>, "ニューラルネットワーク集積回路の概要 ~歴史と流派、近年の動向と可能性のある未来~," 超精密加工専門委員会第70 回研究会, Mielparque Osaka, Osaka, Japan (Dec. 16, 2016).

- [10] Asai T., "Cognitive motion processing in imager/neural processor 3D stacked systems," 2016 HU/SNU Joint Symposium / International Workshop on New Frontiers in Convergence Science and Technology, Hokkaido University, Sapporo, Japan (Nov. 24-25, 2016).

- [11] Asai T., Ikebe M., and Motomura M., "Cognitive motion processing in imager/neural processor 3D stacked systems," The 5th Japan-Korea Joint Workshop on Complex Communication Sciences, Pukyong National University, Busan, Korea (Oct. 20-23, 2016).

- [12] <u>浅井 哲也</u>, "学習型ハードウェアとその応用・発展の展望," 第9回情報ネットワーク科学研究会, Tokyo Metropolitan University, Tokyo, Japan (May 27, 2016).

- [13] Asai T., "Machine learning systems on FPGA/VLSI and their potential applications," CiNet Friday Lunch Seminar, NICT, Suita, Japan (Nov. 27, 2015).

- [14] <u>浅井 哲也</u>, "ニューロチップ概要 ~歴史と 流派、現在の動向と可能性のある未来~," STARCアドバンストセミナー ニューロチッ プ 1~概要/回路アーキテクチャ~, 川崎市 産業振興会館, Tokyo, Japan (Nov. 6, 2015).

- [15] <u>浅井 哲也</u>, "FPGA と人工ニューラルネット," 第25回 日本神経回路学会 全国大会 企画シンポジウム~高性能計算技術が加速する脳神経回路シミュレーション~, The University of Electro-Communications , Tokyo, Japan (Sep. 2-4, 2015).

- [16] Oya T. and <u>Asai T.</u>, "Emerging computation on single electron circuits and devices," The 3rd Bilateral Italy-Japan Seminar of Silicon Nanoelectronics for Advanced Applications, Campus Plaza Kyoto, Japan (Jun. 17, 2015).

- [17] <u>浅井 哲也</u>、"機械学習のデジタル実装と応用," 東北大学電気通信研究所 ブレインウェア工学研究会, Tohoku University, Sendai, Japan (Apr. 28, 2015).

- [18] <u>浅井 哲也</u>, "セルオートマトンの集積回路化 とその技術動向," 明治大学先端数理科学イ ンスティテュート現象数理学研究拠点研究 集会「セルオートマトンが拓く現象数理学」, Meiji University, Tokyo, Japan (Dec. 4-5, 2014).

- [19] Asai T., "A Memristor --- the Fourth Fundamental Circuit Element--- and its Application to Unconventional Computation," The 6th IEEE International Nanoelectronics Conference 2014, Hokkaido University, Japan (Jul. 28-31, 2014).

- [20] Asai T., "Trends in neuromorphic enginnering towards nanoelectronic brain machines," The 10th International Nanotechnology Conference on Communication and Cooperation, NIST, Maryland, U.S.A. (May 13-16, 2014).

- [21] <u>浅井 哲也</u>, 品田 高宏, 辰村 光介, 屋上 公二郎, "ERD 動向と ERD のための Emerging アーキテクチャ," 2013 年度 STRJ ワークショップ, Kokuyo Hall, Tokyo, Japan (Mar. 7, 2014).

- [22] <u>Asai T.</u>, "Noise-driven computing for CMOS and coarse-grained devices," Open seminar at Faculty of Information Technology and Bionics, Pazmany Peter Catholic University, Peter Pazmany Catholic University, Hungary (Oct. 11, 2013).

#### [図書] (計3件)

- [1] Oya T. and Asai T., "Emerging computations on nano-electronic circuits and devices," Molecular Architectonics: The Third Stage of Single Molecule Electronics, Ogawa T., Ed., Springer, New York (2016).

- [2] <u>Asai T.</u> and Peper F., "Explorations in Morphic Architectures," Emerging Nanoelectronic Devices, Chen A., Hutchby J., ZhirnovV, and Bourianoff G., Eds, Wiley, New Jersey (2015).

- [3] <u>Asai T.</u>, "Memristor-CMOS hybrid synaptic devices exhibiting spike-timing dependent plasticity," VLSI: Circuits for Emerging Applications, Wojcicki T. and Iniewski I., Eds., CRC Press (2014).

## [産業財産権]

○出願状況(計1件)

名称:重み符号固定学習装置

発明者:浅井 哲也 権利者:浅井 哲也 番号:特願 2017-048421 出願年月日:2017 年 3 月 14 日

国内外の別:国内

○取得状況(計0件)

### [その他]

ホームページ等

- [1] http://molarch.jp

- [2] http://lalsie.ist.hokudai.ac.jp/~asai/

- 6. 研究組織

- (1)研究代表者

浅井 哲也 (ASAI TETSUYA) 北海道大学・大学院情報科学研究科・教授 研究者番号:00312380

(2)研究分担者

大矢 剛嗣 (OYA TAKAHIDE) 横浜国立大学・工学研究院・准教授 研究者番号:30432066

- (3)連携研究者 なし

- (4)研究協力者 なし