#### 研究成果報告書 科学研究費助成事業

今和 元 年 6 月 1 9 日現在

機関番号: 10101 研究種目: 若手研究(A) 研究期間: 2016~2018

課題番号: 16H06080

研究課題名(和文) | V族/ | | | - V族へテロ接合の界面欠陥制御に基づく低電圧スイッチ素子の回路応用

研究課題名(英文) Research on tunnel FET using IV/III-V heterojunction toward circuit application

#### 研究代表者

冨岡 克広 (Tomioka, Katsuhiro)

北海道大学・情報科学研究科・准教授

研究者番号:60519411

交付決定額(研究期間全体):(直接経費) 19,200,000円

研究成果の概要(和文):次世代エレクトロニクスの新しいスイッチ素子として、トンネルFET素子が注目されている。これは、従来のFETでは実現できない低消費電力性能を有しているためである。本研究では、トンネルFET素子研究について、新しいヘテロ接合によるトンネル接合の形成技術・欠陥制御技術の確立を基軸として、素子の高性能化技術の確立、回路応用へと展開を図る相補スイッチング構造を新しく提案・実証した。

研究成果の学術的意義や社会的意義 トンネルFETは、あらゆるエレクトロニクスの消費電力を9割以上削減できる潜在性を有した次世代スイッチ素子 である。本研究では、この素子の新しい構造・接合を代表者独自のナノ構造形成技術を基軸に提案し、接合界面の欠陥制御技術に着目することで、消費電力を9割以上削減へ向けた課題を解決する新しい素子構造の提案と基盤技術を確立し、高性能化を実証した。これにより、次世代エレクトロニクスの消費電力を抜本的に削減する技術を提供する。

研究成果の概要(英文): Tunneling Field-Effect Transistors (TFET) have been attracted much attention as a building-blocks for future nanoelectronics because of their low-power consumption with high performance. In this research, we proposed new technologies for current boosting and complementary switching operation by controlling the defects at new Si/III-V nanowire heterojunctions in planar structure, and demonstrated state-of-the-art TFET architectures with steep subthreshold slope and high conductivity.

研究分野: 半導体結晶成長、半導体量子構造、半導体デバイス

キーワード: 半導体ナノ構造 薄膜成長 ナノワイヤ材料 半導体デバイス ダイオード トランジスタ

## 1. 研究開始当初の背景

半導体エレクトロニクスの中核を担う次世代大規模集積回路(LSI)技術は、性能向上とともに低消費電力駆動を実現しなければならない。LSIの低消費電力化は、電界効果トランジスタ (FET)の駆動電圧の低減が最も有効である。回路の消費電力は、FETの駆動電圧の2乗に比例するが、サブスレッショルド係数(SS)に物理的な最小限界(SS ~ 60 mV/桁)があるため、駆動電圧を下げることが困難である。そのため、この物理限界を回避し、60 mV/桁以下の急峻な SS 特性を実現できるスイッチ素子の開発が急務となっている。SS=30 mV/桁を達成した場合、駆動電圧は半減し、回路全体の消費電力の 80%以上削減できる可能性がある。スイッチ機構は、トンネル輸送、インパクトイオン化や負性ゲート容量などがある。中でも、トンネル FET は、CMOS 技術の整合性から、次世代低電圧スイッチ素子として期待されている。しかし、トンネル FET に適した接合界面の形成が困難であり、素子構造の非対称性や閾値制御など、回路応用へ向けた課題も多い。

#### 2. 研究の目的

本研究では、III-V 族半導体ナノワイヤ異種集積技術を用いて、格子欠陥・ミスフィット転位を抑制した IV 族/III-V 族へテロ接合を形成する。この接合界面について、界面欠陥制御技術を確立し、これらの新しい半導体へテロ接合界面を低電圧スイッチ素子・トンネル FET へ応用することで、低電圧スイッチ素子による回路研究へとつなげることを目的とし、以下の 3 つの項目について、研究を進める。(1) IV 族/III-V 族へテロ接合界面の界面欠陥制御、(2)Si/InAs 横型TFET の試作、(3) トンネル電流の増大化技術と相補スイッチ動作

#### 3. 研究の方法

Si, Ge 基板上への III-V 族化合物半導体ナノワイヤ選択成長技術を用いることで、極薄 SOI, Ge-OI 基板への III-V 族半導体ナノワイヤを異種集積し、選択成長の特徴を活かしながら、IV 族/III-V 族へテロ接合の界面欠陥制御技術を確立するとともに、高性能・低電圧トンネル FET 素子への応用を図る。

### 4. 研究成果

[1] IV 族/III-V 族ヘテロ接合界面の界面欠陥制御、[2] Si/InAs 横型 TFET の試作、[3] トンネル電流の増大化技術と相補スイッチ動作と回路応用展開に分類し記す。

## [1] IV 族/III-V 族ヘテロ接合界面の界面欠陥制御

## ① SOI, Ge-OI 上の III-V ナノワイヤ選択成長

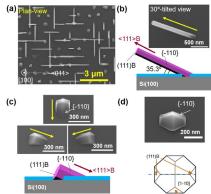

Silicon-on-Insulator (SOI), Ge-OI(001)基板上にトンネル FET(TFET)のソース材料となるIII-Vナノワイヤを選択成 長するため、まず Si(001)上の InAs 選択成長の評価を行っ た。InAs 成長条件は、筆者がこれまでに最適化したナノ ワイヤ成長条件としている。図 1(a)に成長結果を示す。 図から、(001)面から 35.3°傾斜した方向のナノワイヤ成長 【図 1(b)】と{1-10}面、(111)B 面で囲まれた多形構造 【図 1(c)】、{1-10}, (111)B 面からなる八角形構造【図 1(d)】の3種の成長モードがあることがわかる。図1(b) は、Si(001)面に対して<111>B 方向であり、従来の InAs ナノワイヤファセット成長によって成長したと考えら れる。一方、図 1(c)の成長モードは、ナノワイヤ形状 に近く、(001)面に対して、{-211}面の稜線が 35.3°傾斜 しているため、InAsナノワイヤ成長モードを呈してい るが、(111)Bファセット面で成長停止し、基板方向へ 向かってナノワイヤ成長することが分かる(図中矢印 方向)。つまり、基板表面上方<111>B 方向にナノワイ ヤ成長するモードと基板表面下方<111>B 方向にナノ ワイヤ成長するモードが、(001)面の III-V ナノワイヤ 選択成長で生じることを明らかにできた。図 1(d)は、 典型的な(001)面の III-V ファセット成長と同様である。 研究目的である III-V/Si(001) 横型 TFET 実現のために

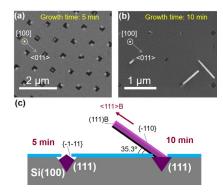

研究目的である III-V/Si(001) 横型 IFET 実現のためには、図 1(b)のナノワイヤ成長モードに制御する必要がある。そこで、Si(001) 面の開口部に選択エッチングすることで、 $\{111\}$  面を形成し、InAs ナノワイヤ選択成長モードの制御について試みた。成長結果を図 2 に示す。 InAs 選択成長時間が 5 min の場合には、SOI 層に形成した 4つの $\{111\}$  面に InAs ナノ構造が形成されており、図 2(b)のように成長時間を長くすると、SOI 面上方にナノワイヤ構造が成長し、図 1(b)で得られたナノワイ

**図1.** (a)成長結果、(b)ナノワイヤ成長モード, (c)多形構造、(d)八角形構造

図 2. InAs on Si(001)選択成長結果 (a) 5 min, (b) 10 min, (c) 成長様式模式図

図3. SOI, Ge-OI 基板上の III-Vナノワイヤ選択成長

ヤ成長モードのみ限定できる。Si(001)面上のランダムな III-V 成長モードについては、Si 表面に{111}ファセットを形成することで、ナノワイヤ成長モードに限定できる。

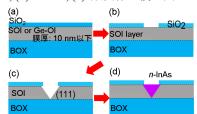

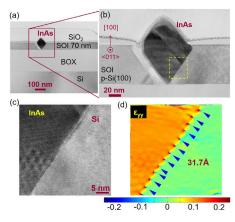

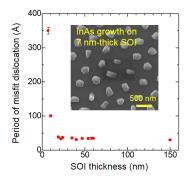

これらの知見を基に、SOI(001)基板に選択マスクと エッチング工程を組み合わせることで、図3に示すよ うな SOI 薄膜層に{111}面を形成し、III-V ナノワイヤ ソース材料を選択成長した。図4に成長結果を示す。 SOI 膜厚 70 nm に対して、InAs ナノワイヤが成長して いることが分かる。図4(b)のSi(111)/InAs界面から、InAs ナノワイヤは、Si{111}面に平行に原子が積層すること が分かり、Si/InAs 界面の歪み分布を計算すると図 4(d) に示すように、周期 31.7Å でミスフィット転位が形成 されていることが分かる。これらの成果は、Ge-OI 基 板においても同様であった。次に、SOI、Ge-OI 層を酸 化工程と HF エッチングを繰り返すことで、SOI, GE-OI 層の薄膜化工程を最適化し、SOI, GeOI 層を 7 – 150 nm まで層厚を制御した。図 5 内挿図に、SOI 層厚 7 nm 上 の InAs ナノワイヤ選択成長結果を示す。 図3と同様に InAs ナノ構造が形成できることが分かる。次に、SOI 層厚と InAs/Si 接合界面のミスフィット転位の周期の 関係を同図に示す。SOI 層厚 20 nm までは、接合界面 のミスフィット転位の周期は、Si/InAs の格子不整合度 11.6%から算出される周期 41 よりも 2 原子層程度長く なることがわかり、層厚 10 nm の場合には、ミスフィ ット転位の周期性がなくなり、転位数が減少し、格子 歪みが残留し、SOI層厚7nmでは、その様子がさらに 顕著になり、転位が 1 つだけ形成され歪みがラメラー 状に分布し、コヒーレント成長に近い格子歪みが現れ ることが明らかになった。これは、SOI 層厚を極薄構

**図4.** SOI 層厚 70 nm 上の InAs ナノワイヤ選択成長(a), (b) TEM 像、(c)拡大像、(d)歪み分布図

図 5. SOI 層厚とミスフィット転位周期 の関係

造にすることで、成長領域が数 nmに限定され、格子緩和過程が抑制されるためと考えられる。 Ge-OI の場合は、予算の都合により、同様の TEM 試験を実施できなかったが、後述するように、 同様の現象を生じると考えられる。 (a) (b) Surface (b) Surface (b) Surface (c)

## ② Ge-OI 気相ドーピング技術

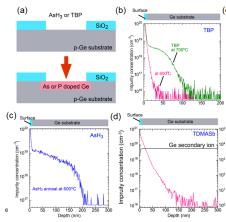

図 6(a)に示すように p-GeOI(001)上に  $SiO_2$  マスク開口部を形成し、MOVPE 反応炉中、水素雰囲気中で、加熱しながら、AsH3, TBP, TDMASb を供給することでそれぞれの As, P, Sb 気相ドーピングについて評価した。評価は SIMS プロファイルによって、ドーパント濃度とドーピング深さを調べた。AsH3 ガスの場合には、 $600^{\circ}$ C アニールでは、Ge 中に As はほぼ拡散せず、 $700^{\circ}$ C では、ドーパント深さ 50 nm,  $4\times10^{18}$  cm<sup>-3</sup>程度拡散し、TBP では、150 nm 程度まで  $600^{\circ}$ C で  $6-10\times10^{18}$  cm<sup>-3</sup>まで拡散することが分かった。また、Sb の場合は、 $600^{\circ}$ C で、ドーパント深さ 50 nm で  $6-10\times10^{19}$  cm<sup>-3</sup>の高濃度ドーピングができることを明らかにした。また、TESn 気相ドーピングによる GeSn 合金層の形成も可能であることを明らかにした(本件は、新規特許出願準備中のため、成果報告書には記載しない。)。

図7に Ge-OI 基板に Sb 原子を高濃度 目ドーピングした試料について、ダイオードと MOSFET 構造を試作した。図7(a), (b)にダイオード構造を示す。図7(b)から、立ち上がり電圧 0.6 V, ダイオード因子 1.8 の良好な整流特性を示し、on/off 比は 1.0 V で 5 桁程度になることがわかる。また、暗電流・リーク電流は 1 mA/ $\mu$ m 程度と非常に高い値を示すことがわかった。これは、トンネル FET 応用に適していることを示している。また、同様に GeOI 上で n-MOSFET を作製した。ゲート酸化膜は  $Al_2O_3$ /HfAlO 多層膜とゲート長 5  $\mu$ m, ゲート幅 20  $\mu$ m、チャネル長 1  $\mu$ m とした。図7(d)に伝達特性を示す。SS は 110 mV/dec, DIBL 160 mV/V であり、これらの気相ドーピングでn 領域を形成できることを示した。

**図 6.** GeOI の気相拡散ドーピング(a)模式図、 SIMS プロファイル(b) As, (c) P, (d) Sb

図 7. (a) p/n-Ge ダイオード、(b) 電流-電 圧特性、(c) MOSFET 構造、(d) 伝達特性

## [2] Si/InAs 横型 TFET の試作

## ① p-SOI/n-InAs 横型ダイオードの作製

横型ダイオード素子構造を作製した。整流特性では、0.5 V 印加で 0.4 mA, 暗電流も  $1\mu\text{A}$ 程度と高い暗電流になり、TFET に適していることを明らかにした。

## ② p-InAs/n-Si/n+-SOI TFET 素子の作製

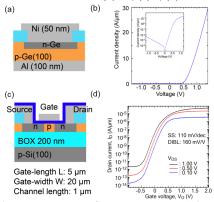

図 8 に研究成果[1]で得られた知見を基に、横型 TFET 素子を作製した。SOI 層厚は 7 nm とし、選択成長法によって、p-InAs ナノワイヤソースを 10 個ソース領域に選択成長した。n-Si ドレイン領域は、P 添加 SOG 剤による熱拡散法で形成した。図 8(a)内挿図に素子構造を示す。ゲート長 1  $\mu$ m, ゲート幅 20  $\mu$ m とした。図 8(c)に作製した TFET の伝達(スイッチ)特性を示す。測定は、ソース接地として暗中で行なった。図から、p-InAs/n-Si 接合界面で生じるトンネル輸送過程がゲート変調

**図 8.** (a) *p*-InAs/*n*-Si/*n*<sup>+</sup>-Si 横型 TFET 構造、内挿図:素子外観、(b)計算特性、(c) 伝達特性、(d) SS 係数とドレイン電流

を受けていることがわかる。on 電流は、InAs ナノワイヤの個数とゲート長で規格化した。 $V_{DS}=V_{G}=0.50~V$ で  $1.5~\mu A/\mu m$  で、on/off 特性は 2~hである。スイッチ特性では、ドレイン電圧の増加でオフリーク電流が大きくなる傾向があるが、DIBL は 4~mV/V であるため、このリーク特性成分はゲートリーク電流が支配的であることが分かる。ドレイン電圧を減少させると、オフリーク電流が下がり  $V_{DS}=0.05~V$  で on/off 比は 4~hになる。 $V_{DS}=0.10~V$  におけるサブスレッショルド係数とドレイン電流の関係を図 8(d)に示す。図からドレイン電流がおよそ一桁に渡り、MOSFET の SS 係数の最小物理限界よりも急峻な係数で変調できることが分かる。最小 SS は、57 mV/dec であった。本研究では、SOI 型 MOSFET に p-InAs ナノワイヤソースを導入したが、リーク電流の抑制が不十分であるが、MOSFET の最小限界以下の小さな SS 係数を実現できた。リーク成分としては、ゲートリーク電流が支配的であるため、後述するように、プレーナ SOI を FIN 加工し、マルチゲート化し、ゲートリークの抑制を図った。

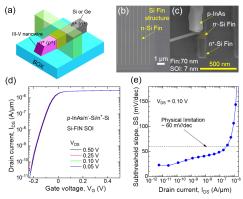

#### ③ p-InAs/n-Si/n+-FIN 型 TFET 素子の作製

図 9(a)に極薄 SOI (7 nm)に FIN 幅 70 nm の細線を形成し、FIN 型の横型 InAs/Si TFET 素子構造を示す。Si ゲート領域・ドレイン領域を立体構造にすることでゲートリーク特性を抑制するねらいがある。作製した FIN 構造を図 9(b)に示す。SOI 膜厚 7 nm に対して、幅 70 nm の FIN 構造が形成されていることがわかる。次に、項目1で確立した InAs ナノワイヤ選択成長技術で、p-InAs 成長した結果を図 9(c)に示す。FIN 細線状に InAs ナノワイヤが形成されたことが分かる。ついで、[2]-②のデバイス工程を導入することで、FIN 型 TFET 素子を作製した。

ドレイン電圧の変化で、on/off 比は変化せず、 およそ 5 桁の範囲でトンネル電流が変調できる 素子構造になることが分かった。 $V_{DS}=0.10~V$  に

図9. (a) p-InAs/n-Si/n<sup>+</sup>-Si 横型 FIN 型 TFET、(b)Si-FIN 構造 SEM 像、(c) FIN 上の p-InAsナノワイヤ SEM 像、(d) 伝達特性、(e) SS 係数とドレイン電流

おける SS 係数とドレイン電流の関係を図 9(d)に示す。最小 SS = 22 mV/dec で急峻な SS 係数を示すドレイン電流は、およそ 4 桁になる。4 桁の平均 SS は 40 mV/dec であり、on/off に要するゲート電圧は 0.30 V であり、従来の MOSFET の 70% 低減できることが分かる。以上から、本研究で提案した横型 InAs/Si FIN 型 TFET 構造を実証できた。

## [3] トンネル電流の増大化技術と相補スイッチ動作と回路応用展開

#### ① Ge/III-V ナノワイヤトンネル接合の形成

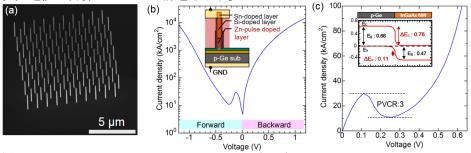

Ge(111)基板上の InGaAs ナノワイヤのヘテロ接合界面の評価を行った。Ge(111)基板上に SiN 薄膜を形成し、In 組成 80%の InGaAs ナノワイヤを選択成長した。初期表面を(111)B 極性面に変換する成長シーケンスを導入することによって、基板と垂直方向に林立した InGaAs ナノワイヤを集積する技術を確立した。さらに、供給原料 In/Ga 組成比を変化させることで、In 組成を 0-100%まで任意に変化させた InGaAs ナノワイヤを Ge(111)上に集積する技術についてもここで確立した。次に、p-Ge(111)上に集積した i-InGaAs/n-InGaAs 縦接合ナノワイヤを集積し、図 10(b)内挿図に示す縦型二端子構造を作製した。ナノワイヤの In 組成は 75%,直径は 100 nmである。図 10(b)に電流密度・電圧特性を示す。順バイアス方向では、0.1 V 付近にバンド間トンネル輸送を示す負性微分抵抗特性が観察され、逆方向バイアスでは、非常に高いトンネル電流が得られた。i-InGaAs/p-Ge 接合界面は、高濃度ドーピングをしていないにもかかわらず、江

崎トンネル輸送に由来した負性微分抵抗を生じており、接合界面近傍は高濃度ドープ層が形成 されていることが分かり、そのため、逆バイアス方向において、大きなトンネルリーク電流を 示すことを明らかにした。図 10(c)に示すように、PVCR はおよそ 3 になり、Si 材料からなる共 鳴トンネルダイオードの PVCR よりも大きくなる傾向を示しており、この Ge/InGaAs ヘテロ接 合界面が高いトンネル確率を示すトンネル接合として有用であることを明らかにした。図 11(c) 中に一次元近似で計算したバンド構造を示す。

図 10. (a) Ge(111)面上の InGaAs ナノワイヤ選択成長結果、(b) InGaAs ナノワイヤ/Ge 縦型 ダイオード素子の電流密度・電圧特性、(c)電流密度・電圧特性の順方向バイアス領域と バンド構造 (内挿図)

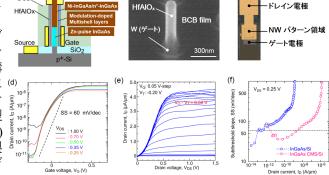

# ②変調ドープナノワイヤ材料による二次元電子ガス/トンネル接合の形成と実証

本研究では、Si 上に選択成長した ® InGaAs/InP/InAlAs/InPコアマルチシェ ルナノワイヤを形成し、InGaAs ナノ ワイヤ中に形成される二次元電子ガ ス層と Si 間のトンネル輸送を InGaAs/Si 接合界面で実現する素子構 造を縦型 TFET で検証した。図 11 に ® 二次元電子ガスを形成した InGaAs ナ ノワイヤと Si 接合界面による縦型 TFET の素子特性を示す。図 11(a) - (c) は、縦型 TFET 素子構造模式図、作製 したサラウンディングゲート構造、デ バイス素子外観を示す。図 11(d),(e)に 示すように、急峻な SS 特性を維持し たままトンネル電流を増加できるこ とを実証した。最小 SS 係数は、42

図 11. (a) InGaAs/InP/InAlAs/InP コアマルチシェルナノ ワイヤの縦型 TFET 素子構造、(b) 作製結果、(c) デバイ ス素子外観、(d) 伝達特性, (e) 出力特性、(f) SS 係数と ドレイン電流の関係

mV/dec で急峻な SS を示す電流領域は 3 桁維持できる。また、図 14(f)に示すように、変調ドー プ層のない InGaAs/Si TFET と比べると、同じドレイン電圧・ゲート電圧印加条件で、トンネ ル電流が 1000 倍まで増加し、3 μΑ/μm までオン電流を増大できることを実証できた。

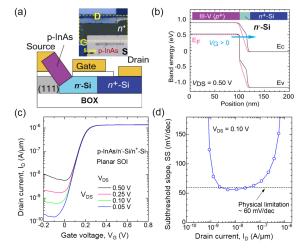

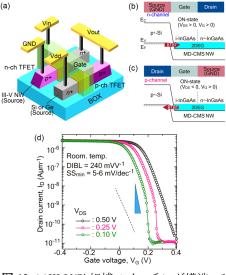

## ③相補スイッチングの実証

相補型スイッチング構造として、変調ドープ型の縦® 型 TFET 素子構造について、ソース・ドレイン接地を 入れ替えることで、n/p チャネル特性を実証した。図 12(b)に示すように、図 11 で n チャネル型 TFET 特性が 得られた試料について、ソース接地端子を Si から InGaAs に入れ替えることによって、二次元電子ガスか ら p-Si 方向にトンネル輸送するキャリアをサラウンデ ィングゲートで変調し p チャネル TFET 特性を実証で きる。図 12(d)に p チャネル TFET 特性を示す。ソース 接地箇所を入れ替えることで、DIBLが大きくなるもの の、急峻な SS 特性を維持し、p チャネルスイッチング 特性を実現できることを示した。最小 SS 係数は、低電 圧で 5-6 mV/dec であり、オン電流は、n チャネル TFET のオン電流とほぼ同じ値を示すことがわかった。また、 集積面積の観点から、当初提案していた横型 TFET 素 子の相補スイッチングについて、ソース・ドレイン接 地の入れ替え構造では、集積面積が広くなる課題があ ったが、図 12 の縦型 TFET で相補スイッチング構造を 構成することによって、高密度・低電圧立体回路を実 nチャネル、(c)pチャネル TFET 動作模式図、 現できることが明らかになり、新しい縦型立体集積回 路構造へと展開することができた。

図 12. (a)III-V/Si 相補スイッチング構造、(b) (d) 伝達特性

5. 主な発表論文等

〔雑誌論文〕(計13件)

- J. Motohisa, H. Kameda, M. Sasaki, <u>K. Tomioka</u>: "Characterization of nanowire light-emitting diodes grown by selective-area metal-organic vapor-phase epitaxy" Nanotechnology, Vol. 30, pp. 134002-1 – 9 (2019).

- M. Yusuke, A. Yoshida, J. Motohisa, <u>K. Tomioka</u>:

"Growth and characterization of GaAs nanowires on Ge(111) substrates by selective-area MOVPE"

J. Cryst. Growth, Vol. 506, pp. 135 139 (2018).

- 3. H. Gamo, K. Tomioka: "Selective-area growth of pulse-doped InAs nanowires on Si and vertical transistor application" J. Cryst. Growth, Vol. 500, pp. 58 62 (2018).

- 4. <u>Katsuhiro Tomioka</u> and Takashi Fukui:"(Invited paper) Transistor application using vertical III-V nanowires on Si platform" ECS Trans., Vol. 80, pp. 43 52 (2017).

- K. Chiba, <u>K. Tomioka</u>, A. Yoshida, J. Motohisa: "Composition controllability of InGaAs nanowire arrays in selective-area growth with controlled pitches on Si platform" AIP Advances, Vol. 7, pp. 125304- 1 – 7 (2017).

- 6. <u>Katsuhiro Tomioka</u>, J. Motohisa, Takashi Fukui:"(Invited paper) Advances in stepp-slope tunnel FETs" Proc. IEEE ESSDERC, pp. 397 402 (2016).

〔学会発表〕(計74件)

- 1. <u>K. Tomioka</u> and T. Fukui, "Transistor applications using vertical III-V nanowires on Si platform" 232nd ECS meeting, Washington DC, USA, October 1 5 (2017) 招待講演

- 2. <u>K. Tomioka</u>, J. Motohisa, T. Fukui "Vertical III-V nanowires on Si and transistor applications" The 15th International Conference on Advanced Materials (IUMRS-ICAM 2017), Kyoto, Japan, August 27 September 1 (2017).招待講演

- 3. <u>K. Tomioka</u>, J. Motohisa, T. Fukui,"Advances in Steep-Slope Tunnel FETs", ESSCIRC-ESSDERC 2016, Lausanne, Switzerland, September 12th 15th (2016).招待講演

- 4. <u>K. Tomioka</u>, J. Motohisa, T. Fukui, "Selective-area growth of III-V nanowires on Si and transistor applications", The Eighth International Conference on Low Dimensional Structures and Devices (LDSD 2016), Mayan Riviera, Mexico, August 28th September 2nd (2016).招待講演

[図書] (計2件)

- 1. <u>Katsuhiro Tomioka</u>: "Several Challenges in Steep-Slope Tunnel Field-Effect Transistors" 分担執筆 Chapter 2 in Emerging Devices for Low-Power and High-Performance Nanosystems Physics, Novel Functions, and Data Processing. S. Deleonibus ed. pp. 73 102, Pan Stanford Publishing (2018).

- 2. <u>Katsuhiro Tomioka</u>: "Chapter 14 III-V Nanowires: Transistor and photovoltaic applications"分担 執筆 Chapter 14 in Novel Compound Semiconductor Nanowires –Materials, Devices, and Applications F. Ishikawa, I. Buyanova ed. pp. 464 516, Pan Stanford Publishing (2017).

## [産業財産権]

○出願状況(計2件)

名称:Tunnel Field Effect Transistor 発明者:Katsuhiro Tomioka, Takashi Fukui 権利者:Katsuhiro Tomioka, Takashi Fukui

種類:特許

番号: US-2018-0294362-A1

出願年:2018 国内外の別: 外国

○取得状況(計1件)

名称:Tunnel Field Effect Transistor 発明者:Katsuhiro Tomioka, Takashi Fukui 権利者:Katsuhiro Tomioka, Takashi Fukui

種類:特許

番号:15/764,426 取得年:2018 国内外の別: 外国

[その他]

https://researchmap.jp/read0146924/

※科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。