# 科研費

# 科学研究費助成事業 研究成果報告書

令和 3 年 6 月 1 7 日現在

機関番号: 16101

研究種目: 基盤研究(C)(一般)

研究期間: 2018~2020

課題番号: 18K11218

研究課題名(和文)積層チップ間の故障テスト用信号生成・供給回路設計手法の開発

研究課題名(英文)On design-for-testability circuit design of pattern generation and propagation for detecting faults at interconnects in stacked ICs

#### 研究代表者

四柳 浩之 (YOTSUYANAGI, Hiroyuki)

徳島大学・大学院社会産業理工学研究部(理工学域)・准教授

研究者番号:90304550

交付決定額(研究期間全体):(直接経費) 3,500,000円

研究成果の概要(和文):本研究では,3次元積層ICチップのチップ間接続における故障テストを行うための検査容易化設計について研究を行なった。特に信号遷移に異常が現れる故障および劣化の検出を対象として,遅延故障の検査容易化回路とその検査容易化回路へのテスト信号・制御信号の供給回路の設計手法を開発した。テスト遷移信号の付加遅延のばらつきを抑える遅延ゲート設計や,テスト時間を抑える検査対象経路の複数選択信号生成手法,およびテスト時の制御・観測時間を低減するため信号供給に用いるバウンダリスキャン回路に迂回経路を設け必要なクロック数の削減を行なった。

研究成果の学術的意義や社会的意義 3次元積層ICには,配線が短く高速動作が可能,パッケージの小型化が可能,低消費電力であることなどの利点がある。提案した各手法によりIC間接続に発生する遅延を生じる検査困難な遅延故障のテストが可能となり,またそのテスト時間を抑えるテスト入力生成およびテスト容易化設計手法の適用により積層ICの製造コスト削減に寄与すると考えられる。

研究成果の概要(英文): In this research, we proposed some circuits and procedures for test pattern generation and propagation for design-for-testability circuit that detects faults at interconnects of 3D stacked ICs. For detecting delay caused by fault and aging effects, we evaluated and enhanced the design-for-testability circuits for delay faults. The proposed methods include a design of a delay gate that has a small difference caused by test input signal transitions, a test pattern generation for reducing test application time by selecting multiple paths during some test patterns, and a design-for-testability circuit that has bypass operation during setting control signals and observing test results using boundary scan design for reducing test clocks.

研究分野: 計算機システム関連

キーワード: VLSIの検査技術 検査容易化設計 3次元積層IC 遅延故障 LSIテスト ディペンダブル・コンピュー ティング

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

## 様 式 C-19、F-19-1、Z-19(共通)

## 1.研究開始当初の背景

集積回路は微細化により集積度の向上を達成してきたが,微細化が限界に近づく中で次世代の集積技術として複数チップを1つのパッケージに収める3次元積層 IC が実用化されている。テストの観点からは,積層チップ間の接続について,従来のプリント基板上の複数チップのテスト容易化手法であるバウンダリスキャン法を適用して,静的な特性をテストする技術が提案されているが,信号遷移の異常などの動的な特性のテストについてはコスト面などの問題があっ

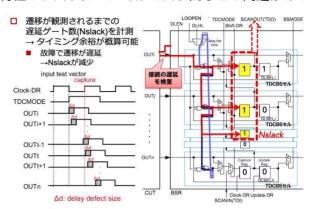

た。チップ間接続を通る遷移信号検査用のテスト容易化回路として,時間-ディジタル変換回路 (Time-to-digital converter; TDC)を従来のバウンダリスキャン設計に埋め込んだ図1の TDC 組込型バウンダリスキャン設計(以下,TDCBS 設計)をこれまでに提案していたが,ばらつきによが特性の違いに対する補正などの問題が残っていた。また,積層チップの遅延故障テスト適用時にテスト対象チップへのテスト用信号の供給・テスト結果の観測時間などのコストに課題があった。

図 1 TDC 組込型バウンダリスキャン(TDCBS)

#### 2.研究の目的

本研究では,積層チップ間配線の信号遷移をテストするためのテスト容易化設計と,テストのための制御信号生成・供給回路の設計手法の提案を目的とした。これまでに,TDCBS 設計において試作した IC の測定より,チップ間ばらつきやチップ内ばらつきに対する補正などの対応が課題となっている。遅延故障検査容易化回路・制御信号供給回路において,主に(1)テスト用の制御信号タイミングを考慮する制御信号生成・供給回路の設計(2)遅延故障検査容易化回路・制御信号供給回路における特性ばらつきの補正の検討(3)異種チップ間接続の積層テストへの提案回路の応用・改良,の3課題について研究を行なった。

#### 3.研究の方法

積層チップ間の故障テスト用に遅延を付加する遅延故障テスト容易化設計におけるチップ間ばらつきやチップ内ばらつきに対する補正,制御信号生成・供給回路の設計などは試作 IC の設計・測定に基づき研究を行なった。回路設計には,導入済みの東京大学大規模集積システム設計教育センター(VDEC)提供の Synopsys 社, Cadence 社, Mentor Graphics 社等の設計用 EDA ツールを用い,期間中に4度のチップ試作を行なった。また,テスト入力信号生成などではテスト対象経路の選択アルゴリズムの開発およびシミュレーションによる評価を行なった。

- (1)検査容易化回路を用いて供給するテストパターンおよびそのテストパターンにより観測が必要な検査対象経路の組合せを,同一パターンで複数経路の観測を行うことを考慮して求める手法を提案した。同時測定可能な検査対象経路の選択には遅延のばらつきも考慮して決定し,検査時間の短縮に有効である。(文献1)

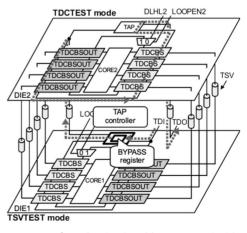

- (2)検査容易化回路における遅延付加部の分割などの回路構成の改良を行った。遅延故障検査対象回路への信号供給に関して,検査時間の短縮を行うために,シリコン貫通ビアへの信号供給に用いる遅延付加部と遅延量観測に用いる遅延付加部を分割した。図2の回路例では信号供給部にTDCBSOUTセル,観測用のTDCBSセルの2種のバウンダリスキャンセルを設け,かつ観測時は測定対象であるチップ(図中のDIE2)のみを観測するようにバイパスモードを設けた。遅延付加部のゲート段数を削減することで,検査時間の短縮が可能となった。(文献2)

図2 TSV 検査のためのバイパス経路を持つ TDCBS 設計

(3) 遅延故障検査容易化設計におけるテスト時間について,使用するバウンダリスキャンセルの制御・観測用のスキャンシフト動作を低減するための設計改良を提案した。制御信号の並列入力および観測不要な経路の迂回を行うことでスキャンシフト動作に必要なクロック数を削減した。

(4) 遅延故障検査容易化回路における遅延ゲートの検討および設計

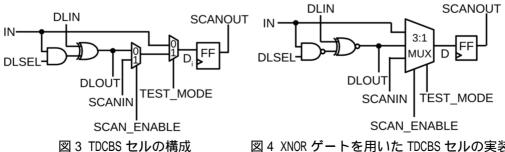

遅延付加部に用いる遅延付加ゲートとして内部構造の異なる2種の設計を行い,シミュレー ションおよび実測により評価を行った。遅延付加ゲート内部の XOR ゲートで立上り遅延と立下 り遅延に違いがあると観測信号が消滅するなどの問題がある。立上り遅延と立下り遅延の差が 少ないパストランジスタベースの XNOR ゲートを利用し,遅延付加ゲートのトランジスタレベル での設計改良を行なった。改良した遅延付加ゲートを含む遅延故障検査容易化回路を試作した。

- (5)遅延故障検査容易化回路内部の遅延付加ゲートおよび遅延付加ゲート間配線による付加遅 延量の差を抑えるために,レイアウト設計時の配置配線について検討・改良を行った。遅延付加 ゲートのスタンダードセル化と配置配線制約の付加の2種により、セル内の遅延差とセル間の 遅延差を抑える設計手法を提案した。

- (6)遅延故障検査容易化設計における遅延補正について,試作 ICの測定により使用する遅延付 加部の遅延付加ゲートの配置・配線による影響を考察した。さらに配線長差などの影響を低減し、 かつ測定回数を抑えた遅延付加部の部分経路の遅延量の測定手法を提案した。

- (7)異種チップ間の接続として,積層化 CMOS センサにおける接続テストについて検討した。ま たクロック信号供給の際にチップ間でのタイミング余裕の関係から遅延付加部を長く伝搬する 場合を考慮するクロック制御回路を設計した。

- (8)外部からのテスト用信号供給について,マイコンと試作 IC を用いたデモボードにおいて, マイコンにより試作 IC を制御し遅延量を監視するための制御プログラムを作成し、信号遅延監 視システムを開発した。

#### 4. 研究成果

各研究方法によって得られた成果は次のとおりである。各成果は研究期間中に 4 回設計した 試作 IC の測定およびシミュレーションにより得られたものを含む。

- (1)遅延故障テストの遷移信号入力のためのテストパターンと複数観測経路の選択のための制 御信号に関して,同一のテストパターンで検査可能な対象経路を優先して同時選択するテスト パターン生成手法を提案した。従来と比較して最大 68%テスト時間短縮が可能となった。

- (2)検査容易化回路における遅延付加部の分割については,遅延付加部を遅延観測用と遷移信 号入力用の2つに分割することで,観測用のスキャンシフト動作において,一度のテスト結果観 測にかかる時間のうち,信号供給用のTDCBSOUT セルによるバウンダリスキャンチェインの長さ の分だけ検査時間を削減可能である.

- (3) TDCBS 設計における検査時間は、観測経路の設定と検査結果の観測のためのスキャンシフ ト動作に依存する。TDCBS セルをグループ分割し,観測対象の選択に必要な制御信号を並列入力 し、観測時にも遷移信号が伝搬する可能性のあるグループのみをスキャンシフトの対象とする ことで、スキャンシフトに必要なテストクロック数を限定することが可能となった。

- (4) 改良した遅延付加ゲートセルにおいては,図3のTDCBS セルの基本構成から立上り遅延と 立下り遅延の差が少ないパストランジスタベースの XNOR ゲートを利用するとともに,テストモ ード選択に要するトランジスタ数の少ない3:1MUX を用いる図4の構成とした。このゲートセル を含む検査容易化設計を施した IC を試作,測定し,従来使用していた遅延付加ゲートセルより 遅延分解能の向上および遷移依存の遅延分解能の差が小さいという結果が得られた。また,信号 選択回路の設計を行うことで従来の遅延付加部より約 18%省面積化することができた。

図 4 XNOR ゲートを用いた TDCBS セルの実装

- (5) レイアウト設計時の配置配線について,遅延付加ゲートのスタンダードセル化と配置配線制約の付加の2種により,セル内の遅延差とセル間の遅延差を抑える設計手法を提案した。提案の遅延故障検査容易化回路を含む試作チップを試作した。遅延付加部と TSV の配置を考慮し,遅延付加部の各ゲート間での配線長差を抑える設計手法を提案した。試作チップを TSV により接続する3次元積層チップの製作も行っており今後測定を行う予定である。

- (6)遅延付加部の遅延量のばらつきとその測定時の補正方法について検討を行った。各遅延付加ゲートの遅延量について試作 IC において遷移信号の測定対象経路を複数設けることで,測定箇所による遅延量の差異を調査した。制御信号の印加法の改良により,従来設計を変更することなく,任意の遅延付加ゲートを起点とする信号遷移の測定が可能となった。また,単一の付加遅延量による概算ではなく,複数箇所の付加遅延量を用いて遷移信号の遅延量を計算することで,遅延故障検査に用いるタイミング余裕の測定における遅延付加部のばらつきの補正が可能となった。

- (7) センサ回路とロジック回路の TSV による接続についての検査容易化設計に関しては,以前提案した CMOS センサの検査容易化設計を用いて TSV 部の断線故障検査シミュレーションを行い TSV 部での電圧変動を観測する回路の設計を行なっている。クロック制御回路については ADPLL を用いるものとクロック信号を半周期早めて遷移信号の伝搬するゲート段数を抑えるものの 2種を設計した。

- (8) 提案した検査容易化設計の制御信号をマイコンから供給し,検証用テストパターンと微小遅延故障検査用テストパターンを用いて動作検証を行った。実装基板上で遅延測定することで劣化検知などの目的に応用可能と考えられる。

#### < 引用文献 >

Kanami Nagata, Hiroyuki Yotsuyanagi, Masaki Hashizume, "Test Time Reduction of Small Delay Testing for Scan Design with Embedded TDC," the 21st IEEE Workshop on RTL and High Level Testing, 2020.

Satoshi Hirai, Hiroyuki Yotsuyanagi and Masaki Hashizume, "Test Time Reduction on Testing Delay Faults in 3D ICs Using Boundary Scan Design," IEEE 27th Asian Test Symposium, 2018.

#### 5 . 主な発表論文等

「雑誌論文】 計3件(うち査読付論文 0件/うち国際共著 0件/うちオープンアクセス 0件)

| 「維応論又」 計3件(つら直流判論又 0件/つら国際共者 0件/つらオーノノアクセス 0件)                                                         |                                                   |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1 . 著者名                                                                                                | 4 . 巻                                             |

| 平井 智士,四柳 浩之,橋爪 正樹                                                                                      | 118                                               |

| 2.論文標題                                                                                                 |                                                   |

| TDC 組込み型バウンダリスキャンにおける遅延付加部の分割による検査時間の削減                                                                | 2018年                                             |

|                                                                                                        |                                                   |

| 3.雑誌名                                                                                                  | 6.最初と最後の頁                                         |

| 電子情報通信学会技術研究報告                                                                                         | 119-124                                           |

|                                                                                                        |                                                   |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                                                | 査読の有無                                             |

| なし                                                                                                     | 無                                                 |

|                                                                                                        |                                                   |

| オープンアクセフ                                                                                               | 国際共革                                              |

| │ オープンアクセス<br>- オープンアクセスではない、又はオープンアクセスが闲難                                                             | 国際共著                                              |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                 | 国際共著                                              |

| オープンアクセスではない、又はオープンアクセスが困難                                                                             | - 4 . 巻                                           |

| オープンアクセスではない、又はオープンアクセスが困難                                                                             | -                                                 |

| オープンアクセスではない、又はオープンアクセスが困難  1 . 著者名 谷口 公貴, 四柳 浩之, 橋爪 正樹                                                | - 4 . 巻<br>118                                    |

| オープンアクセスではない、又はオープンアクセスが困難  1 . 著者名 谷口 公貴, 四柳 浩之, 橋爪 正樹  2 . 論文標題                                      | - 4 . 巻                                           |

| オープンアクセスではない、又はオープンアクセスが困難  1 . 著者名 谷口 公貴, 四柳 浩之, 橋爪 正樹                                                | - 4 . 巻<br>118<br>5 . 発行年                         |

| オープンアクセスではない、又はオープンアクセスが困難  1 . 著者名 谷口 公貴, 四柳 浩之, 橋爪 正樹  2 . 論文標題 自動生成パターンの微小遅延故障検査用回路への適用性検討  3 . 雑誌名 | - 4 . 巻<br>118<br>5 . 発行年<br>2018年<br>6 . 最初と最後の頁 |

| オープンアクセスではない、又はオープンアクセスが困難  1 . 著者名 谷口 公貴, 四柳 浩之, 橋爪 正樹  2 . 論文標題 自動生成パターンの微小遅延故障検査用回路への適用性検討          | -<br>4 . 巻<br>118<br>5 . 発行年<br>2018年             |

査読の有無

国際共著

無

## 〔学会発表〕 計17件(うち招待講演 0件/うち国際学会 5件)

1.発表者名

オープンアクセス

なし

牧野 紘史, 四柳 浩之, 橋爪 正樹

掲載論文のDOI(デジタルオブジェクト識別子)

2 . 発表標題

3D ICの検査容易化設計における遅延故障検査用ダイ選択回路の開発

オープンアクセスではない、又はオープンアクセスが困難

3 . 学会等名

電子情報通信学会ソサイエティ大会

4.発表年

2020年

1. 発表者名

Kanami Nagata, Hiroyuki Yotsuyanagi, Masaki Hashizume

2 . 発表標題

Test Time Reduction of Small Delay Testing for Scan Design with Embedded TDC

3 . 学会等名

the 21st IEEE Workshop on RTL and High Level Testing (国際学会)

4.発表年

2020年

| 1.発表者名<br>福田 康介, 四柳 浩之, 橋爪 正樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 . 発表標題<br>微小遅延故障検査容易化設計用テストクロック制御回路の検討                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 . 学会等名<br>第35回エレクトロニクス実装学会春季講演大会                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4 . 発表年<br>2021年                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.発表者名<br>有元 康滋,牧野 紘史,四柳 浩之,橋爪 正樹                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2 . 発表標題<br>TDC組込み型バウンダリスキャンの観測セル部分選択による検査時間削減について                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3 . 学会等名<br>第35回エレクトロニクス実装学会春季講演大会                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4 . 発表年<br>2021年                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1 . 発表者名<br>Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 . 発表者名                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 . 発表者名 Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume 2 . 発表標題                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 . 発表者名 Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Measurement under Delay Variations in Boundary Scan Circuit with Embedded TDC  3 . 学会等名                                                                                                                                                                                                                                                                                                                    |

| 1 . 発表者名 Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Measurement under Delay Variations in Boundary Scan Circuit with Embedded TDC  3 . 学会等名 2019 IEEE International Test Conference in Asia (国際学会)  4 . 発表年 2019年  1 . 発表者名 Toshiaki Satoh, Hiroyuki Yotsuyanagi and Masaki Hashizume                                                                                                                                                                          |

| 1 . 発表者名 Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Measurement under Delay Variations in Boundary Scan Circuit with Embedded TDC  3 . 学会等名 2019 IEEE International Test Conference in Asia (国際学会)  4 . 発表年 2019年  1 . 発表者名 Toshiaki Satoh, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Elements in Boundary Scan Cells for Delay Testing of 3D IC Interconnection                                                                            |

| 1 . 発表者名 Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Measurement under Delay Variations in Boundary Scan Circuit with Embedded TDC  3 . 学会等名 2019 IEEE International Test Conference in Asia (国際学会)  4 . 発表年 2019年  1 . 発表者名 Toshiaki Satoh, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Elements in Boundary Scan Cells for Delay Testing of 3D IC Interconnection  3 . 学会等名 IEEE 2019 International 3D Systems Integration Conference (国際学会) |

| 1 . 発表者名 Shuya Kikuchi, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Measurement under Delay Variations in Boundary Scan Circuit with Embedded TDC  3 . 学会等名 2019 IEEE International Test Conference in Asia (国際学会)  4 . 発表年 2019年  1 . 発表者名 Toshiaki Satoh, Hiroyuki Yotsuyanagi and Masaki Hashizume  2 . 発表標題 On Delay Elements in Boundary Scan Cells for Delay Testing of 3D IC Interconnection                                                                            |

| 1   | <b> </b> |

|-----|----------|

| - 1 | ,光衣有石    |

知野 遥香,菊池 愁也,四柳 浩之,橋爪 正樹

# 2 . 発表標題

TDC 組込み型バウンダリスキャンを用いる信号遅延監視システムの検討

#### 3 . 学会等名

第34回エレクトロニクス実装学会春季講演大会

#### 4.発表年

2020年

#### 1.発表者名

Jumpei Kawano, Hiroyuki Yotsuyanagi and Masaki Hashizume

# 2 . 発表標題

On Design and Evaluation of a TDC Cell Embedded in the Boundary Scan Circuit for Delay Fault Testing of 3D ICs

#### 3 . 学会等名

33rd International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC 2018)(国際学会)

#### 4.発表年

2018年

#### 1.発表者名

Satoshi Hirai, Hiroyuki Yotsuyanagi and Masaki Hashizume

## 2 . 発表標題

Test Time Reduction on Testing Delay Faults in 3D ICs Using Boundary Scan Design

# 3 . 学会等名

IEEE 27th Asian Test Symposium (国際学会)

#### 4.発表年

2018年

## 〔図書〕 計0件

## 〔産業財産権〕

〔その他〕

-

6 . 研究組織

| 0 | 7. 7. 7. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. |                       |    |

|---|-------------------------------------------------|-----------------------|----|

|   | 氏名<br>(ローマ字氏名)<br>(研究者番号)                       | 所属研究機関・部局・職<br>(機関番号) | 備考 |

#### 7. 科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

# 8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|