## 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成 24 年 5 月 28 日現在

機関番号: 14401

研究種目:若手研究(S)研究期間:2007~2011課題番号:19676001研究課題名(和文)

高性能 SiC パワーエレクトロニクス実現に向けた理想 MOSFET 作製プロセスの創成

研究課題名 (英文)

Fabrication of High-quality SiC-MOSFETs for Advanced Power Electronics

研究代表者

渡部 平司(WATANABE HEIJI)

大阪大学・大学院工学研究科・教授

研究者番号:90379115

研究成果の概要(和文): シリコンカーバイド(SiC)は電気エネルギーの高効率利用に重要なパワーデバイス用の半導体材料として期待されている。本研究では、次世代の SiC スイッチングデバイスを構成する金属/酸化物/半導体(MOS)構造の界面物性を詳細に解析し、これらの知見に基づいて SiC-MOS デバイスの特性改善技術を提案し、その優位性を実証することに成功した。さらに、従来の熱酸化膜に代わる絶縁膜材料として SiC パワーデバイスに最適化した高誘電率ゲート絶縁膜を実現し、トランジスタレベルでの性能実証に成功した。

研究成果の概要(英文): Silicon carbide (SiC) has gained considerable attention for power electronics. Among the various types of power devices, metal-oxide-semiconductor (MOS) should become a key component for next generation SiC switching devices. In this study, we investigated fundamental aspects of SiC oxidation and MOS interfaces, and proposed novel methods for improving electrical properties of SiC-MOS devices. We also fabricated MOS transistors with high-permittivity gate dielectrics and successfully demonstrated superior device performance.

#### 交付決定額

(金額単位:円)

|         | 直接経費         | 間接経費         | 合 計          |

|---------|--------------|--------------|--------------|

| 2007 年度 | 15, 700, 000 | 4, 710, 000  | 20, 410, 000 |

| 2008 年度 | 12, 500, 000 | 3, 750, 000  | 16, 250, 000 |

| 2009 年度 | 15, 600, 000 | 4, 680, 000  | 20, 280, 000 |

| 2010 年度 | 14, 100, 000 | 4, 230, 000  | 18, 330, 000 |

| 2011 年度 | 10, 800, 000 | 3, 240, 000  | 14, 040, 000 |

| 総計      | 68, 700, 000 | 20, 610, 000 | 89, 310, 000 |

研究分野:薄膜工学

科研費の分科・細目:応用物理学・工学基礎、薄膜・表面界面物性

キーワード:パワーエレクトロニクス、MOSデバイス

## 1. 研究開始当初の背景

電気エネルギーの高効率利用は、社会的にも 最重要課題となっている。パワーエレクトロ ニクスは、電力の変換と制御を担うデバイス であり、その高性能化によって電力損失を低 減することは、昨今のエネルギー或いは環境 問題の解決に向けて大きな意味を持つ。従来 のパワーエレクトロニクスは、シリコン半導 体を用いて作製されているが、更なる高性能化に際して物理限界の壁に直面している。シリコンカーバイド(SiC)はワイドバンドギャップ半導体の一種であり、シリコンに比べてより高耐圧、高温での動作が可能であり、エネルギー損失の低減に有利である。さらにスイッチング素子の基本構成である金属/酸化物/半導体(MOS)構造の形成において、

SiC 表面の熱酸化で SiO<sub>2</sub> 絶縁層を形成できるなどの特徴を有している。つまり、良質なSiC-MOS 構造の実現は、社会的にも大きなインパクトを有し、その研究開発の進展が切望されている。しかし、シリコンとは対照的に、SiC 半導体では酸化前の表面清浄化や基板の平坦化技術が未だ確立していない。また熱酸化 SiO<sub>2</sub> 中に炭素が残存し、界面領域に濃縮された炭素が電気特性や絶縁耐圧を著しく劣化させるために、SiC の優れた物性から予測されるデバイス性能を実現するには至っておらず、理想 SiC-MOS 構造作製技術の確立が急務となっている。

#### 2. 研究の目的

本研究では、高性能 SiC MOS 型電界効果トランジスタ (MOSFET) の実現を最終目標として、SiO<sub>2</sub>/SiC 界面物性を理解し、これらの知見に基づいた新プロセスの構築と、デバイスレベルでの優位性実証を目指した。具体的には、①大気圧高密度プラズマを用いた SiC 半導体表面の平滑化・清浄化技術、②超薄 SiO<sub>2</sub>/SiC 構造の作製とプラズマ応用による界面電気特性改善法の開発、③高誘電率 (High-k) 絶縁膜との積層構造 SiC-MOS デバイスの作製技術を確立し、④高性能 SiC-MOSFET を試作して我々が提案する新技術の優位性を実証することを目的とした。

#### 3. 研究の方法

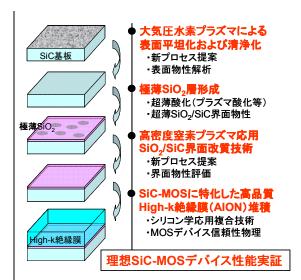

図1に本研究策定当初の具体的な研究項目を 示す。理想 SiC-MOS 構造とデバイス性能実 証に向けて、SiC表面清浄化から高品質 MOS 構造形成までの要素技術の構築を目指した。 第一段階では、SiC 基板表面の清浄化と平坦 化を目的として大気圧水素プラズマを用い た表面処理技術の研究開発を行う。その後、 High-k/SiO<sub>2</sub>/SiC スタックの界面層として用 いる良質な極薄 SiO<sub>2</sub> 絶縁膜の形成技術なら びに MOS 界面特性改善技術を探索する。こ れらの MOS 界面改善技術の基礎研究では、 放射光光電子分光測定等の表面界面分析技 術を駆使し、新規プロセス提案に必要な物性 情報を取得する。さらに界面特性に優れた SiO<sub>2</sub>/SiC 上にワイドバンドギャップ半導体 に特化したアルミナ系 High-k 絶縁膜を堆積 し、絶縁特性・界面電気特性・信頼性の全て の性能で従来の熱酸化 SiC-MOS の特性を凌 駕する高性能ゲートスタックを完成させる。 最終段階としては、AlON/SiO2/SiC スタック を有した SiC-MOSFET を試作し、その優位 性をデバイスレベルで実証する。また MOS デバイスの信頼性を決定する様々な要因を 抽出すると共に、SiC 表面酸化現象や MOS 界面の電気特性を決定する物理現象を見極 め、これからの SiC パワーエレクトロニクス 研究に必要な知見を蓄積する。

図 1. 理想 SiC-MOS 構造作製に向けた戦略

#### 4. 研究成果

以下、本研究で得られた主要成果をまとめた。 研究成果の詳細に関しては、参照の発表論文 を参照頂きたい。

(1) 大気圧水素プラズマによる SiC 表面処理 SiC 半導体の表面平坦化ならびに清浄化を、高密度大気圧水素プラズマ処理によって実現することに成功した。基板温度室温にて極めて早い加工速度(約0.1µm/min)を実現し、結晶性に優れた SiC 表面を形成できることを確認した。また SiC 表面の原子レベルでのラスネス観察から、エッチング機構はステップ端に依存しないことが示唆され、水素ラジカルと SiC との表面反応の観点からも興味深い実験結果を得た。(発表論文[7])

# (2) SiO<sub>2</sub>/SiC 構造への窒素プラズマ照射と高温水素アニール複合処理技術の提案

高密度窒素ラジカルを SiO<sub>2</sub>/SiC 構造に照射 すると共に、これに引き続いて高温水素アニ ールを施す複合技術を提案した。高密度窒素 プラズマを用いることで、従来困難であった 低温(500℃)でのMOS界面への窒素導入に成 功し、これに続いて様々な処理温度で水素ガ スアニールを施し、界面欠陥準位密度を MOS キャパシタの電気特性から評価した。 その結果、プラズマ処理で予め MOS 界面に 窒素を導入した試料では、単独では効果が全 く現れない 450℃での低温水素アニールでも 界面準位密度が低下した。また水素アニール 温度を 900℃以上とすることで、従来の NOx 系ガスアニール処理の特性を上回る MOS 界 面を実現した。これらの実験結果から、ラジ カル窒素の供給により、SiC-MOS 界面に偏 析した炭素不純物の脱離が促進され、界面欠 陥の水素終端が進行する界面特性改善機構 を提案した。(発表論文 [14])

## (3) プラズマ窒化 SiC 表面の熱酸化による SiO<sub>2</sub>/SiC 界面特性向上

SiC 表面に高密度窒素プラズマで薄い窒化膜層を形成した後、熱酸化処理を施すことで、MOS 界面に効果的に窒素を供給する新規手法を提案した。界面構造評価及び MOS デバイスの電気特性評価結果から、窒化 SiC 表面の熱酸化で MOS 構造を形成した場合、界面での電気的な欠陥の起源と考えられるサブオキサイドあるいは Si-O-C 結合成分が減少し、界面欠陥準位密度が低減できることをでした。高温水素アニールを施したところ、従来報告値と比較して約1桁程度の界面準位密度の低減に成功した。(発表論文 [13])

## (4) 放射光光電子分光法による SiO<sub>2</sub>/SiC 界 面構造評価

SiC 表面酸化の素過程と、SiO<sub>2</sub>/SiC 界面原子 構造の理解は、従来の熱酸化 SiC-MOS デバ イスや我々が提案する High-k/SiO<sub>2</sub>/SiC スタ ック構造について共通の課題である。よって 本研究ではSiC表面酸化の素過程を放射光を 利用した高分解能 XPS によって詳細に評価 した。その結果、従来の報告に反し、SiC表 面の酸化によって原子スケールで急峻な MOS 界面が形成されることを示した。また SiO<sub>2</sub>/SiC 界面が Si-O 結合のみで構成されて いることを明らかにした。さらに、酸化の進 行に伴って SiO<sub>2</sub>/SiC 界面の急峻性は維持さ れるものの、原子層レベルの構造揺らぎが生 じ、その増加傾向と SiC-MOS デバイスの特 性劣化傾向が良く一致することを実験的に 示した。(発表論文 [1] [5])

## <u>(5)</u> 放射光光電子分光法による SiO₂/SiC 界 面のバンドアライメント評価

SiC デバイスでは、MOSFET の信頼性やリ ーク電流特性を決定する SiO<sub>2</sub>/SiC 界面での バンドアライメントの詳細な理解が進んで いない。また近年、Si面よりもキャリア移動 度が高い C 面を用いたデバイス試作が提案 されているが、信頼性劣化の問題が指摘され ている。本研究では放射光光電子分光技術を 駆使して、MOS 界面のバンドアライメント を評価した。その結果、SiO<sub>2</sub>/SiC 界面の伝導 帯のバンドオフセットは、Si 面に比べて C面 では低下しており、リーク電流成分の増大に 伴う信頼性劣化が本質的な問題となること を示した。さらに、欠陥起因の MOS 界面で のシートチャージの存在によってもバンド オフセットが変化し、高温水素ガスアニール などの欠陥終端処理は、C面の信頼性をさら に低下させることを明らかにした。これらの 結果は、トランジスタ応用を考慮した MOS 界面設計には重要な情報であり、界面物性の 観点からも非常に興味深い結果である(発表 論文 [2] [9])。

## (6) High-k/SiO2/SiC-MOS 構造の作製とその 最適化

反応性スパッタ法で形成した窒素添加アル ミナ (AlON) 絶縁膜は、従来の Al<sub>2</sub>O<sub>3</sub> 絶縁 膜で問題となっていた膜中固定電荷が発生 しないことを確認し、また各種物性解析結果 からワイドバンドギャップ SiC 半導体デバイ スに最適な絶縁膜材料であるとの結論に達 した。また我々の当初の予想通り、AION 絶 縁膜をSiC基板に直接堆積した場合には多量 の界面欠陥が発生するのに対して、界面 SiO<sub>2</sub> 層を挿入した積層構造ではこれらの問題が 解消できた。また熱酸化膜に代えて AION 絶 縁膜を用いることで、高温動作かつ高電界印 加時のリーク電流を飛躍的に低減すること に成功した。本結果は熱酸化 SiO<sub>2</sub> 絶縁膜で は本質的に解決不可能な数々の問題に対し て、最適化した AlON 絶縁膜の導入がその解 決策となることを明確に示す結果であり、本 研究課題の方向性が正しいことを改めて示 す重要な結果である。加えて、Al<sub>2</sub>O<sub>3</sub>絶縁膜 への窒素導入量と絶縁膜中の電荷トラップ 量との関係を明らかにし、絶縁膜中の窒素量 や AlON/SiO<sub>2</sub> スタックの構造最適化を完了 した。(発表論文 [10] [11] [15])

(7) 高性能 SiC-MOSFET の作製と性能評価 我々が提案する AlON/SiO2/SiC スタック構 造を有した SiC-MOSFET を試作し、その性 能評価を行った。特に、トランジスタ試作に 当って、他の High-k 絶縁膜に対して AlON 膜の高い耐熱性は非常に大きなアドバンテ ージであり、SiC デバイス作製工程で必要と される高温熱処理工程を施した後でも、高温 条件下でのリーク電流低減効果や絶縁特性、 さらには窒素添加による電荷トラップ抑制 効果が維持されることを確認した。さらに、 SiO<sub>2</sub>界面層に対して、上述の高密度窒素プラ ズマ処理や、高温水素アニールとの複合処理 を施して AlON/SiO<sub>2</sub>/SiC スタックを作製し、 これを搭載した SiC-MOSFET のデバイス性 能評価を行ったところ、従来の NOx 系酸化 プロセスで作製した SiO<sub>2</sub>/SiC スタックを有 したトランジスタに対して約1.6倍の移動度 向上とリーク電流低減を同時に達成した。 (発表論文 [10] [11] [15])

## (8) SiC-MOSデバイスの信頼性劣化要因の抽 <u>出とその対策の検討</u>

SiC-MOSFET の実用化では、高い信頼性を確保することが重要となる。しかし、Siデバイスに比べて SiC-MOS では絶縁破壊現象や絶縁膜中への電荷トラップ等のデバイスの信頼性を決定する様々な現象の理解が進んでいない。本研究期間の後半では、新規研究テーマとして、SiC-MOS デバイスの信頼性決定要因である以下の課題に取り組んだ。

(8)-① 導電性原子間力顕微鏡 (C-AFM) を用いた SiC-MOS デバイスのナノ領域の経時絶縁劣化の観測手法を新たに提案した。その結果、SiC 表面の熱酸化で形成した SiO2 絶縁膜は、微小領域内では Si-LSI のそれと同程度の信頼性が得られるが、SiC 基板の表面欠陥あるいは結晶欠陥に起因する Weak Spot が存在し、信頼性を低下させることが明らかとなった。(発表論文 [12])

(8)-② 上記の SiC-MOS デバイスの信頼性劣化を引き起こす原因として、SiC 基板の熱処理に伴うステップバンチングに関して、酸化に伴う構造変化を詳細に解析した。その結果、ステップバンチングが生じた SiC 表面では、平坦なテラス部分と、ステップバンチング端の酸化速度が大きく異なる為、熱酸化で形成される SiO $_2$  の物理膜厚に大きな揺らぎが発生し、SiC-MOS の信頼性を著しく劣化させることを明らかにした。(発表論文 [8])

(8)-③ SiC-MOS デバイスの製造工程では、各種のプラズマプロセスが採用されている。本研究では、プラズマからの紫外線照射がSiC-MOS デバイスの特性劣化を引き起こすことを明らかにした。この現象はSi-MOS デバイスでは軽微であることから、SiC 固有の問題であると言える。さらに、紫外線照射に伴う SiC デバイスの特性劣化は、波長依存性を有し、さらに高温条件下では劣化反応が加速されることを示した。(発表論文[3])

(8)-④ SiC-MOS デバイスでは、ナトリウム 等の不純物が混入しない条件下でも、イオン ドリフト現象が見られることを明らかにし た。これらの現象は SiC 熱酸化膜に特有であ り、深刻な問題である。これらのドリフトイ オンは、熱酸化後の高温熱処理(POA)によ り、その大半が消滅するが、MOS 界面の欠 陥終端を目的として実施される高温水素ア ニールで再び生成されることがわかった。こ れらの現象は、SiC 熱酸化膜のみで見られる ことから、炭素不純物起因であると推察され る。この問題に対する対策として、ドリフト イオン成分を MOS 構造の上部電極界面に高 温バイアス印加で集めた後に、SiO2絶縁膜の 最表層をウエットエッチングで取り除くこ とで、イオンドリフト現象を抑制できること を示した。(論文投稿中)

これらの研究成果は、国内外でも高く評価されており、本研究課題の最終年度(平成 23年度)だけでも、国際会議での3件の招待講演や、これらに関係したレビュー論文の執筆依頼があった。(学会発表 [2][3][5]および発表論文[4][6])

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

[雑誌論文](計15件)全て査読有

[1] H. Watanabe, T. Hosoi, T. Kirino, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, and T. Shimura, "Synchrotron Radiation Photoelectron Spectroscopy Study of Thermally Grown Oxides on 4H-SiC(0001) Si-Face and (000-1) C-Face Substrates", Mater. Sci. Forum 717-720 (2012) 697.

[2] T. Hosoi, T. Kirino, A. Chanthaphan, Y. Uenishi, D. Ikeguchi, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, and <u>H. Watanabe</u>, "Impact of Interface Defect Passivation on Conduction Band Offset at SiO<sub>2</sub>/4H-SiC Interface", Mater. Sci. Forum **717-720** (2012) 721.

[3] D. Ikeguchi, T. Kirino, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, T. Shimura, and <u>H. Watanabe</u>, "Impact of UV Irradiation on Thermally Grown 4H-SiC MOS Devices", Mater. Sci. Forum **717-720** (2012) 765.

[4] <u>H. Watanabe</u>, T. Hosoi, T. Kirino, Y. Uenishi, A. Chanthaphan, D. Ikeguchi, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, and T. Shimura, "Gate Stack Technologies for SiC Power MOSFETs", ECS Trans. **41** [3] (2011) 77.

[5] <u>H. Watanabe</u>, T. Hosoi, T. Kirino, Y. Kagei, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, and T. Shimura, "Synchrotron x-ray photoelectron spectroscopy study on thermally grown SiO<sub>2</sub>/4H-SiC(0001) interface and its correlation with electrical properties", Appl. Phys. Lett. **99** (2011) 021907.

[6] H. Watanabe, T. Kirino, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi and T. Shimura, "Impact of Stacked AlON/SiO<sub>2</sub> Gate Dielectrics for SiC Power Devices", ECS Trans. **35** [2] (2011) 265.

[7] H. Watanabe, H. Ohmi, H. Kakiuchi, T. Hosoi, T. Shimura, K. Yasutake, "Surface Cleaning and Etching of 4H-SiC(0001) Using High-Density Atmospheric Pressure Hydrogen Plasma", Journal of Nanoscience and Nanotechnology 11 (2011) 2802.

[8] T. Hosoi, K. Konzono, Y. Uenishi, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, H. Watanabe, "Investigation of

- Surface and Interface Morphology of Thermally Grown SiO<sub>2</sub> Dielectrics on 4H-SiC(0001) Substrates", Mater. Sci. Forum **679-680** (2011) 342.

- [9] H. Watanabe, T. Kirino, Y. Kagei, J. Harries, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, T. Shimura, "Energy Band Structure of SiO<sub>2</sub>/4H-SiC Interfaces and its Modulation Induced by Intrinsic and Extrinsic Interface Charge Transfer", Mater. Sci. Forum **679-680** (2011) 386.

- [10] T. Hosoi, Y. Kagei, T. Kirino, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, <u>H. Watanabe</u>, "Reduction of Charge Trapping Sites in Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Stacked Gate Dielectrics by Incorporating Nitrogen for Highly Reliable 4H-SiC MIS Devices", Mater. Sci. Forum **679-680** (2011) 496.

- [11] T. Hosoi, Y. Kagei, T. Kirino, Y. Watanabe, K. Kozono, S. Mitani, Y. Nakano, T. Nakamura, and <u>H. Watanabe</u>, "Improved Characteristics of 4H-SiC MISFET with AlON/Nitrided SiO<sub>2</sub> Stacked Gate Dielectrics", Mater. Sci. Forum **645-648** (2010) 991.

- [12] K. Kozono, T. Hosoi, Y. Kagei, T. Kirino, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, and <u>H. Watanabe</u>, "Direct Observation of Dielectric Breakdown Spot in Thermal Oxides on 4H-SiC(001) Using Conductive Atomic Force Microscopy", Mater. Sci. Forum **645-648** (2010) 821.

- [13] Y. Kagei, T. Kirino, Y. Watanabe, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, T. Shimura, and <u>H. Watanabe</u>, "Improved electrical properties of SiC-MOS interfaces by thermal oxidation of plasma nitrided 4H-SiC(0001) surfaces" Mater. Sci. Forum **645-648** (2010) 507.

- [14] H. Watanabe, Y. Watanabe, M. Harada, Y. Kagei, T. Kirino, T. Hosoi, T. Shimura, S. Mitani, Y. Nakano, and T. Nakamura, "Impact of a treatment combining nitrogen plasma exposure and forming gas annealing on defect passivation of SiO<sub>2</sub>/SiC interfaces", Mater. Sci. Forum 615-617 (2009) 525.

- [15] T. Hosoi, M. Harada, Y. Kagei, Y. Watanabe, T. Shimura, S. Mitani, Y. Nakano, T. Nakamura, and <u>H. Watanabe</u>, "AlON/SiO<sub>2</sub> Stacked Gate Dielectrics for 4H-SiC MIS Devices" Mater. Sci. Forum **615-617**(2009) 541.

〔学会発表〕(計 65 件) 国際会議 32 件 国内会議 33 件

- [1] A. Chanthaphan, T. Kirino, Y. Uenishi, D. Ikeguchi, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, T. Shimura, and <u>H. Watanabe</u>, "Insight into Bias-temperature Instability of 4H-SiC MOS Devices with Thermally Grown SiO<sub>2</sub> Dielectrics", 2012 MRS Spring Meeting, April 11 (2012), San Francisco, CA.

- [2] H. Watanabe, T. Hosoi, T. Kirino, Y. Uenishi, A. Chanthaphan, D. Ikeguchi, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, and T. Shimura, "Gate Stack Technologies for SiC Power MOSFETs (Invited)", 220th ECS Meeting, October 10 (2011), Boston, MA.

- [3] H. Watanabe, T. Hosoi, T. Kirino, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, and T. Shimura, "Synchrotron Radiation Photoelectron Spectroscopy Study of Thermally Grown Oxides on 4H-SiC(0001) Si-face and (000-1) C-face Substrates (Invited)", International Conference on Silicon Carbide and Related Materials, September 14 (2011), Cleveland, OH.

- [4] T. Hosoi, T. Kirino, A. Chanthaphan, Y. Uenishi, D. Ikeguchi, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, and <u>H. Watanabe</u>, "Impact of Interface Defect Passivation on Conduction Band Offset at SiO<sub>2</sub>/4H-SiC Interface" International Conference on Silicon Carbide and Related Materials, September 15 (2011), Cleveland, OH.

- [5] <u>H. Watanabe</u>, T. Kirino, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi and T. Shimura, "Impact of Stacked AlON/SiO<sub>2</sub> Gate Dielectrics for SiC Power Devices (Invited)", 219th ECS Meeting, May 3 (2011), Montreal, QC, Canada.

- [6] T. Kirino, Y. Kagei, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, T. Shimura, and <u>H. Watanabe</u>, "Energy Band Structure of Thermally Grown SiO<sub>2</sub>/4H-SiC Interfaces and its Modulation Induced by Post-oxidation Treatments", 41st IEEE Semiconductor Interface Specialists Conference, December 2 (2010), San Diego, CA.

- [7] T. Hosoi, Y. Kagei, T. Kirino, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, <u>H. Watanabe</u>, "Reduction of Charge Trapping Sites in Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Stacked Gate Dielectrics by Incorporating Nitrogen for

Highly Reliable 4H-SiC MIS Devices", 8th European Conference on Silicon Carbide and Related Materials, August 31 (2010), Oslo, Norway.

[8] H. Watanabe, T. Kirino, Y. Kagei, J. Harries, A. Yoshigoe, Y. Teraoka, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, and T. Shimura, "Energy Band Structure of SiO<sub>2</sub>/4H-SiC Interfaces and its Modulation Induced by Intrinsic and Extrinsic Interface Charge Transfer", 8th European Conference on Silicon Carbide and Related Materials, September 1 (2010), Oslo, Norway.

[9] Y. Kagei, T. Kirino, Y. Watanabe, S. Mitani, Y. Nakano, T. Nakamura, T. Hosoi, T. Shimura, and <u>H. Watanabe</u>, "Improved electrical properties of SiC-MOS interfaces by thermal oxidation of plasma nitrided 4H-SiC(0001) surfaces", International Conference on Silicon Carbide and Related Materials, October 13 (2009), Nürnberg, Germany.

[10] K. Kozono, Y. Kagei, T. Kirino, S. Mitani, Y. Nakano, Y. Nakamura, T. Hosoi, T. Shimura, and H. Watanabe, "Direct Observation of Dielectric Breakdown Spot in Thermal Oxides on 4H-SiC(0001) Using Conductive Atomic Force Microscopy", International Conference on Silicon Carbide and Related Materials, October 13 (2009), Nürnberg, Germany.

[11] H. Watanabe, Y. Watanabe, M. Harada, Y. Kagei, T. Kirino, T. Hosoi, T. Shimura, S. Mitani, N. Nakano, and T. Nakamura, "Impact of a Treatment Combining Nitrogen Plasma Exposure and Forming Gas Annealing on Defect Passivation of SiO<sub>2</sub>/SiC Interfaces", 7th European Conference on Silicon Carbide and Related Materials, September 10 (2008), Barcelona, Spain.

[12] T. Hosoi, M. Harada, Y. Kagei, Y. Watanabe, T. Shimura, S. Mitani, Y. Nakano, T. Nakamura, and <u>H. Watanabe</u>, "AlON/SiO<sub>2</sub> Stacked Gate Dielectrics for 4H-SiC MIS Devices", 7th European Conference on Silicon Carbide and Related Materials, September 11 (2008), Barcelona, Spain.

#### [図書] (計1件)

[1] 渡部平司 [分担執筆] (松波弘之、大谷昇、 木本恒暢、中村孝 編著)、日刊工業新聞社、 "半導体 SiC 技術と応用"、2011 年 9 月 30 日、pp. 293-297.

#### [産業財産権]

○出願状況(計4件)

名称:半導体装置およびその製造方法 発明者:<u>渡部平司</u>、志村考功、細井卓治、 箕谷周平、中野佑紀、中村亮太、中村孝

権利者:ローム(株)

種類:特許権

番号:特願 2012-039059 出願年月日:2012年2月24日

国内外の別:国内

名称:半導体装置

発明者:渡部平司、志村考功、細井卓治、

桐野嵩史、箕谷周平、中野佑紀

権利者:ローム(株)

種類:特許権

番号:特願 2009-206374 出願年月日:2009年9月7日

国内外の別:国内

名称: 半導体装置

発明者:渡部平司、志村考功、細井卓治、

桐野嵩史、箕谷周平、中野佑紀

権利者:ローム(株)

種類:特許権

番号:特願 2009-206373 出願年月日:2009年9月7日

国内外の別:国内

名称:半導体装置の製造方法および半導体装

置

発明者:渡部平司、志村考功、細井卓治、

桐野嵩史、箕谷周平、中野佑紀

権利者:ローム(株)

種類:特許権

番号:特願 2009-206372 出願年月日:2009年9月7日

国内外の別:国内

○取得状況(計0件)

[その他]

研究室ホームページ

http://www-asf.mls.eng.osaka-u.ac.jp/

#### 6. 研究組織

(1)研究代表者

渡部 平司(WATANABE HEIJI) 大阪大学・大学院工学研究科・教授

研究者番号:90379115