# 科学研究**費**補助金研究成果報告書

平成22年 5月18日現在

研究種目: 若手研究(B) 研究期間: 2007~2009 課題番号: 19700045

研究課題名(和文)フォールパス自動検出および過剰テスト緩和の合成システムに関する研究

研究課題名(英文)Automatic False Path Identification and Test Synthesis System Development to Avoid Overtesting

#### 研究代表者

史 又華 (SHI YOUHUA)

早稲田大学・IT研究機構・講師

研究者番号:70409655

研究成果の概要(和文):システム LSI の多機能化、高速化及び低消費電力化につれ、新たな問題点が明らかになってきた。その一つは、フォールスパスの遅延に関する解析・テスト合成設計である。本研究では、システム LSI 設計時間の短縮とテスト設計コストの削減のため、設計解析合成システムを構築し、その環境を活用して、次世代システム LSI 向けの解析・テスト技術の開発を行ってきた。特に、フォールスパス自動検出システムの開発及び過剰テストを考慮した遅延故障テスト技術に関する研究を行ってきた。

研究成果の概要 ( 英文 ): The progress of design and manufacturing technology of LSIs makes it possible to realize more functional blocks into a chip with high speed and low power consumption. However it also leads to many new design challenges and one of them is the design and test technique due to the existence of false paths in the designs. Therefore in this research, a new analysis and test synthesis system was developed for the low cost design and test of next-generation LSIs, and with the use of this system novel test techniques, more specifically response compaction techniques and non-overtesting delay test methods, were developed.

### 交付決定額

(金額単位:円)

|        | 直接経費      | 間接経費    | 合 計       |

|--------|-----------|---------|-----------|

| 2007年度 | 1,300,000 | 0       | 1,300,000 |

| 2008年度 | 800,000   | 240,000 | 1,040,000 |

| 2009年度 | 1,100,000 | 330,000 | 1,430,000 |

| 年度     |           |         |           |

| 年度     |           |         |           |

| 総計     | 3,200,000 | 570,000 | 3,770,000 |

研究分野:総合領域

科研費の分科・細目:情報学・計算機システム・ネットワーク

キーワード:設計自動化、回路とシステム、VLSI設計技術、回路設計・CAD

#### 1.研究開始当初の背景

半導体技術の進歩は目覚ましくなり、2004年の時点で既に 90nm プロセスが実用された。90nm プロセスにおいては、1 チップ上に約2億個のトランジスタを実現することができ、非常に高機能なシステム LSI が実現できる。しかし、システム LSI の多機能化、高速化及び低消費電力化につれ、新たな問題点が明らかになってきた。その一つは、フォールスパスの遅延に関する解析・テスト合成設計である。

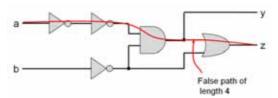

図1.フォールスパスの例

フォールスパス(図1参照)とは、回路の 接続はなされているものの、冗長な回路など が原因で論理的に信号が伝播しないような 経路のことを指す。既存の論理合成ツールは、 入力された RTL 記述だけでは、どのパスがト ゥル・パスで、どのパスがフォールスパスか については判定できない。そのため論理合成 ツールは、全てのレジスタ - レジスタ間、入 出力ピン - レジスタ間のパスをトゥル - パ スとみなしてパスの遅延最適化を行う。しか し、中には遅延最適化を行う必要のないフォ ールスパスについても最適化し、回路の面積 を増加させてしまうことがある。そのため、 最適化に長い時間を必要とし、配置・配線が 収束しないなどが課題になる。一方、フォー ルスパスは、本来テスト不可能なパスであり、 テスト容易化設計のことによって、テストさ れてしまうことと言い、それは過剰テストと も呼ぶ。結果的には、歩留まりが悪くなり、 良品を不良品と判断してしまうなどの悪影 響に及ぼす。

上記の背景を基に、システム LSI 設計時間の短縮とテスト設計コストの削減を目的にフォールスパス自動検出及び過剰テスト緩和の合成システムについて研究を行ってきた。

# 2.研究の目的

フォールスパスの解析に関する研究は、 1980年代頃から始まってから、多くの研究者 によって絶えずに続かれている。その中、古 いものでは文献[1]、新しいのものでは文献 [2]などがある。

[1] D. Brand and V. Iyengar, Timing

Analysis Using Functional Analysis, IEEE transactions on Computers, Vol.37, No.10, pp. 1309-1314, October 1988.

[2] V. Vorisek, B. Swanson, K. Tsai, and D. Goswami, Improved Handling of False and Multicycle Paths in ATPG, Proc. of IEEE VLSI Test Symposium, pp. 160-165, May 2006.

しかし、それらの研究結果を利用したフォールスパス解析は実際の設計ではあまり利用されていない。原因の一つは、従来の研究はゲートレベル解析手法で行われるものが多い。ゲートレベル解析手法で行われるをの数え上げでの組み合わるとが表したり処理時間が長くなる点にある。その理しきれないほど多く、フォールスパス制を自動されることが多り、フォールスパス制度といるでは、利用しやすさという点が考慮されていないという問題点もある。すなの問題が考慮されていなかった。

本研究は、主に2つの目的がある。1つ目は、タイミングを重視した設計フローの中に実用的なフォールスパス自動検出およびュータ上での自動設計環境構築を実現することである。2つ目は、構築された合成アルゴリズムでは、RTL レベル HDL コードから、ダイミング解析と有効テスト合成の融合がでラング解析と有効テスト合成の融合がでコンピュータで実装し、システム LSI を設計・テストすることによって、アルゴリズムの有効性を評価することである。

#### 3.研究の方法

本研究では、システム LSI 設計時間の短縮とテスト設計コストの削減のため、設計解析合成システムを構築し、その環境を活用して、次世代システム LSI 向けの解析・テスト技術の開発を行ってきた。特に、フォールスパス自動検出システムの開発及び過剰テストを考慮した遅延故障テスト技術に関する研究を行ってきた。

### (1) フォールスパス自動検出解析合成 システム

構築したシステムは、大別に3つの要数から構成される。 タイミング解析モデル、特にトランジッションモードとフローティングモードに焦点を当て、パス活性化条件の考案、 パス活性化情報抽出アルゴリズムの構築、 フォールスパス自動検出アルゴリズムの確立。以上のアルゴリズムをコンピュータに実装し、評価実験を行った。

### (2) 過剰テストを考慮した次世代遅延 テスト技術

次世代遅延テスト技術に関しては、主に以下の研究を行った。 フォールスパス上の遅延故障および過剰テストの影響の考察、 テスト不要パスの判定アルゴリズムの確立、有効テスト合成アルゴリズムの構築、 テスト不要な遅延故障および過剰テストの影響を考慮した、遅延テスト手法を実装し、実際の大規模集積回路に適用し評価実験を行った。

# 4. 研究成果

本研究では、次世代システム LSI 向けの解析・テストに関する研究を行ってきた。具体的には、以下の 2 項目について研究を行い、それぞれ以下に示す成果をあげた。

(1)「フォールスパス自動検出システム」に関する研究開発:タイミングを重視した設計フローの中で、実用的なフォールスパス解析が自動で実現させる技術を開発することが目標である。研究成果として、フォールスパス自動検出システムの開発を行ってきた。構築したフォールスパス自動検出システムを様々なサンプルRTLレベルVerilog HDLに適用され、フォールスパス検出機能の効果が確認できて、精度・有効性を評価された。

「クロック経路自動認識」に注目し、マルチクロークドメインに対してフォールスパス自動検出機能を実現され、効果を確認できた。また、本研究成果の一部を暗号回路に応用し、効果を示した。 テストパタン自動生成ツールと連携し、有効テストカバレッジ向上またはテストパタン生成時間大幅に減ることができた。

(2)「過剰テスト緩和のため有効遅延故障 テスト設計手法」に関する研究:次世代シス テム LSI を対象に、設計の品質・効率を向上 させると共に、新たなテスト設計手法に関す る研究を行った。具体的には、 システム LSI 向け低コストと高いテストの品質を両立さ せるテスト手法を提案した。研究結果として、 テストの品質を保証することで、最先端のス キャンテスト設計手法と比較してテスト・デ ータの量とテスト時間を最大で25 分の1 までに削減できた。さらに、テストコストの 大幅な削減も達成できた。 VLSI 製造技術・ 設計技術の進歩により、遅延故障テストが重 要になってきた。しかし、回路規模が大きく なるとパス数が急増しており、本来回路には 通常動作に影響を与えない遅延故障 (テスト

不要な故障)をテストすることになり、LSI 製造における歩留りの低下する可能性があ る。また、全てのテスト不要なパスを高速検 出するには非現実的である。この問題を解決 するに当って、開発した「フォールスパス自 動検出システム」を利用し、フォールスパス 上の遅延故障および過剰テストの影響につ いて考察し、テスト不要パスの判定アルゴリ ズムを確立され、評価実験を行い、新たな遅 延故障テスト手法を提案した。 テスト不要 なパスに生じる不定値(X)の影響による故障 検出効果の低下である。この問題を解決する に当って、開発した「フォールスパス自動検 出システム」を利用し、テスト不要な遅延故 障および過剰テストの影響について考察し、 故障検出効果の低下を見積ることによって、 不定なテスト応答値(Unknown responses) をマスキング回路の適正な構成を提案した。 実際の大規模集積回路に適用し有効性を確 認した。

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### 〔雑誌論文〕(計3件)

Youhua Shi, Nozomu Togawa, Masao Yanagisawa and Tatsuo Ohtsuki, X-Handling for Current X-Tolerant Compactors with More Unknowns and Maximal Compaction, IEICE Trans. on Fundamentals of Electronics Communications and Computer Science, Vol. E92-A, No.12, 2009, pp. 3119-3127. (查読有)

Youhua Shi, Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, A Unified Test Compression Technique for Scan Stimulus and Unknown Masking Data with No Test Loss, IEICE Trans. on Fundamentals of Electronics Communications and Computer Science, Vol. E91-A, No.12, 2008, pp.3514-3523. (查読有)

Youhua Shi, Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, A Secure Test Technique for Pipelined Advanced Encryption Standard, IEICE Trans. on Fundamentals of Electronics Communications and Computer Science, Vol. E91-D, No.3, 2008, pp. 776-780. (査読有)

### 〔学会発表〕(計5件)

<u>Youhua Shi,</u> Nozomu Togawa, Masao Yanagisawa and Tatsuo Ohtsuki, Design-for-Secure- Test for Crypto Cores, Proc. of IEEE International Test Conference (ITC), Poster 11, October 2009, Austin, USA.

Youhua Shi, Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, Handling More X s Using Current X-Tolerant Compactors with Maximal Compaction, IEEE European Test Symposium (ETS), May 2009, Sevilla, SPAIN. (poster 発表)

Youhua Shi, Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, X-Eliminator: A Technique to Mask All Unknown Responses with No Test Loss and Minimized Masking Data Overhead, Proc. of 16th IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SOC), pp. 563-568, October 2008, Rhodes Island, Greece. <u>Youhua Shi,</u> Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, GECOM: Test Data Compression Combined with All Unknown Response Masking. Proc. of IEEE Asia and South Pacific Automation Conference Design (ASP-DAC), pp. 577-582, January 2008, Seoul, Korea.

Youhua Shi, Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, Design for Secure Test -- A Case Study on Pipelined Advanced Encryption Standard, Proc. of IEEE International Symposium on Circuits and Systems (ISCAS), pp.149-152, May 2007, New Orleans, USA.

#### 6.研究組織

(1)研究代表者

史 又華 (SHI YOUHUA)

早稲田大学・IT研究機構・講師

研究者番号:70409655