# 科研費

## 科学研究費助成事業 研究成果報告書

令和 6 年 6 月 4 日現在

機関番号: 14301 研究種目: 若手研究 研究期間: 2020~2023

課題番号: 20K19770

研究課題名(和文)データ駆動型社会に向けた大容量高速メモリキューブ・ネットワークの研究

研究課題名(英文)Research on large-capacity high-speed memory-cube networks for a data-driven society

### 研究代表者

安戸 僚汰 (Yasudo, Ryota)

京都大学・情報学研究科・助教

研究者番号:00846941

交付決定額(研究期間全体):(直接経費) 3,300,000円

研究成果の概要(和文):本課題では,大容量かつ高速,スケーラブルなメモリキューブネットワークを研究した.メモリキューブネットワーク特有の設計制約を満たした中で,直径および平均距離が最小であるようなトポロジとして二重対角メッシュを提案した.また,二重対角メッシュ向けのルーティングを提示し,それが最短経路を常に通りデッドロックフリーであることを証明した.最後に,パイプラインの一部を省略できるルータアーキテクチャを設計し,どのパイプラインステージを省略すべきかを提示した.ネットワークシミュレーションおよびハードウェア評価で提案手法の優位性を明らかにした.

研究成果の学術的意義や社会的意義レイアウトとリンク長,次数の厳しい設計制約がある場合の最適なトポロジを明らかにしたことはメモリキューブネットワークが台頭してきた中で学術的に価値がある. さらにルーティング,ルータアーキテクチャまで一貫して提案したため理論的意義と実践的意義の双方が含まれる. ディープラーニングやビッグデータ解析に代表される近年のアプリケーションにおいて,計算機のメモリ容量の要求は増加している.クラウドプラットフォームにおいて要求されるメモリ量は2015年頃から急速に増加している.そのため,提案するメモリキューブネットワークは大量のデータを扱う重要なアプリケーションを高速動作させる基盤技術として社会的意義がある.

研究成果の概要(英文): In this project, we have studied a large-capacity, high-speed, and scalable memory-cube network. Within the design constraints of memory-cube networks, we have proposed the Dual Diagonal Mesh (DDM) as a topology that minimizes both diameter and average distance. Additionally, we have presented a routing method for DDM, proving that it always uses the shortest path and is deadlock-free. Finally, we have designed a router architecture that can omit part of the pipeline stages and identified which pipeline stages should be omitted. Through network simulations and hardware evaluations, we have demonstrated the superiority of the proposed method.

研究分野: 並列計算機アーキテクチャ

キーワード: 相互結合網 メモリキューブネットワーク トポロジ ルーティング ルータアーキテクチャ

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

## 1.研究開始当初の背景

ディープラーニングやビッグデータ解析に代表されるアプリケーションによって計算機が扱うデータ量が増え、メモリ容量の増加が要求されている。たとえば Amazon Web Services (AWS) で提供されるクラウドサーバーや Microsoft のクラウドプラットフォームにおいて要求されるメモリ量は 2015 年頃から急速に要求が増加し、2018 年では約 6TB になっていることが報告されている。従来のメモリは計算機のソケットと呼ばれるスロットに搭載する。メモリの大容量化のためにはソケットを増設する必要があるが、そうするとコストの増加と速度の低下を招くという問題がある。

そこで新しいメモリ技術としてメモリキューブが提唱されている.これは三次元積層されたメモリで、メモリコントローラやルーティングの論理回路を最下層に置き、その上に複数のメモリチップを積層する.メモリキューブの最大の特徴は、ソケットに直接挿すのではなく、論理層にあるスイッチを使ってメモリキューブ間で結合網を構成する点である.これによってソケット数を増やすことなくメモリ容量と性能を高めることができる.このメモリキューブ間の結合網、メモリキューブネットワークをどう構成すべきかを探究するのが本研究、ということになる.

#### 2.研究の目的

メモリキューブネットワーク特有の設計制約を元に,従来の相互結合網とは異なる独自のトポロジ,ルーティングアルゴリズム,ルータアーキテクチャを提案し評価する.設計制約は,メモリキューブとプロセッサがグリッド状に配置されること,リンク長の長さがマンハッタン距離で2以下であること(先行研究に準拠),メモリキューブのポート数が4以下であること(商用化されたメモリキューブである HMC の仕様に準拠)である.これらの設計制約を満たすような結合網は,メニーコアプロセッサ/データセンタ/スーパーコンピュータを対象としていた従来の結合網とは性質が異なるものとなるので,新たに提案する.特に,設計制約下でメモリキューブ間の直径や平均距離の下界や,それに一致する最適なネットワークを提唱することを目的とする.これにて理論的に最適な相互結合網の提案ができる.その後,実際のアプリケーションのトラフィックを流した時の遅延やスループットを評価し,さらにはルータをハードウェア設計しその動作周波数や面積を評価することで,実験的・工学的にも提案手法の優位性を示す.

## 3.研究の方法

#### (1) トポロジの提案

トポロジについては数学的なモデルで議論できる.メモリキューブネットワークと設計制約, 直径,平均距離を定義した上で,直径と平均距離が下界と一致するようなトポロジを設計する. 具体的には,伝統的な相互結合網の研究におけるムーアグラフの考え方と,グリッドグラフの考え方をメモリキューブネットワークに当てはめることでこれを可能とする.

## (2) ルーティングアルゴリズムの提案

提案するトポロジに対し,ルーティングアルゴリズムを考案する.最短経路であることとデッドロックフリーであることを目標とする.デッドロックフリーであることは,仮想チャネルを考慮したチャネル依存グラフにサイクルがないことを示すことで証明する.

## (3) ルータアーキテクチャの提案

経路計算(RC), 仮想チャネル割当(VA), スイッチ割当(SA), スイッチ通過(ST) からなるパイプラインルータを元に,パイプラインステージを省略できるバイパスを追加する.省略の仕方によって,複数のルータアーキテクチャが考えられる.それぞれハードウェア記述言語で設計,論理合成し,動作周波数と面積を評価する.

## (4) ネットワークの評価

ランダムトラフィックおよび NAS parallel benchmark からトレースしたトラフィックを用いて,ネットワークシミュレーションを行う.トレースにはメモリキューブネットワークを模擬するよう拡張した gem5 シミュレータを用いる. BookSim シミュレータを用いることで,ネットワーク負荷(注入パケット率)を変化させたときの遅延とスループットを測定する.バイパスパイプラインに対しても評価できるように BookSim シミュレータを拡張する.最後に,ルータの動作周波数を加味した実時間の遅延を見積もる.

## 4. 研究成果

## (1) 二重対角メッシュの提案

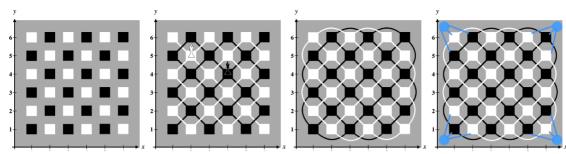

メモリキューブネットワークに対して二重対角メッシュと呼ぶ新しいトポロジを提案した. 二重対角メッシュはグリッド上に配置され,図のように4つのステップから構成することができる.ステップ1では,四角で表すメモリキューブをグリッド上にならべ,チェスボードのよう

図 1. 提案する二重対角メッシュの構成法 (左から 4 ステップで構成可能)

に白と黒に分ける.ステップ2では,二つの対角メッシュを構成する.それぞれ白のメモリキューブと黒のメモリキューブのみを含んでいるため,白対角メッシュ,黒対角メッシュと呼ぶ.白対角メッシュと黒対角メッシュは連結しておらず,ここが二重対角メッシュの最大の特徴といえる.ステップ3では周辺のメモリキューブを結合させる.最後にステップ4において,丸で表すプロセッサを接続する.

以上のステップで構成される二重対角メッシュメッシュは、「研究の目的」で既に述べた設計制約において直径・平均距離が最適(下界に一致)することを数学的に証明した(発表論文を参照のこと)、ムーアグラフの議論を応用することで容易に証明できる、設計制約のどちらの影響が大きいかというと、リンク長の制限の方が厳しいということがわかった、n×n のサイズの二重対角メッシュの直径、平均距離はそれぞれn、(2^3 + n^2 + 8n + 8)/(4n^2 + 12)となる、

## (2) 決定的・最短経路・デッドロックフリールーティングの提案

二重対角メッシュに対し決定的かつ最短経路かつデッドロックフリーのルーティングアルゴリズムを提案した.二重対角メッシュメッシュは直径・平均距離が小さいのみならず,チャネル依存関係がシンプルという特徴を持っている.これにより極めて単純な決定的ルールに基づいてルーティングアルゴリズムを設計することができた.

提案するルーティングアルゴリズムは常に最短経路をとり,デッドロックが生じないことを証明した.デッドロックが生じないことは,チャネル依存グラフに基づいたデッドロックフリーの条件に基づいて示すことができる.

## (3) ルータアーキテクチャの提案

上述したように,提案するルーティングアルゴリズムはチャネル依存関係がシンプルである.この特徴を活用して,ルータのパイプラインの一部を省略するアーキテクチャを提案した.省略する条件は二つあり,一つ目はチャネル依存グラフにおいてあるノード(チャネルに対応)の出次数が1のとき,対応するチャネルを使った転送は経路計算(RCステージ)を省略できるというものである.二つ目として,チャネル依存グラフにおいてあるノードの入次数が1のとき,対応するチャネルを使った転送は仮想チャネル・スイッチの割り当てを省略できる.このようにパイプラインステージの一部を省略する信号パスをルータ内に設定することができる.このような信号パスをバイパスパイプラインと呼び,これを持つルータをバイパスパイプラインルータと呼ぶ

本研究では、ハードウェアコストを節約するため、高々一種類のバイパスパイプラインを持つルータを考える。よって、考えられるルータアーキテクチャとしては、バイパスパイプラインのないルータ、RC ステージを省略するバイパスパイプラインを持つルータ、VA/SA ステージを省略するバイパスパイプラインを持つルータ、RC/VA/SA ステージを省略するバイパスパイプラインを持つルータの四つのルータがある。それぞれ設計し評価を行った。

#### (4) 評価

BookSimシミュレータを用いたネットワークシミュレーションの結果,二重対角メッシュトポロジのメモリキューブネットワークはメッシュ,トーラス,先行研究である対角メモリキューブネットワークに対して最大45.2%遅延が小さいことを示した.バイパスパイプラインルータを用いると,さらに18.7%遅延を削減できることを示した.NASパラレルベンチマークのトラフィックを用いた評価では,VA/SAステージのみを省略するバイパスパイプラインルータが最も遅延削減率が小さいことがわかった.これは,削減するクロックサイクル数が少ない一方で,バイパスパイプラインを使う確率が高いためである.

ハードウェア評価の結果,バイパスパイプラインの面積オーバヘッドは 20~30%程度であり,動作周波数の悪化はないことがわかった.動作周波数を考慮して遅延を計算しても,ネットワークシミュレーションの結果を覆す変化はなく,結論として VA/SA ステージのみを省略するバイパスパイプラインルータが最も遅延削減率が小さいといえる.

# (5) まとめ

以上のように,トポロジの設計からハードウェア実装に基づいた評価に至る一貫した研究を本研究課題において遂行することができた.トポロジおよびルーティングについては理論的に最適なものを示した一方,ルータアーキテクチャについてはまだ改善する余地が残されている.また,設計制約を変えた場合の最適なネットワークは違うものとなると考えられるため,将来の研究に譲る.

#### 5 . 主な発表論文等

【雑誌論文】 計1件(うち査読付論文 1件/うち国際共著 0件/うちオープンアクセス 1件)

| 「粧碗調文」 司一件(ひら直読性調文 一件/ひら国際共者 サイノングクイーノンググセス 一件)                                      |           |

|--------------------------------------------------------------------------------------|-----------|

| 1.著者名                                                                                | 4 . 巻     |

| Yasudo Ryota、Nakano Koji、Koibuchi Michihiro、Matsutani Hiroki、Amano Hideharu          | e6115     |

|                                                                                      |           |

| 2.論文標題                                                                               | 5 . 発行年   |

| Designing low diameter interconnection networks with multi ported host switch graphs | 2020年     |

|                                                                                      |           |

| 3.雑誌名                                                                                | 6.最初と最後の頁 |

| Concurrency and Computation: Practice and Experience                                 | 1-17      |

|                                                                                      |           |

|                                                                                      |           |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                              | 査読の有無     |

| 10.1002/cpe.6115                                                                     | 有         |

|                                                                                      |           |

| <b>  オープンアクセス</b>                                                                    | 国際共著      |

| オープンアクセスとしている(また、その予定である)                                                            | -         |

## 〔学会発表〕 計6件(うち招待講演 0件/うち国際学会 2件)

# 1.発表者名

Ryota Miyagi, Ryota Yasudo, Kentaro Sano, and Hideki Takase

2 . 発表標題

Elastic Sample Filter: An FPGA-based Accelerator for Bayesian Network Structure Learning

3 . 学会等名

International Conference on Field Programmable Technology (国際学会)

4 . 発表年 2022年

#### 1.発表者名

慶田開,安戸僚汰,高木直史

2 . 発表標題

配線長制限下での平均ホップ数および直径が最小のメモリキューブネットワーク

3 . 学会等名

組込み技術とネットワークに関するワークショップ ETNET2023

4.発表年

2023年

1.発表者名

額見怜央,安戸僚汰,高木直史

2 . 発表標題

深層強化学習を用いた発見的二次無制約二値最適化ソルバーの学習

3 . 学会等名

組込み技術とネットワークに関するワークショップ ETNET2023

4.発表年

2023年

| 1.発表者名<br>飯田智子,安戸僚汰,高木直史                             |

|------------------------------------------------------|

| 2.発表標題<br>Graph Pointer Networkによる距離行列TSPおよびQAPの高速解法 |

| 3.学会等名<br>組込み技術とネットワークに関するワークショップ ETNET2023          |

| 4.発表年                                                |

1.発表者名

2023年

Masashi Oda, Kai Keida, and Ryota Yasudo

2 . 発表標題

Dual Diagonal Mesh: An Optimal Memory Cube Network Under Geometric Constraints

3 . 学会等名

International Symposium on Computing and Networking(国際学会)

4 . 発表年 2023年

1.発表者名

織田雅史,安戸僚汰,高木直史

2 . 発表標題

二重対角メッシュメモリネットワークにおけるルーティング手法の検討

3 . 学会等名

電子情報通信学会技術研究報告

4.発表年

2023年

〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6 . 研究組織

| Ο, |                           |                       |    |

|----|---------------------------|-----------------------|----|

|    | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

## 7. 科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

# 8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|