## 科学研究費助成事業 研究成果報告書

平成 26 年 5 月 22 日現在

機関番号: 14301 研究種目: 基盤研究(S) 研究期間: 2009~2013

課題番号: 21226008

研究課題名(和文)炭化珪素半導体の欠陥制御と超高耐圧ロバスト素子への応用

研究課題名(英文)Defect Engineering in SiC and Application to Robust Devices with Ultrahigh Blocking Voltage

#### 研究代表者

木本 恒暢 (Kimoto, Tsunenobu)

京都大学・工学(系)研究科(研究院)・教授

研究者番号:80225078

交付決定額(研究期間全体):(直接経費) 156,500,000円、(間接経費) 46,950,000円

研究成果の概要(和文):電力系統や高圧電源に用いられる高効率電力変換用パワーデバイスの実現を目指し、炭化珪素(SiC)半導体に関する材料科学と超高耐圧デバイスの基礎研究を遂行した。主な成果として、高純度結晶の作製、拡張欠陥の構造および物性の解明、拡張欠陥の非破壊高速検出、深い準位の物性解明、キャリア寿命キラー欠陥の大幅な低減とキャリア寿命の増大、キャリア寿命制御、超高耐圧を可能とする接合終端構造および設計指針の提示、絶縁破壊機構に関する考察、固体素子として最高の超高耐圧(20kV以上) SiC PiNダイオードおよびバイポーラトランジスタの作製、特性解析と高温動作(300)の実証を達成した。

研究成果の概要(英文): Defect electronics in SiC and ultrahigh-voltage SiC power devices have been studie d toward efficient electric power conversion employed for future smart grids. Fast epitaxy of high-purity SiC was developed, and extended defects in SiC epitaxial layers were systematically characterized. Physica I properties of the major deep levels were elucidated. The carrier-lifetime killer defects could be elimin ated, leading to remarkably enhanced carrier lifetimes. Control of carrier lifetimes was also achieved. Or iginal junction-termination structures were proposed to achieve ultrahigh blocking voltage with SiC, and b reakdown mechanism of SiC devices was discussed. By utilizing thick, lightly-doped SiC epitaxial layers and the original device structures, ultrahigh-voltage (> 20 kV) PiN diodes and npn bipolar transistors were realized. The performance was significantly improved by enhancement of carrier lifetimes, and high-tempera ture operation of SiC devices was demonstrated.

研究分野: 工学

科研費の分科・細目: 電気電子工学・電子・電気材料工学

キーワード: 半導体 パワーデバイス 結晶欠陥 キャリア寿命 絶縁破壊

#### 1. 研究開始当初の背景

- (1) 省エネルギーの重要性が益々高まってい る現在、発電所や変電所における大規模電力 変換システムでは、変換電力の実に 5~10%に 相当する膨大なエネルギーが熱として排出 されている。この主な原因は、電力変換機器 の中核を担う高耐圧(~6 kV) Si サイリスタと PiN ダイオードの性能限界にある。配電に使 われる典型的な交流電圧は 6.6 kV であり、 この電力変換には耐圧 13~20 kV のスイッチ ング素子とダイオードが必要となる。現状で は 6 kV 級の Si 素子を多段接続して 20 kV の 耐圧を得ているが、導通時の電力損失や発熱 が大きい、スイッチング周波数が極めて遅い、 発熱による素子破壊を防ぐために莫大な水 冷設備が必要である等の深刻な問題を抱え ている。

- (2) 本研究で取り扱う炭化珪素(SiC)は、Siに比べて絶縁破壊電界強度が約 10 倍、禁制帯幅と熱伝導率が約 3 倍という優れた物性を持ち、しかも広範囲の伝導性制御(n型、p型とも)が容易な間接遷移型半導体であるので、Siでは到達できない超高耐圧(> 20 kV)の高性能バイポーラデバイス(サイリスタ、PiN ダイオード等)を実現できる。しかしながら、SiC を用いた高耐圧バイポーラデバイスを実現するためには、材料およびデバイスの両面において多くの課題が山積している。

### 2. 研究の目的

本研究では、SiC を用いた超高耐圧かつ高温動作デバイス実現を目指して、その材料物性(欠陥と物性制御)とデバイス物理に関する学術的研究を行う。具体的な目的は以下の通りである。

- (1) SiC 成長層に存在する主要な拡張欠陥および点欠陥を多角的に評価し、その種類、構造、および物性を明らかにする。

- (2) SiC におけるキャリア寿命制限因子の特定とその低減を通じて、キャリア寿命を大幅に増大させると共に、キャリア寿命制御を実現する。

- (3) 実験とシミュレーションにより、超高耐圧デバイスに有効な電界集中緩和構造や表面保護法を確立し、耐圧 20 kV 以上の SiC PiN ダイオードを実現して特性を評価する。

#### 3. 研究の方法

(1) 独自に作製する高純度 SiC 厚膜エピタキシャル結晶を用い、多角的かつ系統的評価手法を駆使して、拡張欠陥および点欠陥の検出、 欠陥構造と起源の解明を進め、さらにキャリ

- ア生成・再結合等の欠陥物性を明らかにする。 また、超高耐圧デバイスの性能を支配するキャリア寿命を測定し、様々な欠陥との相関からその制限要因を特定する。

- (2) 次に、電界集中緩和構造の設計や良質の表面保護膜形成等の要素技術を集約して超高耐圧(> 20 kV)ロバスト PiN ダイオードやトランジスタを作製する。絶縁破壊機構や素子内でのキャリアダイナミクスを明らかにし、耐圧の極限を追究する。

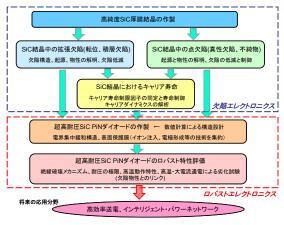

本研究で取り組む研究計画の概要(模式 図)を図1に示す。本研究では、SiC 半導体 における点欠陥(深い準位)、拡張欠陥、表面/ 界面再結合の影響を解明すると共に、バイポ ーラデバイス応用を見据えてキャリア寿命 制御を実現することを目指している。これら 欠陥の構造と物性の解明およびその制御は、 材料科学から電子工学に亘る「ワイドギャッ プ半導体の欠陥エレクトロニクス」の発展に 寄与する。さらに、10kV以上の超高耐圧デ バイスの作製と高温動作を含めた特性解析 は未踏領域であり、「ロバストエレクトロニ クス」の発展に寄与する。なお、研究内容お よび体制としては、SiC 半導体に関する材料 からデバイスまでの垂直統合型研究を効率 的に遂行することができる研究組織となっ ている。

図1 研究計画の概要

#### 4. 研究成果

- (1) 自作の化学気相堆積(CVD)装置を用いて、気相でのSi重合反応を抑制することにより、従来に比べて6倍以上高い成長速度(85µm/h)で表面平坦性に優れたSiC厚膜(> 150µm)の形成に成功した。残留不純物密度は1×10<sup>13</sup>cm<sup>-3</sup>以下であり、化合物半導体として例外的に高純度の結晶を得た。

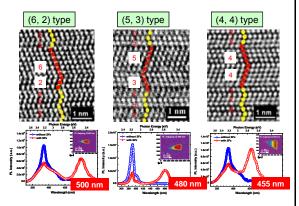

- (2) SiC成長層内の主要な積層欠陥の三次元的 構造を同定し、各々の積層欠陥の光学的性質 を明らかにした。積層欠陥はSiC結晶内で量子

井戸的振舞いを示し、各々の積層構造に応じた特徴的な発光ピークを示すことを明らかにした(一例を図2に示す)。フォトルミネセンス(PL)マッピングあるいはPLイメージング測定により、非破壊に積層欠陥の箇所とその種類を同定できることを示した。

図2 SiC成長層に存在する主要な積層欠陥の断面TEM像とPLスペクトル(赤色のスペクトルが積層欠陥、青色が積層欠陥の無い領域からのPL). 積層欠陥特有の発光.

- (3) SiC成長層に存在する積層欠陥の大半は成長初期に生成していることを明らかにし、成長初期条件を工夫することにより、高速成長時の積層欠陥密度を従来の約10cm<sup>-2</sup>から1cm<sup>-2</sup>以下に低減した。

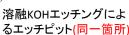

- (4) SiC結晶中の転位が特異な近赤外発光を示すことを活用することで、初めてSiC成長層内の全ての転位の非破壊検出/判別に成功した。転位の種類によって、発光パターンや発光スペクトルが異なるので、転位の種類(貫通らせん転位、貫通刃状転位、基底面転位)の判別も可能である(図3)。

PLイメージング像 (@880 nm)

TSD: 貫通らせん転位 TED: 貫通刃状転位

図3 SiC成長層の近赤外(880nm)における PLイメージング像(左)と同一箇所の転位 ピット(右). 一対一の対応を確認.

(5) SiC結晶中の転位がキャリア再結合に及ぼす影響を時間分解PLイメージング測定によって定量的に調べ、基底面転位が最もキャリア寿命に悪影響を与えること、貫通刃状転位

の影響は小さいことを明らかにした。

(6)低温から超高温(850K)まで測定できるDLTS (深い準位分析法)を構築し、かつドーピング密度の異なるn型およびp型SiC成長層を作製することにより、SiCの禁制帯幅内に存在するほぼ全ての深い準位を検出することに成功し、その基本的性質(エネルギー準位、捕獲断面積、熱的安定性など)を系統的に明らかにした。

- (7) SiC結晶にデバイス作製時に必須のイオン注入やドライエッチングを施した時に生成される深い準位を全て検出し、その基本的性質を明らかにした。主要な欠陥の起源は特定の不純物を含まない真性欠陥(特に炭素空孔を含む欠陥)であることが分かった。また、これらの欠陥密度を熱酸化とAr=ールの組み合わせにより桁違いに低減できることを示した。(8) n型SiCにおけるキャリア寿命キラー欠陥である $Z_{1/2}$ センター(伝導帯底から0.63eVの深い準位)の起源をDLTSと電子スピン共鳴実験により調べ、これが孤立した炭素空孔のアクセプタ準位によるものであることを解明した。SiCにおいて深い準位の起源を同定したのは、本研究が初めてである。

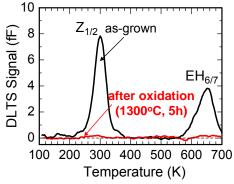

- (9) SiC結晶を熱酸化することにより、SiC成長層中の主要な深い準位をほぼ消滅(<1×10<sup>11</sup>cm<sup>-3</sup>)させることに成功した(図4)。これは、熱酸化時に酸化界面から放出された過剰な炭素原子がバルク結晶中に拡散し、炭素空孔を埋めることで炭素空孔関連欠陥が消滅するというモデルでうまく説明できることを示した。さらに、この現象を定量的に解析する拡散方程式を導出し、その解を求めることで熱酸化による炭素空孔の消滅を定量的に予測できることを示した。

図 4 成長直後および熱酸化後の n 型 SiC 成長層の DLTS スペクトル. 熱酸化により全ての欠陥ピークが消滅.

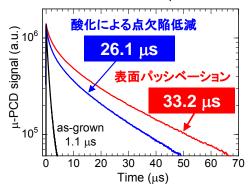

(10) 炭素原子の拡散を促進できる高温熱酸 化を用いることによって、厚さ約200µmのn 型SiC中の炭素空孔をほぼ完全に消滅させる ことに成功した。この結果、室温で33μs、200℃で47μsという最高のキャリア寿命を達成した(図5)。なお、酸化処理を施さない結晶のキャリア寿命は0.7~1μsである。

図 5 成長直後および熱酸化後の n型 SiC 成長層の光伝導度減衰曲線. 欠陥低減による大幅なキャリア寿命増大を達成.

(11) p型SiCにおいては、熱酸化による炭素空孔の消滅に加えて、高温(800℃以上)水素処理による残留点欠陥の不活性化が重要であることを見出した。この結果、p型SiCでも室温で10μs、200℃で31μsという長いキャリア寿命を達成した。水素処理による欠陥の不活性化の熱的安定性も調べ、600℃までは水素が脱離することなく、長いキャリア寿命を維持できることを明らかにした。

(12) 低エネルギー電子線照射と800-1000℃ の熱処理により、SiC結晶中に炭素空孔のみを 選択的に生成できることを見出した。生成した炭素空孔密度は、照射した電子線ドーズに ほぼ正比例することを示した。この結果を用いて、n型およびp型SiCにおけるキャリア寿命キラー欠陥を所望の密度で導入できる。この結果、n型およびp型SiCにおけるキャリア寿命制御(ライフタイムコントロール)を初めて実現した。

(13) SiC成長層のキャリア寿命測定時におけるキャリアの拡散と再結合を考慮したモデルを構築し、キャリア寿命測定時の諸問題を明らかにした。表面再結合の影響や下地基板における速いキャリア再結合が、測定される減衰カーブに大きな影響を与えることを定量的に示し、正確にキャリア寿命を求めるための指針を提示した。

(14) 5 kV級のSiC PiNダイオードを作製して、活性領域に存在する拡張欠陥がダイオードのリーク電流や耐圧に及ぼす影響を調べた。基底面転位、貫通らせん転位、貫通刃状転位が初期特性に与える影響は非常に小さいが、積層欠陥や積層欠陥を含む大型のエピ成長欠陥は、リーク電流の増

大や耐圧の低下に繋がることを明らかに した。

(15) シミュレーションと実験の両方のアプローチにより、10kV超級のSiC PiNダイオードやトランジスタの耐圧制限要因を調べた。この結果、絶縁膜/SiC界面に存在する高密度の表面電荷(エネルギー的に深い界面準位に捕獲されたキャリアを含む)が、デバイス端部における接合終端構造近傍における電荷バランスを崩し、電界集中を引き起こすことを明らかにした。

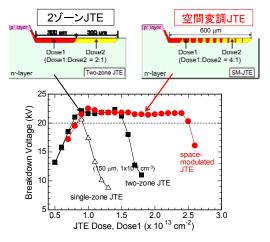

(16) 上記の問題を解決するために、実効的な空間電荷密度が、デバイス端部(外周端)に向かって緩やかに変化する理想的な電荷分布を実現する接合終端構造(改良型空間変調JTE)を考案した。この構造を有する20kV級PiNダイオードの耐圧特性を調べ、プロセス条件や動作温度が変化しても安定して超高耐圧が得られることを実証した(図6)。

図 6 2 ゾーン JTE および空間変調 JTE を有する SiC PiN ダイオードの耐圧の JTE ドーズ依存性. 空間変調 JTE により最適ドーズ範囲を大幅に拡大.

(17) 超高電圧動作時における表面放電を抑制するための表面保護膜を検討し、酸化膜とポリイミド厚膜の積層構造を用いることで、20kV以上の超高耐圧を得ることができることを明らかにした。また、このような超高耐圧デバイスにおいて、200℃までの良好な動作を確認し、温度上昇と共に耐圧が増加することから、アバランシェ破壊が支配的であることを示した。

(18) 上記の接合終端構造および表面保護を設けたデバイスでは、直流測定において10~20kVの耐圧近傍で降伏現象(漏れ電流の急増)が生じてもデバイスの物理的破壊や損傷は観測されず、アバランシェ耐性

が高いことが分かった。

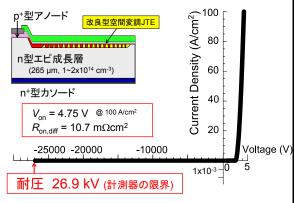

(19) 上述のSiCに適した独自の電界集中緩和構造を高純度SiC厚膜(265μm)に適用し、精密なデバイス設計技術、イオン注入技術、エッチング技術、電極形成技術を集約することで、いかなる固体素子で最高耐圧となる26.9kVのSiC PiNダイオードを実現した(図7)。

図7 高純度厚膜SiC成長層と空間変調 JTEを用いて作製したSiC PiNダイオー ドの電流一電圧特性. 26.9kV以上の耐圧 を達成.

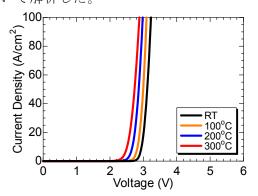

(20) 高温熱酸化による炭素空孔低減処理を施し、キャリア寿命を大幅に改善する技術を高耐圧PiNダイオードの作製に適用した。さらに電極材料や熱処理プロセスの改善によってオーミック電極の接触抵抗を低減することによって、 $10\sim20$ kV級SiCPiNダイオードのオン特性を著しく向上することに成功した。具体的には、電流密度100A/cm²時の微分オン抵抗を従来の約20m $\Omega$ cm²から2m $\Omega$ cm²以下に低減した( $10\sim15$ kV級デバイス)。オン特性の温度依存性も測定し、オン抵抗の温度依存性について解析した。

図8 キャリア寿命増大プロセスを活用して作製した13kV級SiC PiNダイオードの電流一電圧特性(温度依存性を含む).

(21) SiC トランジスタの一例として、npn 型バイポーラトランジスタに着目し、作製と特性解析を行った。キャリアのバルク再結合と表面再結合を抑制する構造およびプロセスを考案することにより、エミッタ接地電流増幅率を従来の70~100から250~430に増大することに成功した。なお、このトランジスタの耐圧は600V級である。

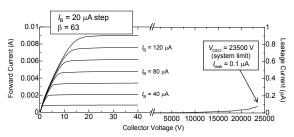

(22) 厚さ 180μm の高純度 n型 SiC 層をコレクタに用い、前述の空間変調型接合終端構造を設けることで、23kV の耐圧を有する SiC バイポーラトランジスタを実現した(図9)。これは半導体スイッチングデバイスとして最高の耐圧である。超高耐圧デバイスであるにも関わらず、電流増幅率は 63 と高い。

図 9 高純度厚膜 SiC コレクタ層と空間変調 JTE を用いて作製した高耐圧 SiC npn 型バイポーラトランジスタのコレクタ特性.

## 5. 主な発表論文等 〔雑誌論文〕(計 54 件)

(1) K. Kawahara, X. T. Trinh, N. T. Son, <u>J. Suda</u>, and <u>T. Kimoto</u>, "Investigation on origin of Z<sub>1/2</sub> center in SiC by deep level transient spectroscopy and electron paramagnetic resonance", Appl. Phys. Lett., 查読有, **102**, 112106/1-4 (2013).

DOI:10.1063/1.4796141

- (2) N. Kaji, H. Niwa, J. Suda, and <u>T. Kimoto</u>, "Ultrahigh-voltage SiC PiN diodes with an improved junction termination extension structure and enhanced carrier lifetime", Jpn. J. Appl. Phys., 查読有, **52**, 070204/1-4 (2013). DOI: 10.7567/JJAP.52.070204

- (3) T. Okuda, <u>T. Kimoto</u>, and <u>J. Suda</u>, "Improvement of carrier lifetimes in highly Al-doped p-type 4H-SiC epitaxial layers by hydrogen passivation", Appl. Phys. Express, 查読有, **6**, 121301/1-3 (2013). DOI:10.7567/APEX6.121301

- (4) H. Niwa, <u>J. Suda</u>, and <u>T. Kimoto</u>, "21.7 kV 4H-SiC diode with a space-modulated junction termination extension", Appl. Phys. Exp., 查読有, **5**, 064001/1-3 (2012). DOI:10.1143/APEX.5.064001

- (5) S. Ichikawa, K. Kawahara, <u>J. Suda</u>, and <u>T. Kimoto</u>, "Carrier recombination in n-type 4H-SiC epilayers with long carrier lifetimes", Appl. Phys. Exp., 查読有, **5**, 101301/1-3 (2012). DOI:10.1143/APEX5.101301

- (6) H. Miyake, T. Okuda, H. Niwa, <u>T. Kimoto</u>, and <u>J. Suda</u>, "21-kV SiC BJTs with space-modulated junction termination extension", IEEE Electron Device Lett., 查 読有, **33**, 1598-1600 (2012). DOI:10.1109/EDL.2012.2215004

- (7) K. Kawahara, <u>J. Suda</u>, and <u>T. Kimoto</u>, "Analytical model for reduction of deep levels in SiC by thermal oxidation", J. Appl. Phys., 查読有, **111**, 053710/1-9 (2012).

DOI: 10.1063/1.3692766

- (8) G. Feng, <u>J. Suda</u>, and <u>T. Kimoto</u>, "Nonradiative recombination at threading dislocations in 4H-SiC epilayers studied by micro-photoluminescence mapping", J. Appl. Phys., 查読有, **110**, 033525/1-5 (2011). DOI:10.1063/1.3622336

- (9) G. Feng, <u>J. Suda</u>, and <u>T. Kimoto</u>, "Space-modulated junction termination extension for ultrahigh-voltage p-i-n diodes in 4H-SiC", IEEE Trans. Electron Devices, 查読有, **59**, 414-418 (2012). DOI:10.1109/TED.2011.2175486

- (10) T. Hiyoshi, and <u>T. Kimoto</u>, "Reduction of deep levels and improvement of carrier lifetime in n-type 4H-SiC by thermal oxidation", Appl. Phys. Exp., 查読有, **2**, 041101/1-3 (2009).

DOI: 10.1143/APEX.2.041101

[学会発表] (計92件)

- (1) <u>T. Kimoto</u>, "Ultrahigh-voltage SiC devices for future power infrastructure" (plenary), Proc. of 43th Europ. Solid-State Device Research Conf. (Bucharest, 2013), A4L-E, p.22-29. 2013 年 9 月 16~20 日

- (2) T. Kimoto, K. Kawahara, H. Niwa, T. Okuda, and J. Suda, "Junction technology in SiC for high-voltage power devices" (plenary), Ext. Abstr. of IEEE 13th Int. Workshop on Junction Technology (Kyoto, 2013), p.54-57. 2013 年 6 月 6~7 日

- (3) <u>T. Kimoto</u>, <u>J. Suda</u>, G. Feng, H. Miyake, K. Kawahara, H. Niwa, S. Ichikawa, and <u>Y. Nishi</u>, "Defect electronics in SiC and fabrication of ultrahigh-voltage bipolar devices" (plenary), Electrochemical. Soc. Fall

Meeting 2012 (Honolulu, 2013), 2515. 2012 年 10 月 7~10 日

- (4) <u>T. Kimoto</u>, "SiC technologies for future energy electronics" (plenary), Tech. Digests of 2010 VLSI Technology Symp. (Honolulu, 2010), pp.9-14. 2010年6月14~16日

- (5) <u>T. Kimoto</u>, G. Feng, T. Hiyoshi, K. Kawahara, M. Noborio, and <u>J. Suda</u>, "Defect control in growth and processing of 4H-SiC for power device applications" (plenary), Int. Conf. on Silicon Carbide and Related Materials 2009 (Nürnberg, 2009), PL-1. 2009 年 10 月 11~15

[図書] (計3件)

(1) <u>T. Kimoto</u>, G. Feng, K. Danno, T. Hiyoshi and <u>J. Suda</u> "4H-SiC epitaxial growth and defect characterization", Silicon Carbide Epitaxy **4**, pp.121-144 (Publisher Research Signpost, 2012).

# [産業財産権]

○出願状況(計2件)

名称:半導体装置の製造方法および熱処理装

発明者:須田淳、奥田貴史、木本恒暢

権利者:京都大学

種類:特許

番号:特願 2013-143504 出願年月日:2013年7月9日

国内外の別: 国内

名称:半導体素子及び半導体素子の製造

発明者:木本恒暢、須田淳

権利者:京都大学

種類:特許

番号:特願 2011-059992

出願年月日:2011年3月18日

国内外の別: 国内

[その他]

ホームページ等

http://semicon.kuee.kyoto-u.ac.jp/

- 6. 研究組織

- (1) 研究代表者

木本 恒暢(KIMOTO Tsunenobu) 京都大学大学院・工学研究科・教授 研究者番号:80225078

(2) 研究分担者

須田 淳(SUDA Jun) 京都大学大学院・工学研究科・准教授 研究者番号: 00293887

西 佑介(NISHI Yusuke) 京都大学大学院・工学研究科・助教 研究者番号:10512759