# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成25年 5月20日現在

機関番号: 1 1 3 0 1 研究種目:基盤研究(B) 研究期間:2010~2012 課題番号:22300013

研究課題名(和文)3次元集積化新世代ベクトルマイクロアーキテクチャの創出

研究課題名 (英文) Innovative 3D Design for the New Generation Vector Microarchitecture

#### 研究代表者

小林 広明 (KOBAYASHI HIROAKI)

東北大学・サイバーサイエンスセンター・教授

研究者番号: 40205480

#### 研究成果の概要(和文):

本研究では、低消費電力・高性能な次世代ベクトルプロセッサを実現するために、新たなデバイス技術として注目を集めている 3 次元実装技術によるマイクロアーキテクチャ設計に取り組んだ。従来の 2 次元設計と 3 次元設計をハイブリッドに活用する上での設計指針を与え、演算回路やオンチップメモリなどユニット内配線レベルからユニット間配線レベルまで、2 次元配線の 3 次元 TSV (シリコン貫通ビア)による効果的な置き換えを実現した。そして、3 次元集積技術を活用して得られたプロセッサの有効性を性能評価により明らかにした。

### 研究成果の概要 (英文):

This study discusses a new design methodology for a microarchitecture of next-generation, low-power high-performance vector processors by using 3D die-stacking technology. A strategy for mixed design of conventional 2D design and TSV (Through-Silicon-Via)-based 3D design that realizes a good trade-off between them in the all level of on-chip units design has also been proposed. Through the performance evaluation of a prototyped 3D vector processor, the effectiveness of 3D design regarding power consumption and performance has been clarified.

#### 交付決定額

(金額単位:円)

|         | 直接経費         | 間接経費        | 合 計          |

|---------|--------------|-------------|--------------|

| 2010 年度 | 3, 800, 000  | 1, 140, 000 | 4, 940, 000  |

| 2011 年度 | 5, 100, 000  | 1, 530, 000 | 6, 630, 000  |

| 2012 年度 | 4, 900, 000  | 1, 470, 000 | 6, 370, 000  |

| 年度      |              |             |              |

| 年度      |              |             |              |

| 総計      | 13, 800, 000 | 4, 140, 000 | 17, 940, 000 |

研究分野:総合領域

科研費の分科・細目:情報学・計算機システム・ネットワーク

キーワード:計算機アーキテクチャ、3次元集積技術、ベクトルアーキテクチャ

# 1. 研究開始当初の背景

半導体微細化技術の進歩により、マイクロプロセッサの理論的性能の向上がはかられる一方,処理されるデータが格納されるオフチップメモリとプロセッサ間の接続技術は

チップのピン制限などから改善のスピード は遅く、多くのアプリケーションでメモリ性 能制約による実効性能の低下が深刻化して いる.併せて、大量の演算器やオンチップメ モリの実装により、それらのユニット内配線、 およびユニット間配線は、その量、および距離の増加が著しく、これによる伝送遅延、および消費電力の増加がプロセッサの設計制約にもなっている.

#### 2. 研究の目的

本研究の目的は、3次元貫通配線 LSI 積層技術を最大限に利用することにより、近い将来深刻化する高性能プロセッサ設計におけるメモリ制約問題とチップ内配線制約問題を緩和し、高メモリバンド幅アプリケーションに対して高い実効性能を達成する次世代ベクトルプロセッサアーキテクチャ実現のための要素技術を確立することである.

#### 3. 研究の方法

本研究では、高いメモリバンド幅により多くの実アプリケーションで高い実効性能を達成できるベクトルアーキテクチャに着目し、3年の研究期間内に3次元集積化時代を見据えたベクトルプロセッサ実現のためのマイクロアーキテクチャ設計に関して、以下の3つのポイントから研究を進めていく。

・ ベクトルプロセッサコア要素レベル 3 次 元マイクロアーキテクチャに関する研究

ベクトルプロセッサコアを構成する演算器、レジスタファイル、共有キャッシュなど基本構成要素である機能ユニットそれぞれの構成方式について、2次元層内、2次元層間の最適マイクロアーキテクチャ分割について性能-消費電力に関するトレードオフを明らかにし、コア要素レベルでのアーキテクチャ設計基礎を確立する。

・ ベクトルプロセッサコア要素間 3 次元マイクロアーキテクチャに関する研究

ベクトルプロセッサコアを構成する機能 ユニットの適切な3次元配置およびその接続 方式について、性能-消費電力に関するトレードオフを明らかにし、コア要素間レベルで のアーキテクチャ設計基礎を確立する。

・ ベクトルプロセッサコア間 3 次元マイクロアーキテクチャに関する研究

チップマルチコアやオンチップ共有・専有メモリ階層の3次元配置について、性能-消費電力に関するトレードオフを明らかにし、プロセッサレベルでのアーキテクチャ設計基礎を確立する。

# 4. 研究成果

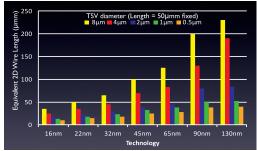

本研究では、先ず、チップ間をシリコン貫通配線 (TSV) で接続する 3 次元実装技術により、2 次元の平面配線によるチップ設計において、伝送遅延並びに消費電力がどの程度向上するかの評価を行った。図1は、チップ間を接続する様々な直径のTSVを仮定した際に、それと同等な通信遅延を有する2次元配

線がどの程度の長さになるかを、様々なテクノロジを想定して評価したものである。同図からわかるように、半導体技術の微細化により、想定する TSV と同等な 2 次元配線長が劇的に短くなり、その結果、より多くの 2 次元配線を TSV で置き換えることにより、チップ内の平均伝送遅延を向上させる可能性があることがわかった。

図1 TSV と等価な伝送遅延を 有する2次元配線長との関係

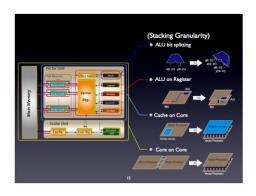

次に、マルチベクトルコアプロセッサ設計において、どのレベルで3次元実装技術が可能かの検討を行った。図2に示すように、本研究では、演算器やオンチップメモリ内配線にTSVを適用する最粒度レベルから、演算器やオンチップメモリ間、さらには演算コア間、ならびに演算コアとオンチップメモリ間をTSVで接続する粗粒度レベルまで、3次元実装技術を適用し、その効果を評価した。具体的には、3次元実装技術に基づくマルチベクト

図2プロセッサ設計における3次元実装技術の適用

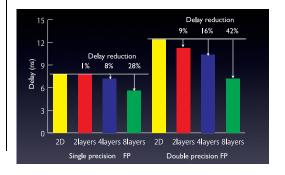

図3 3次元積層型乗算器の遅延評価

ルコアプロセッサの主要構成要素である,3次元演算器,3次元ベクトルキャッシュ,ならびに3次元マルチベクトルコアの基本設計を完了させた.

まず、演算器内配線レベルでの3次元実装技術の適用においては、単精度、および倍精度浮動小数点乗算器の設計を行った。本設計においては、サブ回路間TSV接続を仮定した場合に、ビット幅分割とサブ演算機能分割の両面で適切な回路分割を可能とする3次元回路分割戦略を新たに考案した。図3に設計した3次元乗算の評価結果を示す。乗算回路の3次元化により、クリティカルパス上の遅延を最大42%削減することに成功した。

また、3次元積層型キャッシュメモリ設計を既存の2次元設計用のEDAツールを用いて行った. 設計には 180nmCMOS テクノロジと様々な直径のTSVを用い、キャッシュを構成するサブキャッシュとコントローラを結ぶ

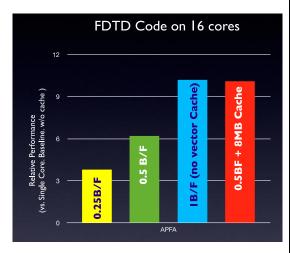

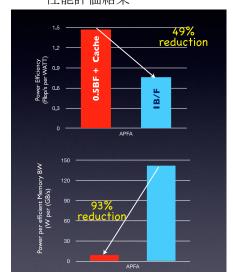

図4 3次元ベクトルプロセッサの 性能評価結果

図5 3次元ベクトルプロセッサの 消費電力評価結果

配線を TSV に置き換えるキャッシュ分割・積層法を検討した.評価の結果,3 次元積層型キャッシュメモリは,2 次元実装と比べて10,000um の長配配線数を49%,面積を99%削減するとともに,メモリバンド幅を最大で2倍に向上できることを明らかにした.

さらに,ベクトルマルチコア設計,および それらとオンチップキャッシュとの接続に TSV 接続を考慮した設計にも取り組み、その 有効性を東北大学サイバーサイエンスセン ターのスーパーコンピュータを利用してい るアプリケーション研究者の協力を得て評 価した. 図 4、図 5 に結果を示す. 図 4 は, 16 ベクトルコアを有するプロセッサのメモ リバンド幅を 0.25 から 1 B/F (B/F は演算性 能とメモリ性能の比を示す)まで変化させた 場合の実効性能と,16コアでメモリバンド幅 を半分にし、それを補うために 8MB のオンチ ップキャッシュを導入したチップの性能比 較を示す. 同図が示すように, 8MBのオンチ ップキャッシュを導入することにより、メモ リバンド幅を半分にしてもほぼ同等の実効 性能が得られていることがわかる. 図5は同 等の実効性能を達成する2つの設計において、 実効性能あたりの消費電力,並びにメモリ実 効転送率あたりの消費電力を比較したもの である.同図からわかるように、オンチップ キャッシュの導入により、演算あたりの消費 電力を 49%削減し、データ転送に関しては 93%の省電力の削減に成功している.

以上まとめると、3次元実装技術は次世代ベクトルプロセッサ設計において、高い実効性能を低消費電力で実現する上で必須の技術であり、本研究を通じて、そのための要素技術を明らかにできた.

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### [雑誌論文] (計 17 件)

- ① Ryusuke Egawa, Yusuke Endo, Jubee Tada, Hiroyuki Takizawa, Hiroaki Kobayashi, Exploring Design Space of a 3D Stacked Vector Cache, Proceedings of International Conference on High Performance Computing, Networking, Storage and Analysis (SC12), 査読有, 2012, USB (DOI: 10.1109/SC.Companion.2012.271).

- ② Ryusuke Egawa, Jubee Tada, Hiroaki Kobayashi, Exploring a Design Space of 3- D Stacked Vector Processors, Sustained Simulation Performance 2012, 査読無, 2012, 35-49 (DOI: 10.1007/978-3-642-32454-34).

- ③ Ye Gao, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, An out-of-order vector processing mechanism for multimedia applications, Proceedings of the 9th conference on Computing Frontiers (CF '12), 査読有 ,2012, 233-236 (DOI: 10.1145/2212908.221294).

- ④ Ye Gao, Naoki Shoji, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, A media-oriented vector architectural extension with a high bandwidth cache system, Cool Chips XV:15th IEEE International Symposium on Low-Power and High-Performance Processors, 査読有 , 2012, USB (DOI: 10.1109/COOLChips.2012.6216588).

- ⑤ Ryusuke Egawa, Yusuke Funaya, Ryu-ichi Nagaoka, Yusuke Endo, Akihiro Musa, Hiroyuki Takizawa and Hiroaki Kobayashi, Effects of 3-D Stacked Vector Cache on Energy Consumption, Proceedings of IEEE 3DIC 2012, 査読有, 2012, CD-ROM, (DOI: 10.1109/3DIC.2012.6263026).

- 6 Jubee Tada, Ryusuke Egawa, Kazushige Kawai, <u>Hiroaki Kobayashi</u> and Gensuke A Goto, Middle-Grain Circuit Partitioning Strategy for 3-D Integrated Floating-Point Multipliers, Proceedings of IEEE 3DIC 2012, 查読有, 2012, CD-ROM, (DOI:10. 1109/3DIC. 2012. 6263031).

- ⑦ Takashi Soga, Akihiro Musa, Koki Okabe, Kazuhiko Komatsu, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, Shun Takahashi, Daisuke Sasaki, and Kazuhiro Nakahashi, Performance of SOR Methods on Modern Vector and Scalar Processors, Computers & Fluid, 査読有, 45 巻 , 2011, 215-221 (DOI:10.1016/j.compfluid.2010.12.024

- Kazuhiko Komatsu, Takashi Soga, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, Shun Takahashi, Daisuke Sasaki, and Kazuhiko Nakahashi, Processing of Parallel the Building-Cube Method on the GPU Platform, Computers & Fluid, 查読有, 巻 , 2011, 122-128 (DOI:

- 10.1016/j.compfluid.2010.12.019).

- ⑨ 佐藤義永,撫佐昭裕,江川隆輔,滝沢寛 之,岡部公起,小林広明,チップマルチ ベクトルプロセッサのためのプログラム 最適化技術,東北大学サイバーサイエン スセンター 大規模科学計算システム広 報誌 SENAC,査読無,44巻,2011,29-36.

- ⑩ 河井一茂,多田十兵衛,江川隆輔,小林 広明,後藤源助,3次元積層型浮動小数 点器の回路分割手法に関する研究,信学 技報(ICD2011-94),査読無,111巻,2011, 67-72.

- ① Yoshiei Sato, Akihiro Musa, Ryusuke Egawa, Hiroyuki Takizawa, Koki Okabe, Hiroaki Kobayashi, Performance and Scalability Analysis of a Chip Multi Vector Processor, High Performance Computing on Vector Systems 2011, 查読無, 2011, 3-20 (DOI:10.1007/978-3-642-22244-3\_1).

- ① 佐藤義永,永岡龍一,撫佐昭裕,<u>江川隆</u><u>輔</u>,<u>滝沢寛之</u>,岡部公起,<u>小林広明</u>,ルーフラインモデルに基づくベクトルプロセッサ向けプログラム最適化戦略,IPSJ Transactions on Advanced Computing Systems,査読有,4巻,2011,1-11.

- (3) Masayuki Sato, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, A Majority-based Control Scheme for Way-Adaptable Caches, Lecture Notes in Computer Science, 查読有, 2011, 16-28, (DOI: 10.1007/978-3-642-16233-6\_5).

- Masayuki Sato, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, A Voting-Based Working Set Assessment Scheme for Dynamic Cache Resizing Mechanisms, Proceedings of IEEE International Conference on Computer Design 2010, 查読有, 2010, 98 - 105, "DOI: 10.1109/ICCD.2010.5647599".

- (5) Ye Gao, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, A Load-Forwarding Mechanism for the Vector Architecture in Multimedia Applications, Proceedings of Euromicro Conference on Digital System Design (DSD 2010), 查読有, 2010, 412-415, (DOI:10.1109/DSD.2010.93).

- 16 Yusuke Funaya, Ryusuke Egawa, Hiroyuki

- Takizawa,<br/>PartitioningHiroaki<br/>StrategiesKobayashi,<br/>forCache<br/>3-DStackedVectorProcessors,ProceedingsofIEEE3DSystemIntegrationConference2010,查読有,2010,CD-ROM,(DOI:10.1109/3DIC.2010.5751453).

- (Ī) Ryusuke Egawa, Yusuke Funaya, Ryuichi Nagaoka, Akihiro Musa, Hiroyuki Takizawa, Hiroaki Kobayashi, Design and Early Evaluation of 3-D Die Stacked Chip Multi-Vector Processors, Proceedings of IEEE 3D System Integration Conference 2010, 查読有, 2010, CD-ROM, (D0I: 10.1109/3DIC.2010.5751453).

# 〔学会発表〕(計24件)

- ① <u>Hiroaki Kobayashi</u>, Potentials of the vector architecture in the post-peta era, 16th Workshop on Sustained Simulation Performance (招待講演), 2012年12月10日, ドイツシュットガルト市.

- ② <u>Hiroaki Kobayashi</u>, Design Space Exploration of the Vector Processor Architecture using 3D Die- Stacking Technology, 筑波大学計算科学研究センター設立 20 周年記念シンポジウム(招待講演), 2012年09月07日, つくば市

- ③ <u>Hiroaki Kobayashi</u>, High- End Computing Systems: Past, Present and Future, SICE2012 (招待講演), 2012年08月20日, 秋田市.

- ④ <u>Hiroaki Kobayashi</u>, Capability and Potential of Vector Processors: Present and Future, NUG2012 (招待講演), 2012 年 06 月 12 日, ドイツポツダム.

- ⑤ <u>Hiroaki Kobayashi</u>, Capability of Vector-Parallel Computing Platforms, ATIP HPC Workshop in Singapore (招待講演), 2012年05月07日,シンガポール.

- Ryusuke Egawa, Yusuke Endo, Jubee Tada, Hiroyuki Takizawa, Gensuke Goto, and Hiroaki Kobayashi, Designing a 3D stacked Vector Cache, DATE 2012 Workshop on 3D Integration Application, Technology , Architecture, Automation and Tests, Mar. 16 2012, Dresden, Germany.

- ⑦ 千葉雄太,遠藤裕亮,船矢祐介,<u>江川隆</u><u>輔</u>,<u>滝沢寛之</u>,小林広明,3次元積層技術を用いた倍精度浮動小数点加算回路設計に関する一考察,情報処理学会東北支部研究報告会,2012年3月2日,仙台市.

- ⑧ 佐藤義永,永岡龍一,撫佐昭裕,江川隆 輔,滝沢寛之,岡部公起,小林広明,キ ャッシュ機構を有するベクトルアーキテ クチャのためのプログラム最適化戦略, 第10回情報シナジー研究会,2012年2月 27日,東北大学.

- Ryusuke Egawa, Yusuke Funaya, Ryuichi Nagaoka, Akihiro Musa, Hiroyuki Takizawa, Hiroaki Kobayashi, Effects of 3-D Stacked Vector Cache on Energy Consumption, Facing the multicore challenge II, Sep. 29 2011, Karlsruhe, Germany.

- ① <u>Hiroaki Kobayashi</u>, 3D Vector Processor for Highly-Productive Extreme-Scale Computing, NUG2011 (招待講演), June 8, 2011, Prague, Czech Republic.

- ② 永岡龍一,佐藤義永,撫佐昭裕,<u>江川隆</u><u>輔</u>,<u>滝沢寛之</u>,小林広明,実アプリケーションを用いたチップマルチベクトルプロセッサの消費エネルギ評価,東北大学シナジー研究会,2011年2月18日,東北大学.

- (3) 佐藤義永,永岡龍一,撫佐昭裕,<u>江川隆</u>輔,<u>滝沢寛之</u>,岡部公起,<u>小林広明</u>,ルーフラインモデルに基づくベクトルプロセッサ向けプログラム最適化戦略,2011年ハイパフォーマンスコンピューティングと計算科学シンポジウム(HPCS2011),2011年1月19日,つくば市.

- ④ 佐藤義永, 撫佐昭裕, <u>江川隆輔</u>, <u>滝沢寛</u> <u>之</u>, 岡部公起, <u>小林広明</u>, 次世代ベクトルプロセッサ向けプログラム最適化戦略, 次世代スーパーコンピューティングシンポジウム 2010, 2011 年 1 月 17 日, 神戸市

- ⑤ 坂井 一仁,多田 十兵衛,<u>江川 隆輔</u>, 小林 広明,後藤 源助,3 次元積層型乗

算器の回路分割手法に関する研究, ICD 研究会, 2010年12日16日, 東京.

- ⑩ 永岡龍一,佐藤義永,撫佐昭裕,<u>江川隆</u>輔,<u>滝沢寛之</u>,小林広明,実アプリケーションを用いたチップマルチベクトルプロセッサの消費エネルギ評価,ハイパフォーマンスコンピューティングとアーキテクチャの評価に関する北海道ワークショップ(HOKKE-18),2010年12月15日,札幌.

- ① 小林広明,高生産・高性能コンピューティングと新世代ベクトルコンピューティングに関する R&D, SP 研究会 SC10 講演会(招待講演), November 17, 2010, New Orleans, LA, USA.

- Woshiei Sato, Ryuichi Nagaoka, Akihiro Musa, Ryusuke Egawa, Hiroyuki Takizawa, Koki Okabe Hiroaki Kobayashi, A Performance Tuning Strategy under Combining Loop Transformations for a Vector Processor with an On-Chip Cache, ACM/IEEE SC2010 conference, November 16, 2010, New Orleans, LA, USA.

- ⑪ <u>Hiroaki Kobayashi</u>, Activities for Highly-Productive Computing and R&D on New-Generation Vector Computing, JAEA SC10 Workshop(招待講演), November 16, 2010, New Orleans, LA, USA.

- Miroaki Kobayashi, Performance Discussion on Scalar and Vector Systems and R&D on New-Generation Vector Computing, 13th Teraflop Workshop, October 21-22, 2010, Sendai, Japan.

- ② 多田十兵衛,<u>江川隆輔</u>,坂井一仁,<u>小林</u> <u>広明</u>,後藤源助,3次元積層技術を用い た乗算回路設計に関する研究,再生可能 集積システム時限研究会,2010年10月 15日,横浜.

- ② <u>Hiroaki Kobayashi</u>, Performance Discussion on Scalar and Vector Systems and R&D for New-Generation Vector Computing at Tohoku University, NUG-XXII(招待講演), June 30, 2010, Toulouse, France.

- Kazuhiko Komatsu, Takashi Soga, <u>Ryusuke Egawa</u>, <u>Hiroyuki Takizawa</u>, <u>Hiroaki Kobayashi</u>, Shun Takahashi, Daisuke Sasaki, Kazuhiro Nakahashi,

Efficient Data Management for the Building Cube Method using Cartesian Meshes on the GPU Platform, International Supercomputing Conference '10, June 01-02, 2010, Hamburg, Germany.

② Takashi Soga, Akihiro Musa, Youichi Shimomura, Ken'ichi Itakura, Koki Okabe, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi, Performance Evaluation of NEC SX-9 using Real Science and Engineering Applications, SACSIS 2010, 2010 年 5 月 28 日,奈良県.

### [図書] (計3件)

- ① M. Resch, X. Wang, E. Focht, <u>H. Kobayashi</u>, S. Roller(Ed.), Sustained Simulation Performance, Springer, 2012, 1-194

- ② M. Resch, X. Wang, E. Focht, <u>H. Kobayashi</u>, S. Roller(Ed.), High Performance Computing on Vector Systems 2011, Springer, 2012, 1-260.

- ③ M. Resch, S. Roller, K. Benkert, M. Galle, W. Bez, <u>H. Kobayashi</u> (Ed.), High Performance Computing on Vector Systems 2011, Springer, 2011, 1-250.

[その他]

ホームページ等

http://www.sc.isc.tohoku.ac.jp/

- 6. 研究組織

- (1)研究代表者

小林 広明 (KOBAYASHI HIROAKI) 東北大学・サイバーサイエンスセンタ ー・教授

研究者番号: 40205480

(2)連携研究者

滝沢 寛之 (TAKIZAWA HIROYUKI) 東北大学・大学院情報科学研究科・准教 授

研究者番号:70323996

江川 隆輔 (EGAWA RYUSUKE) 東北大学・サイバーサイエンスセンタ ー・助教

研究者番号:80374990