# 科学研究費助成事業 研究成果報告書

平成 26 年 6 月 6 日現在

機関番号: 62615 研究種目: 若手研究(B) 研究期間: 2010~2013 課題番号: 22700061

研究課題名(和文)メニーコア計算機プラットフォームのためのチップ内ネットワークの省電力化

研究課題名(英文)Low Power Techniques of Network-on-Chips for Many-core Computer Platforms

#### 研究代表者

鯉渕 道紘 (Koibuchi, Michihiro)

国立情報学研究所・アーキテクチャ科学研究系・准教授

研究者番号:40413926

交付決定額(研究期間全体):(直接経費) 2,500,000円、(間接経費) 750,000円

研究成果の概要(和文):本研究では,携帯端末,高性能計算などの IT機器の基盤となっているメニーコアプロセッサ・計算機プラットフォームにおけるチップ内ネットワークの革新的な動的電力最適化技術と関連する低遅延通信技術の実現を目的として行った.成果として,(1)トラフィック負荷に応じて動作周波数とパイプライン構成(1段から4段)を切り替えることが可能な省電力オンチップルータ,(2) その動的再構成方法,(3) 配線密度,および各配線長を一定(具体的にはマンハッタン距離で6コア長)以下に抑える制限を課したランダムルータ間トポロジを各々提案し,フルシステムシミュレーション,電力面の評価から有効性の提示を行った.

研究成果の概要(英文): In this study our objective is to present innovative dynamic low-power and low-lat ency techniques of network-on-chips for many-core processor platforms that form IT equipments, such as mobile terminals and high-performance computers. Our main solutions are (1) low-power variable pipeline-and-frequency on-chip routers (1 cycle to 4 cycles) optimized to traffic load, (2) its dynamic reconfiguration techniques and (3) random topology design of routers whose link length is limited within 6 core logical length. Their efficiency is confirmed via full-system simulation and power estimation.

研究分野: 総合領域

科研費の分科・細目: 情報学・計算機システム・ネットワーク

キーワード: ネットワークオンチップ 低消費電力技術 システムオンチップ 相互結合網 メニーコア

## 1.研究開始当初の背景

半導体技術の進歩によって,単一チップ上 にプロセッサ, メモリ, I/O などの複数の設 計モジュールをタイル状に実装したマルチ コア,メニーコアプロセッサが登場し,これ らのプロセッサシステムは計算機プラット フォームとしての主流となりつつある. 例え ば,2007年,インテルは80コアのシングル チップを開発し、スーパーコンピューターに 匹敵する TFlops(1 秒当り1兆回以上の演算 速度)性能のチップを発表した .従来のプロセ ッサ研究はスーパースカラ,アウトオブオー ダ命令実行等のマイクロアーキテクチャに 関連するものが多かったが,現在,コアの相 互結合方式,通信機構といった課題が極めて 重要になってきている.つまり,研究代表者 の鯉渕の 2006 年頃の研究テーマである PC クラスタ,並列計算機などの計算機間の通信 の課題が、シングルチップ上のコア間通信と いうマイクロシステムの課題へと広がりを 見せている、情報家電などの組み込み機器で 使われるシステムオンチップ(SoC)の分野に おいても, 実装可能なモジュール数が飛躍的 に増加しているため,同様の課題が生じてい る.

現在、半導体の集積度の向上により、実システムのチップ内ネットワークにおける課題はハードウェア量や遅延から、動的と静的な)消費電力の削減に移行しつつある.例えばMIT Raw CMP ではネットワークがチップの全消費電力の4割を消費している.しかし、プロセッサコアの省電力化が進んでいることと対称的に、全コアから共有されているネットワークは電力を落とすタイミングが難しく、省電力に関する研究が進んでいないのが現状である.

ネットワーク低消費電力技術は,性能(スループットと遅延)とのトレードオフであるため既存の1つの要素技術のみで解決できる単純なものではなく,各要素技術の組み合わせ,クロスレイヤによるマッシュアップ的なシステムアーキテクチャとして取り組むことが効果的である.そこで,これまでの研究成果を消費電力の削減のために応用して,次節に述べる革新的な電力最適化技術をアーキテクチャレベルで実現することが重要という結論に至った.

#### 2.研究の目的

本研究では、携帯端末、高性能計算機、ゲーム機などのIT機器の基盤となっているメニーコアプロセッサ・シングルチップ計算機プラットフォームにおけるチップ内ネットワークの革新的な動的電力最適化技術を実現することを目的とする.そのために、(1)動的な電力制御である Dynamically Voltage and Frequency Scaling (DVFS)と On/Offリンクアクティベーション制御を活用し、かつパケットのバッファリングリング処理を1

~ 2回に激減する超低消費電力ルータアーキテクチャ,トポロジ,ルーティングを提案し,これを基に(2)メニーコアプロセッサのキャッシュコヒーレンスに最適化したトポロジの動的再構成による省電力技術を提案,評価する.

#### 3.研究の方法

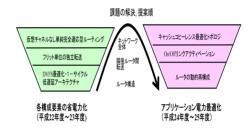

省電力チップ内ネットワークを効率良く順序立てて実現するために,ルータなどの構成要素の省電力技術の確立と,その構成要素を統合したアプリケーション最適化の2つに分類し,順に行うことで最終的にチップ内ネットワーク全体での電力性能向上を達成する(図1).

図 1: 研究概要

#### (1) 平成 22 年度

, 初年度は,まず,要素の構成技術として ルータアーキテクチャの改良を行う.チップ 内ネットワークはパケットをパイプライン 処理するルータを多数用いることで , 高スケ ーラビリティ , 高スループットを実現してい る. そこで, トラフィック負荷に応じて動作 周波数とパイプライン構成を切り替えるこ とが可能な省電力オンチップルータを提案 する. 各動作周波数におけるパイプラインス テージあたりの処理量を大きくするために、 低い動作周波数ではパイプライン段数を浅 くする.これを,単純なカスケーディングに よるパイプラインステージの統合ではなく、 各ステージ処理の並列性を最大限に利用す る投機実行によって実現し,かつ最小限の遅 延でパイプライン構造を再構成する技術を 実現することを目標とした.

さらに,バンド幅要求が低い並列アプリケーションにおいて 1ーサイクルでルータ内をパケット転送することでバッファリングイプライン構造との動的な統合を1つのルータ上で実現する.これらは,既に耐故障性の向上,性能向上のために申請者が行ってきた料研費(スタートアップ,若手 B)の支援に電力、関したチップ内ネットワーク技術を電力制減(例えば,故障箇所迂回技術を電別フにしたリンクの迂回ルーティングに活用)に応用することで,本研究課題の基礎を確実に進められるように配慮した.

なお,シミュレーションにおいて,万が一, 計算機の計算能力が不足した場合,あるいは, 開発が遅れた場合には,待ち行列理論,マル コフモデルを用いてルータとネットワークの性能を解析し、性能要因を確認し、かつ提案要素技術にフィードバックする.既存の多くの研究がマクロシステムの評価にシミュレーションのみを用いた総合評価を行っているが、本研究では理論的にも性能要因を特定するように工夫を行った.

次に,ルーティングラベルを効率良く活用し,フリット毎に独立した経路で転送するデータ転送方式を用いることでパケット・デッドロックの発生するパターンを削減する.そして,デッドロック条件の静的解析から最終的に,仮想チャネルを用いることなく完全適応型デッドロックフリールーティングを実現する.

また,効果的に研究を進めるために,各段階で解決困難な問題が生じた場合,性能面などでは劣るが既存のデッドロックフリールーティング,最短経路のみを用いるライブロック除去法などを適用することで,本提案手法の全体像,枠組を示すことができるように工夫した.

## (2)平成 23、24 年度

1 年目に確立した技術を発展させ,モデル 化した上で,3年目終了時までにアプリケー ションのトラフィックパターン(アクセスパ ターン,転送量)に応じて最適化する.様々 なケースを想定した検証,評価を行うため, 大容量ハードディスクを含めて最新の計算 機環境が必要となる、そして、既存の低遅延 技術との比較をスループット,パケット遅延, ハードウェア量,電力の4点において総合的 に行う.これらはチップ内ネットワークの評 価指標として使われている妥当なものであ る. さらに, 具体的な応用例として, インテ ル 80 コアプロセッサ, TRIPS EDGE, SCE/東 芝/IBM Cell ブロードバンドエンジンなどの チップ内ネットワークを持つ実システムを 想定した本提案手法の適用方法についても 明らかにすることを目標とした.

最近のマルチコアプロセッサでは,プログラミングの容易さなどコヒーレントなキャッシュの重要性が認識され,Tilera 社 Tile64などコヒーレントキャッシュを装備するシステムが増えている.そこで,3年目にはキャッシュコヒーレントをブロードキャストの有無とパケットの到着順保障の必要性の観点で分類し,各々に適したトポロジとルーティングを示すことにした.

なお,随時得られた定量的な知見に基づき,研究会,国際会議,論文誌などへの論文執筆を行った.

チップ内ネットワークのアーキテクチャの性能要因であるルータ構造,ルータ間データ転送方式,ルーティングに関してアプリケーション,キャッシュコヒーレンスに対して電力最適化するという多岐に及ぶ課題を図2に示した順に従い実現するために4年という研究期間を設定した.

本研究課題は,従来の PC クラスタ,並列計 算機などのシステムレベルの研究領域をマイクロシステムに広げる点で視野をより一 層広くするものである.

よって,本研究課題は,研究代表者がこれまで行ってきた相互結合網,並列処理,計算機アーキテクチャの知見を,各要素技術として利用,融合できる点で,研究代表者の能力を最大限に生かすことができたものといえる。

## 4. 研究成果

主な研究成果を順に述べる.

まず,チップ内ネットワークの要素の構成 技術として、ルータアーキテクチャの改良を 行った.チップ内ネットワークはパケットを パイプライン処理するルータを多数用いる ことで, 高スケーラビリティ, 高スループッ トを実現している、そこで、トラフィック負 荷に応じて動作周波数とパイプライン構成 を切り替えることが可能な省電力オンチッ プルータを提案、拡張した. 各動作周波数に おけるパイプラインステージあたりの処理 量を大きくするために,低い動作周波数では パイプライン段数を3段から2段、あるいは 1段と浅くする.これを,単純なカスケーデ ィングによるパイプラインステージの統合 ではなく,各ステージ処理の並列性を最大限 に利用する投機実行によって実現し,かつ最 小限の遅延でパイプライン構造を再構成す る技術を実現した.

次に,バンド幅要求が低い並列アプリケーションにおいて 1ーサイクルでルータ内をパケット転送することでバッファリング回数を削減し,かつ,再構成技術により,パイプライン構造との動的な統合を1つのルータ上で実現した.以上より、動的電力最適化技術を実現するための要素技術について提案を行い、スループット、動作周波数に関する部分的な評価を行うことができた。

また、結合網のトポロジにランダム性を取 り入れることで遅延を最小化する方式を提 案し、その結果コア間通信遅延をネットワー クレベルで大幅に削減できる見通しを示し た。さらに、End-to-end 通信遅延を削減す るために、規則的なルータ間トポロジに対し、 複数リンクを単一コアとランダムに選択し た複数ルータに接続する方法を提案した。フ リットレベルのネットワークシミュレーシ ョンの結果、ランダムコアリンクを用いた本 トポロジは従来のトポロジに比べ、平均遅延 を最大 27%減少させることに成功した。さら に、チップ内ネットワークの実装をふまえて、 配線密度、および核配線長を一定以下に抑え る制限を課したランダムトポロジを追求し た。その結果、このランダムコアリンクはマ ンハッタン距離で6コア長以内という制約を 課してもほぼ同等の性能が得られることが 分かった。

最後に、チップ内ネットワークのルータの

消費電力がポート数に支配される点に注目してトポロジの最適化を行い、3次元チップ内ネットワークを含めた影響を調査した。その結果、ランダムリンクを用いたトポロジは電力面でも極めて有望であることが分かった。これらは既存のチップ内ネットワークに適用するために特別なデバイスや実装技術を必要とせず、現実的なチップ内ネットワークの低消費電力技術と関連する低遅延技術を提案し、その有効性を定量的に示すことができた。

# 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文](計 6 件)

- (1)河野 隆太, 藤原 一毅. 松谷 宏紀, 天野 英晴, <u>鯉渕 道紘</u>, ホストから複数リンクを 用いた低遅延ネットワークトポロジ, 電子情報通信学会技術研究報告 CPSY2012-77, Vol.112, No.376, pp.123-128, Jan 2013.(査 読無)

- (2)佐々木大輔, 松谷宏紀, <u>鯉渕道紘</u>, 天野 英晴, 3 次元 NoC の混在トポロジにおけるル ーティング手法の提案,電子情報通信学会技 術研究報告 CPSY2012-2, pp.7-12, Apr 2012 (査読無)

- (3)中村 武雄, 松谷 宏紀, <u>鯉渕 道紘</u>, 宇佐美 公良, 天野 英晴, 多電源可変パイプラインルータを用いた細粒度な電源制御, 情報処理学会研究報告計算機アーキテクチャ(ARC),2012-ARC-200, No.15, pp.1-8, May 2012(査読無)

- (4)<u>鯉渕 道紘</u>, 松谷 宏紀, 天野 英晴, D. Frank Hsu, Henri Casanova, 高性能計算機 インターコネクトにおけるランダムショートカットトポロジ, 2012 年ハイパフォーマンスコンピューティングと計算科学シンポジウム (HPCS2012), 論文集, pp.85-92, Jan 2012(査読有)

- (5)Yuto Hirata, Hiroki Matsutani, Michihiro Koibuchi, Hideharu Amano, A Variable-pipeline On-chip Router Optimized to Traffic Pattern, Proc. of the 3rd International Workshop on Network on Chip Architectures (NoCArc'10), pp.57-62, Dec 2010 (査読有)

DOI: 10.1145/1921249.1921263

(6) 西川 由理, <u>鯉渕 道紘</u>, 松谷 宏紀, 天野 英晴, 単フリット・単サイクルルータを用いた NoC 向け非最短完全適応型ルー ティン グ, 情報処理学会論文誌コンピューティングシステム, Vol.3, No.3, pp.88-99, Sep 2010(査読有)

[学会発表](計 1 件)

(1)<u>鯉渕 道紘</u>, HPC インターコネクトのためのランダムトポロジ,2012年12月21日(東北大学,情報処理学会東北支部講演会)(招待講演)

[図書](計 0 件)

[産業財産権]

出願状況(計 0 件)

取得状況(計 0件)

#### [その他]

「メニーコア、マルチコアなどのシングルチップ高性能コンピューティング環境における超省電力・低遅延・スケーラブルなチップ内ネットワーク(NoC) (鯉渕研究室)」http://research.nii.ac.jp/~koibuchi/research03.html

## 6. 研究組織

(1)研究代表者

鯉渕 道紘 (KOIBUCHI Michihiro) 国立情報学研究所・アーキテクチャ科学研 究系・准教授

研究者番号: 40413926

(2)研究分担者

0名

(3)連携研究者

0名